使用版本:AD18

Altium Designer(一)——新建工程以及小技巧

Altium Designer(三)——PCB的绘制

Altium Designer(四)——PCB规则设置

Altium Designer(五)——铺铜和电器规则检查

推荐一个B站的UP主的视频,感觉很不错呀:https://www.bilibili.com/video/BV17E411x7dR?p=1 系列视频

文章目录

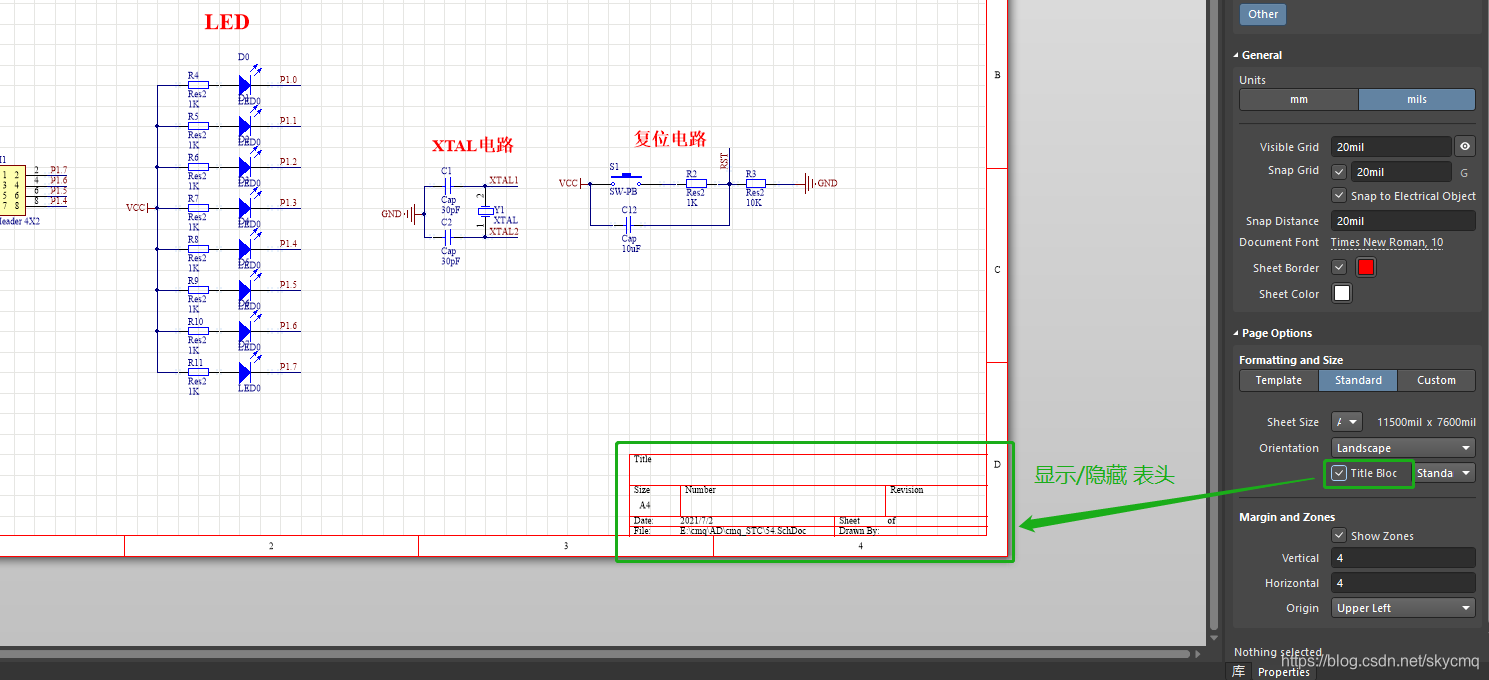

打开SchDoc文件之后,在外边的空白区域左键,可设置 栅格点以及 纸张的大小、 颜色等。

- 是否隐藏表头

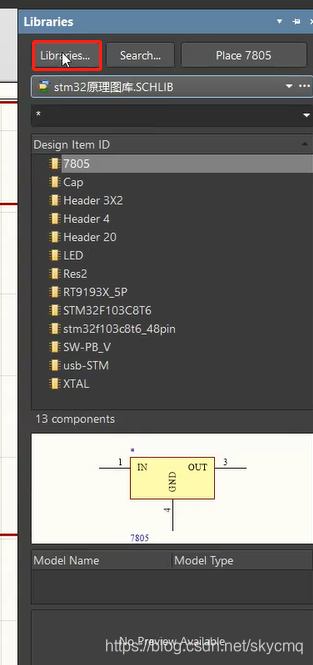

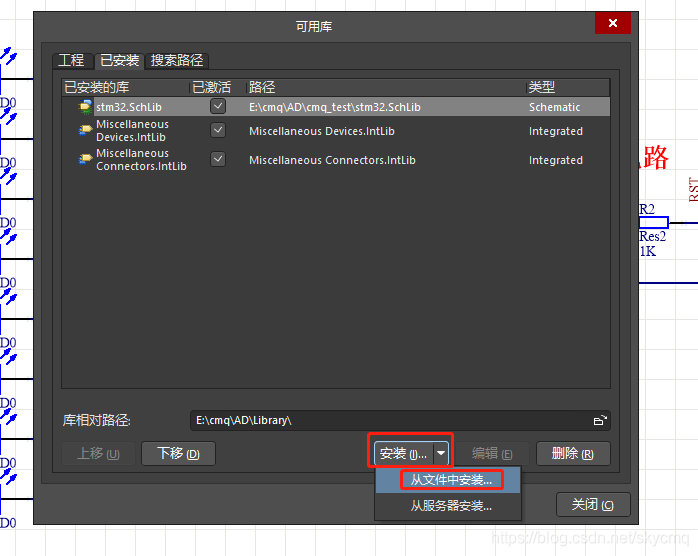

- 添加自己的库

找到需要的LIB后缀的库,选中添加即可,ESC/右键 取消继续添加。

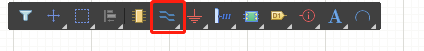

- 画具有电气连接属性的线

法一:点击“放置线”的图标

法二:Ctrl + W

放置线的时候,空格可以改变角度

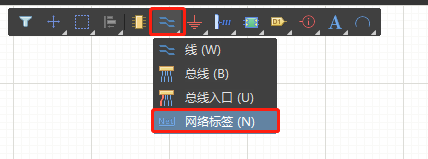

- 放置网络标签

同一个网络标签代表的两条线代表连接到了一起。

还没有放置的时候,按Tab键修改属性,ESC/右键结束当前放置

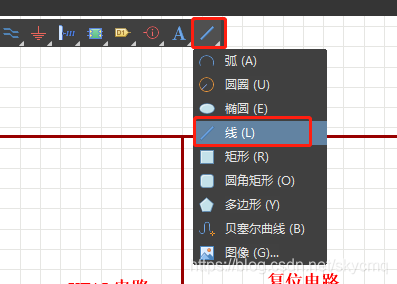

- 画框框

画框框以区分不同的区域

同理,Tab键修改属性(颜色、粗细等),右键结束当前操作

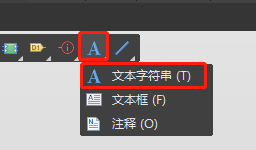

- 添加字符文本

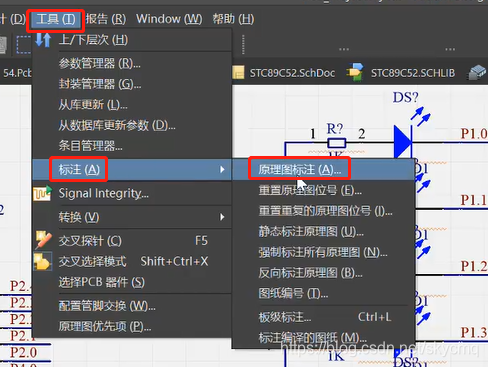

- 给相同的器件添加编号(标号)

法一:

法二:

-

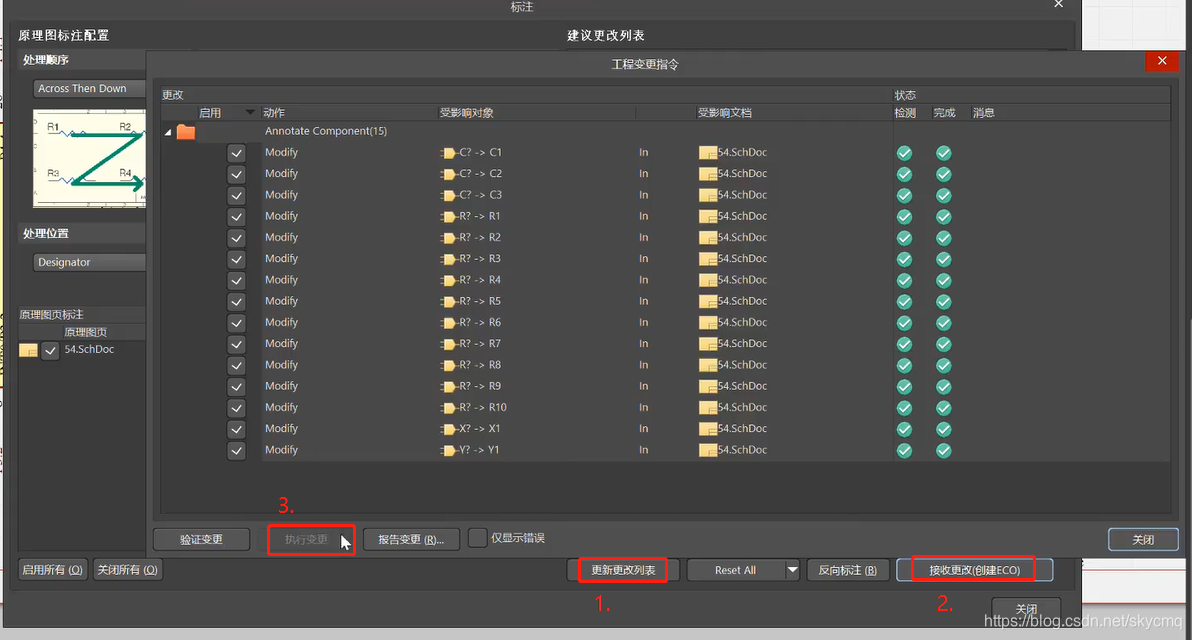

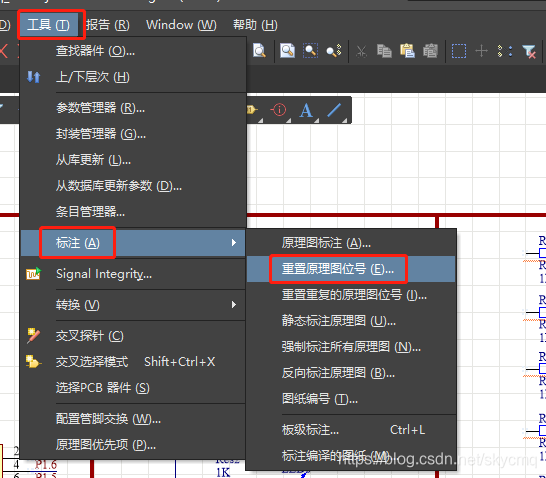

先reset,把所有标号都去掉

-

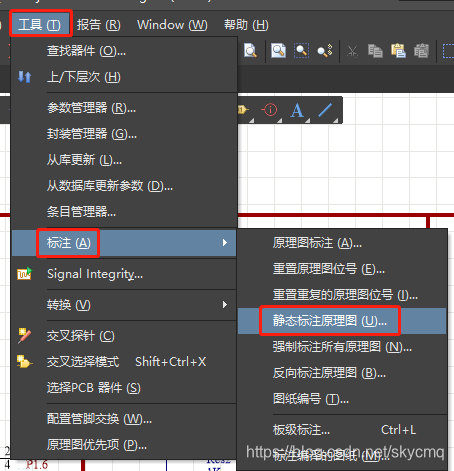

静态标注原理图

- 添加封装

法一:

在SchDoc中双击器件,然后在右侧的Footprint里添加相应的封装。

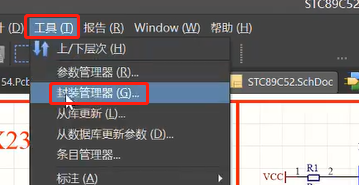

法二:批量封装

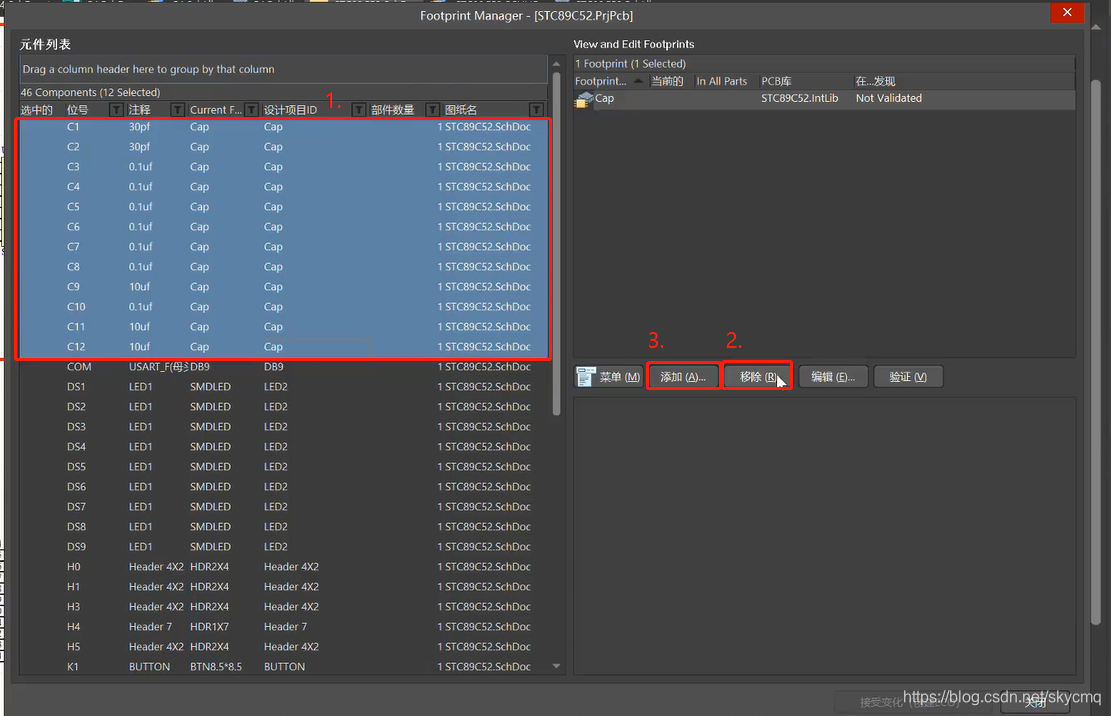

工具——封装管理器(快捷键:T+G)

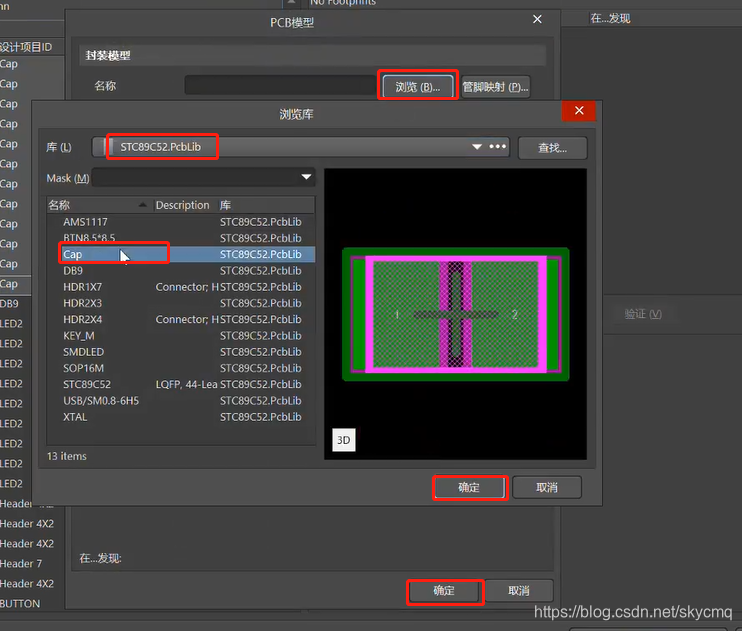

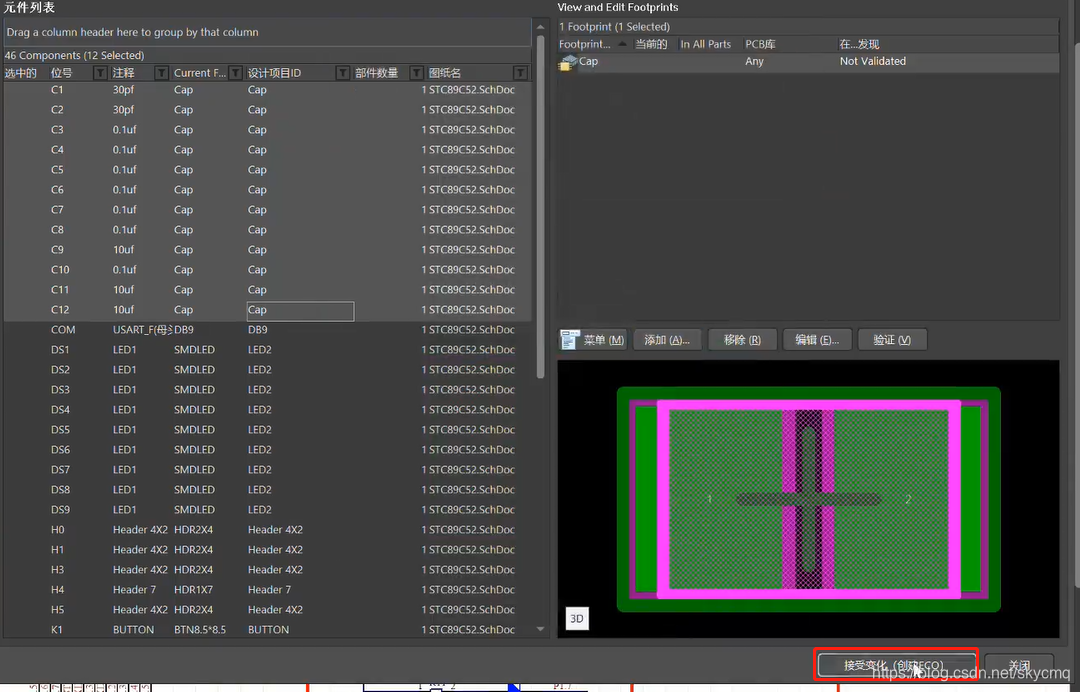

以Cap为例,选中所有的Cap,移除再添加

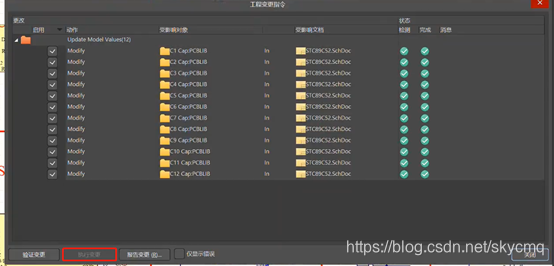

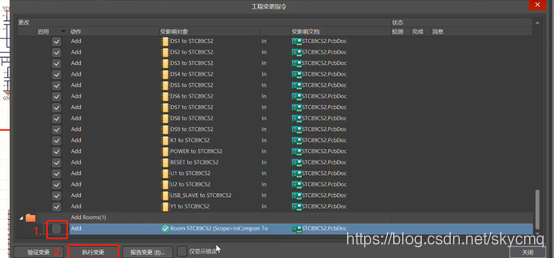

执行变更:

- 检查是否所有器件都有封装

法一:利用封装管理器(T+G)查看

法二:

点击“验证变更“:

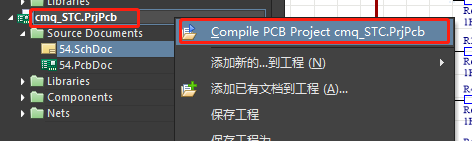

- 编译

右击自己的工程—Compile PCB

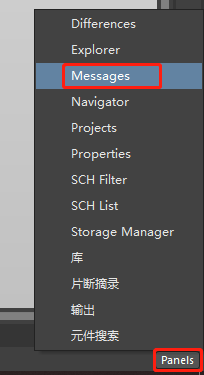

点击右下角的 “Panels“——”Messages“查看编译结果,绿色即为没有问题

在原理图界面右键→工程选项→错误报告,界面选择修改off grid object 的报告格式为不报告,则此类型错误在下次编译时不会产生报告。

- 原理图导入PCB

(确保已经新建了PCB文件之后)

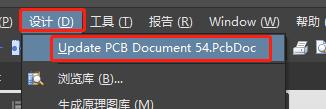

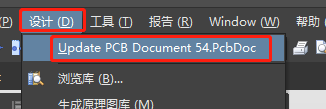

法一:

在SchDoc里边操作,设计—Update PCB Document

把Room前的对勾去掉

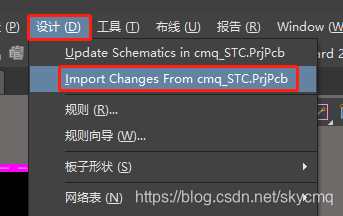

法二:

在PcbDoc里边操作

1447

1447

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?