verilog基础语法练习

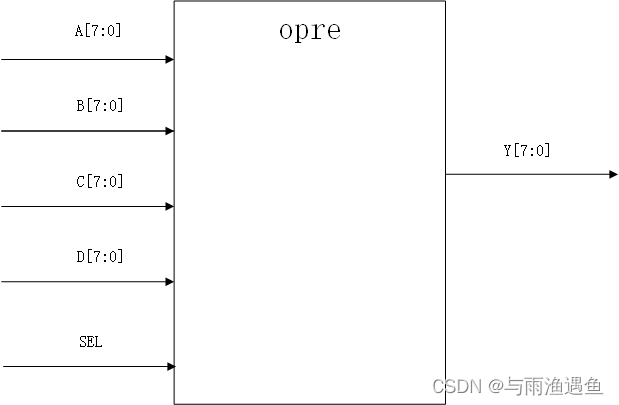

设计目标:设计输入4个8位的变量,输出最大值模块

框图

代码

opra文件

module opre (

input wire [7:0]A,

input wire [7:0]B,

input wire [7:0]C,

input wire [7:0]D,

output wire [7:0]Y

);

assign Y = (A>B&&A>C&&A>D)?A:

(B>A&&B>C&&B>D)?B:

(C>A&&C>B&&C>D)?C:

(D>A&&D>B&&D>C)?D:

8'b00000000;

endmodule

tb文件

`timescale 1ns/1ps

module opre_tb ();

reg [7:0]A;

reg [7:0]B;

reg [7:0]C;

reg [7:0]D;

wire [7:0]Y;

initial begin

A = 8'b00000000;

B = 8'b00000000;

C = 8'b00000000;

D = 8'b00000000;

end

always #2 A = {$random} % 256;

always #2 B = {$random} % 256;

always #2 C = {$random} % 256;

always #2 D = {$random} % 256;

opre opre_1(

.A(A),

.B(B),

.C(C),

.D(D),

.Y(Y)

);

endmodule

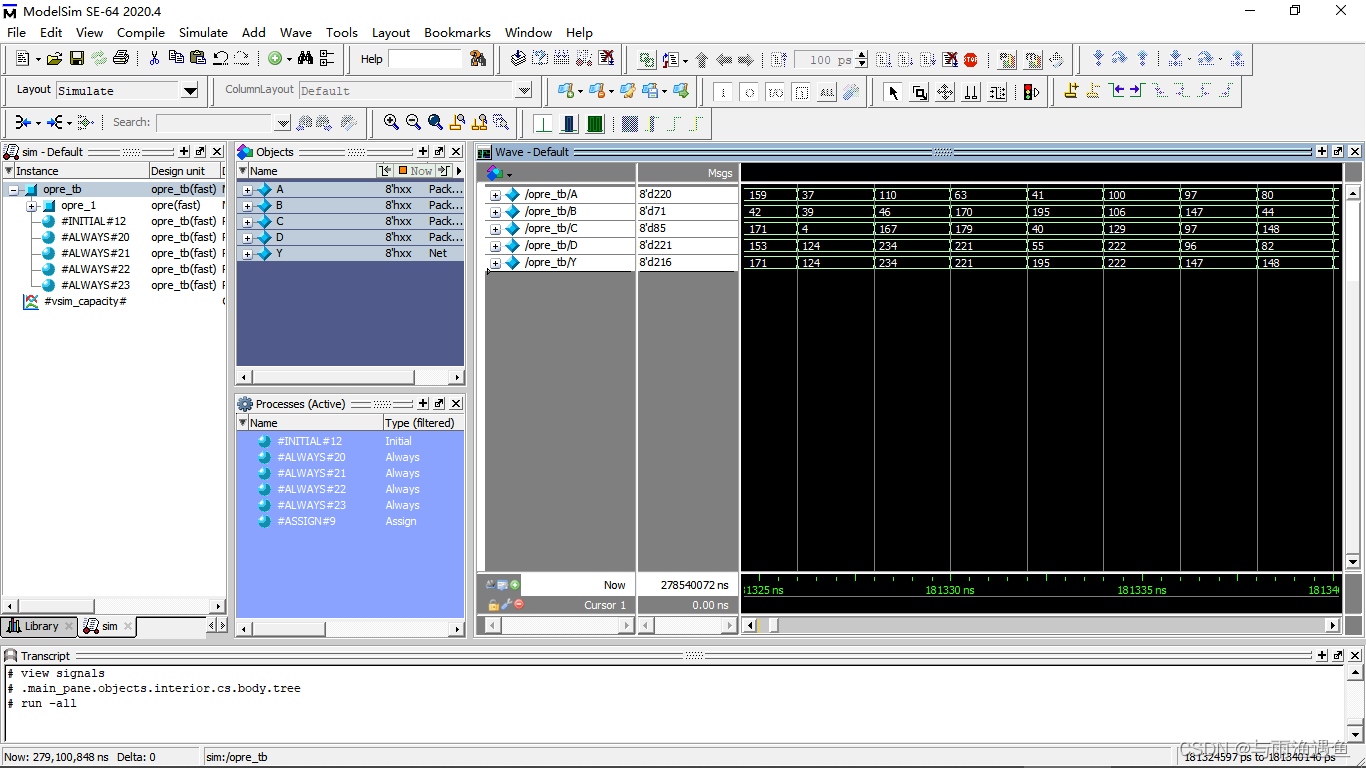

仿真结果

该文介绍了使用Verilog语言设计一个模块,该模块接收4个8位输入变量A、B、C、D,并输出其中的最大值。通过条件赋值语句,当一个输入大于其他所有输入时,该输入作为输出。在测试模块中,使用随机数模拟输入并验证功能。

该文介绍了使用Verilog语言设计一个模块,该模块接收4个8位输入变量A、B、C、D,并输出其中的最大值。通过条件赋值语句,当一个输入大于其他所有输入时,该输入作为输出。在测试模块中,使用随机数模拟输入并验证功能。

5630

5630

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?