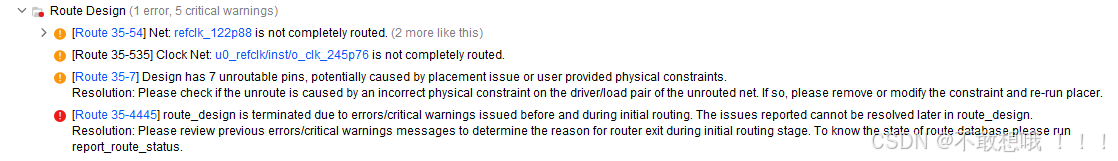

问题描述:出现该问题原因在于高速接口时钟接线错误

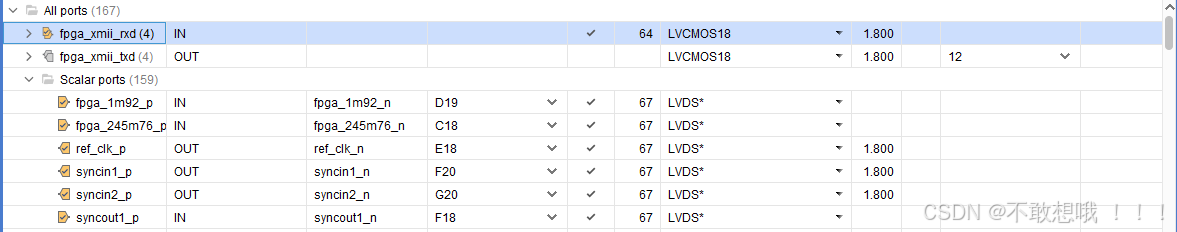

1. 检查pin脚接线是否都接上了;

若出现选择pin脚时出现invalid,检测对应pin信号是否使用错误,

例如:

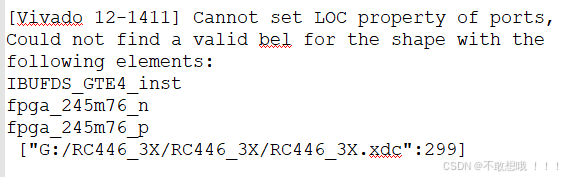

原因在于对应 fpga_245m76_n/p为普通IO信号,而该信号用在了高速接口的源语上;

改正:采用普通差分转单端源语(IBUFDS)即可;

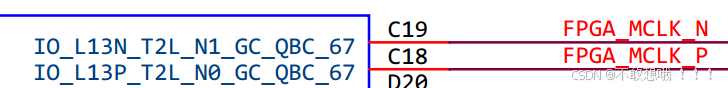

2. 查看原理图,查看需要连接的管脚是否是MGT类型

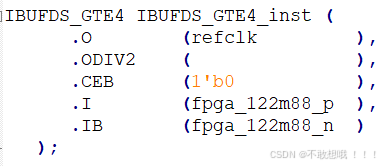

3. 代码上使用IBUFDS_GTE4原语进行差分转单端;

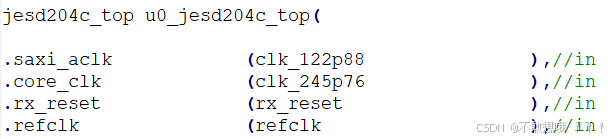

4. 将单端信号直接与jesd204c_phy的QPLL相连即可;

Block design 连接:

905

905

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?