问题的由来:我们在写Verilog时,有一些代码可能是仿真需要的,但不需要综合,那么在Vivado环境中如何处理呢?

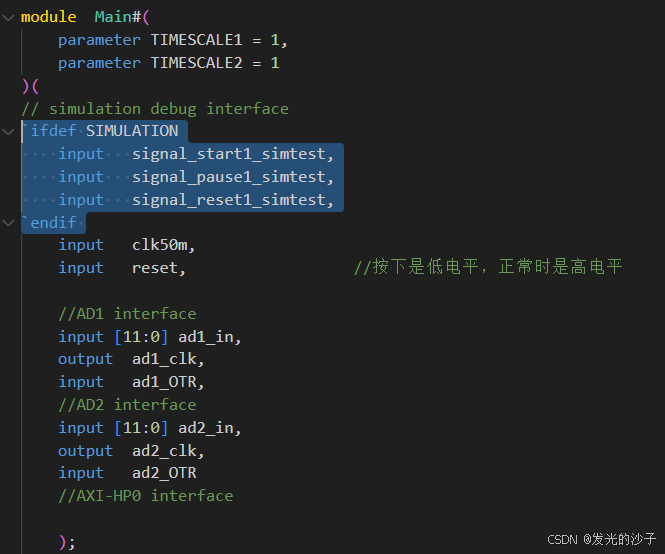

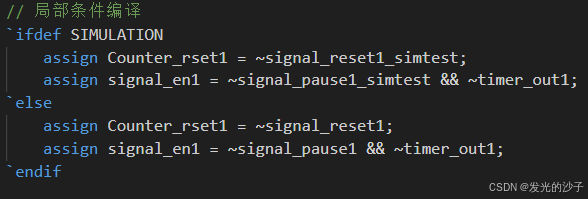

1、使用宏定义

如上图所示,使用`ifdef以及`endif将仿真代码部分包裹起来即可

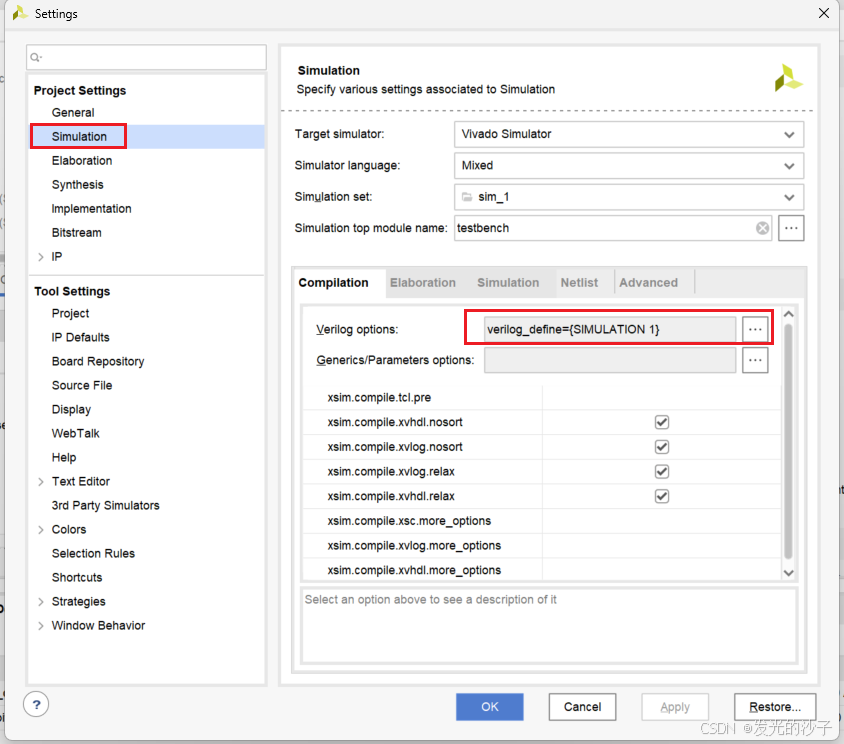

2、如何在Vivado实现仿真时自动宏定义呢?

-

打开仿真设置

- 右键点击项目名 → Project Settings → 左侧导航栏选择 Simulation

-

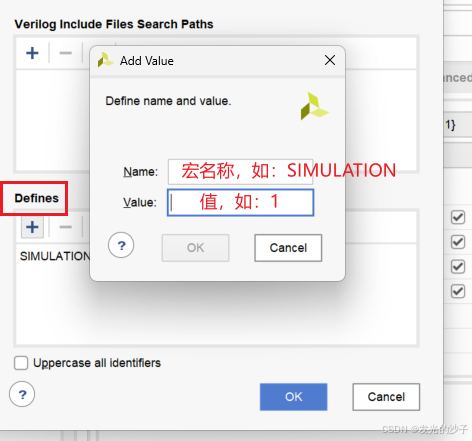

配置宏定义

- 在右侧面板点击 Compilation 选项

- 找到 Verilog options输入框

- 在下方的Defines定义宏

-

验证设置

- 运行仿真后,在Tcl控制台查看编译命令是否包含

-d SIMULATION参数。

- 运行仿真后,在Tcl控制台查看编译命令是否包含

1746

1746

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?