问题的由来:国产的芯片太难用了,必须要用例程设定好的程序才能读写。而且文档错误巨多。

实验设置:ZYNQ7020B、Vivado 2019.1

1、PS侧工程建立

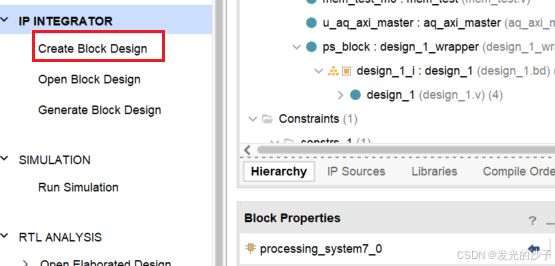

1)点击“Create Block Design",创建一个 Block 设计,也就是图形化设计

2)搜索“zynq”,在搜索结果列表中双击“ZYNQ7 Processing System“。

3)双击 Block图中的“processing_system7_0”,配置相关参数。

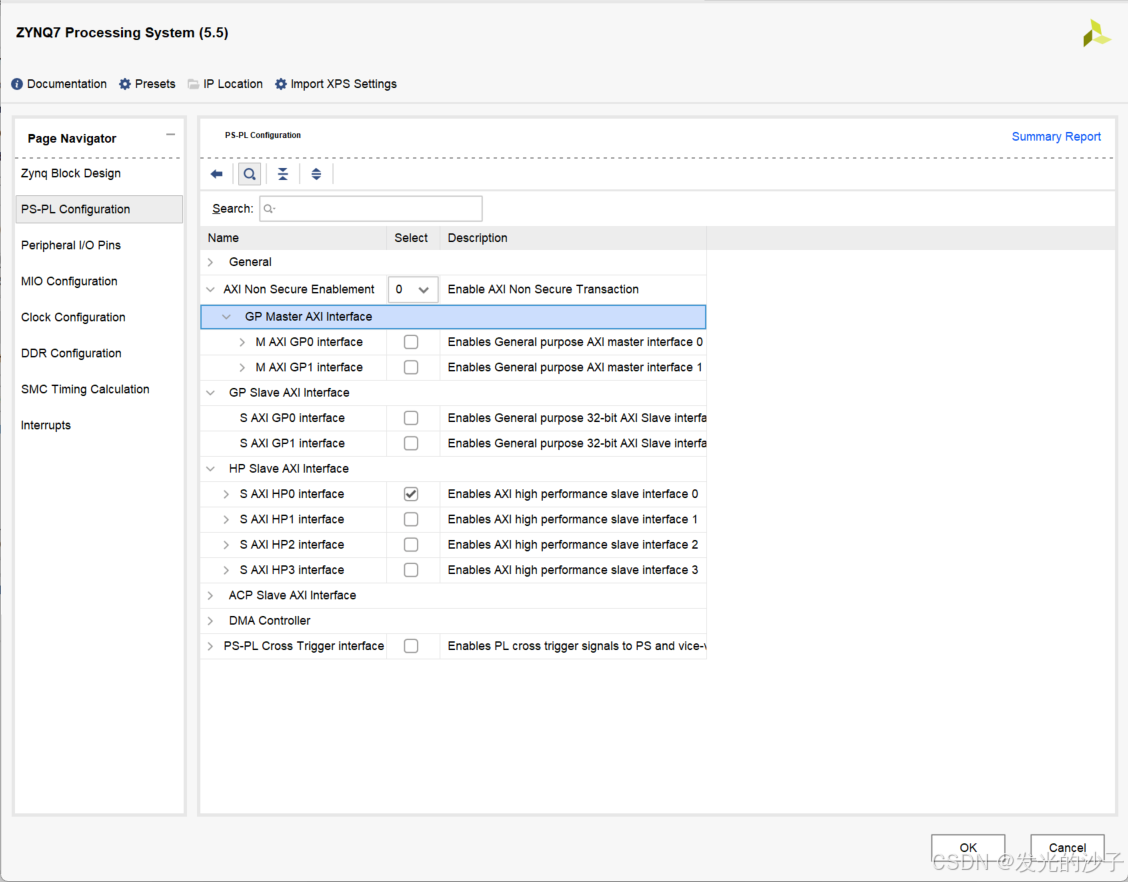

4) PS-PL Configuration 界面,这个界面主要是进行 PS与PL之间接口的配置,主要是 AXI 接口,这些接口可以扩展 PL 端的 AX 接口外设,所以 PL如果要和 PS 进行数据交互,都要按照 AXI总线协议进行,xilinx 为我们提供了大量的 AXI接口的IP 核。在这里我打开了HP0通道(带宽是64bit,150MHz,但我们只能设置100MHz,后面会详细说)。

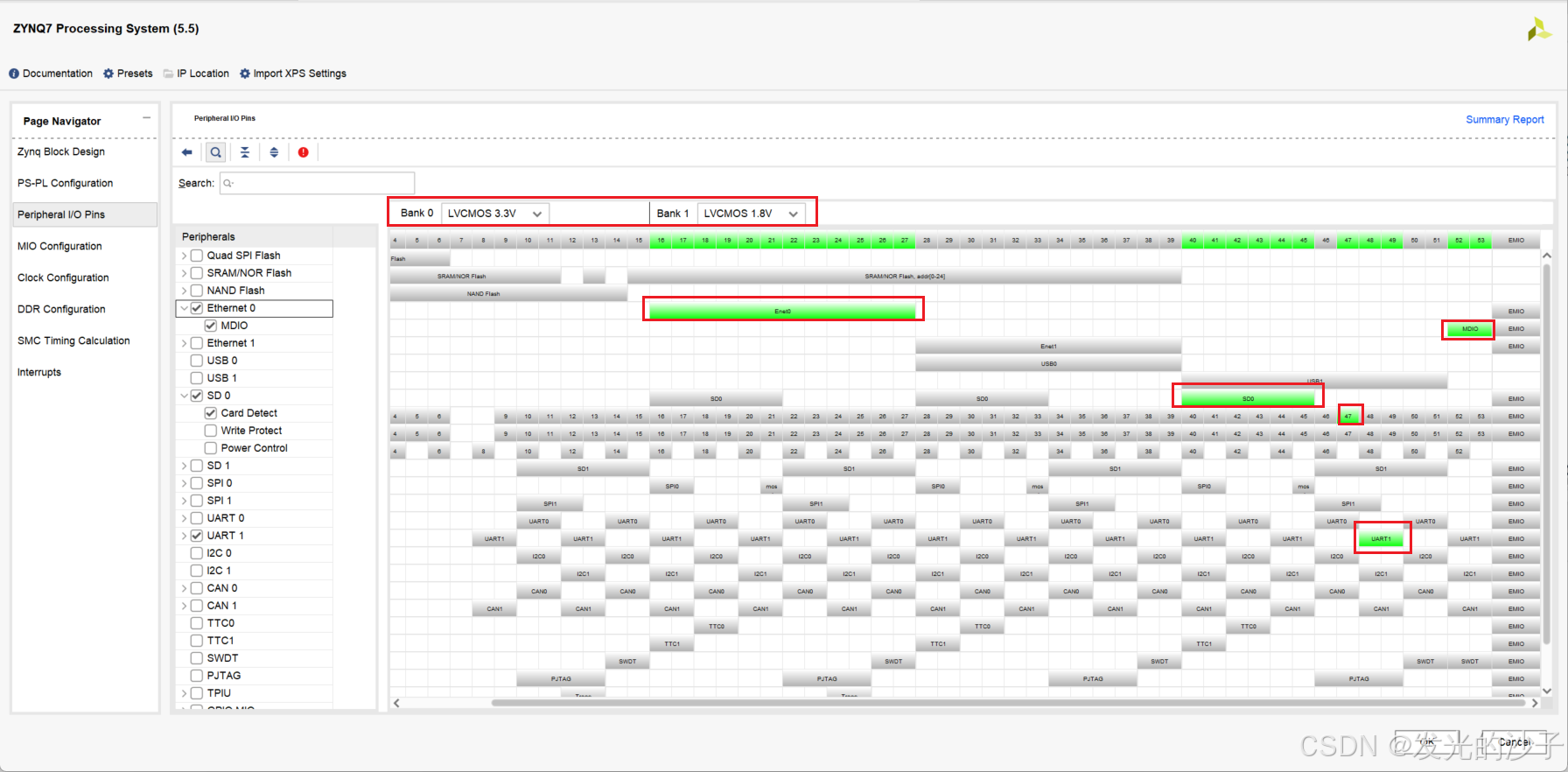

5)所需要的外设,打开 Eth0、SD0、UART1并且设备Bank0的电压3.3V,Bank1的电压1.8V。点方块就能变成绿色的了。

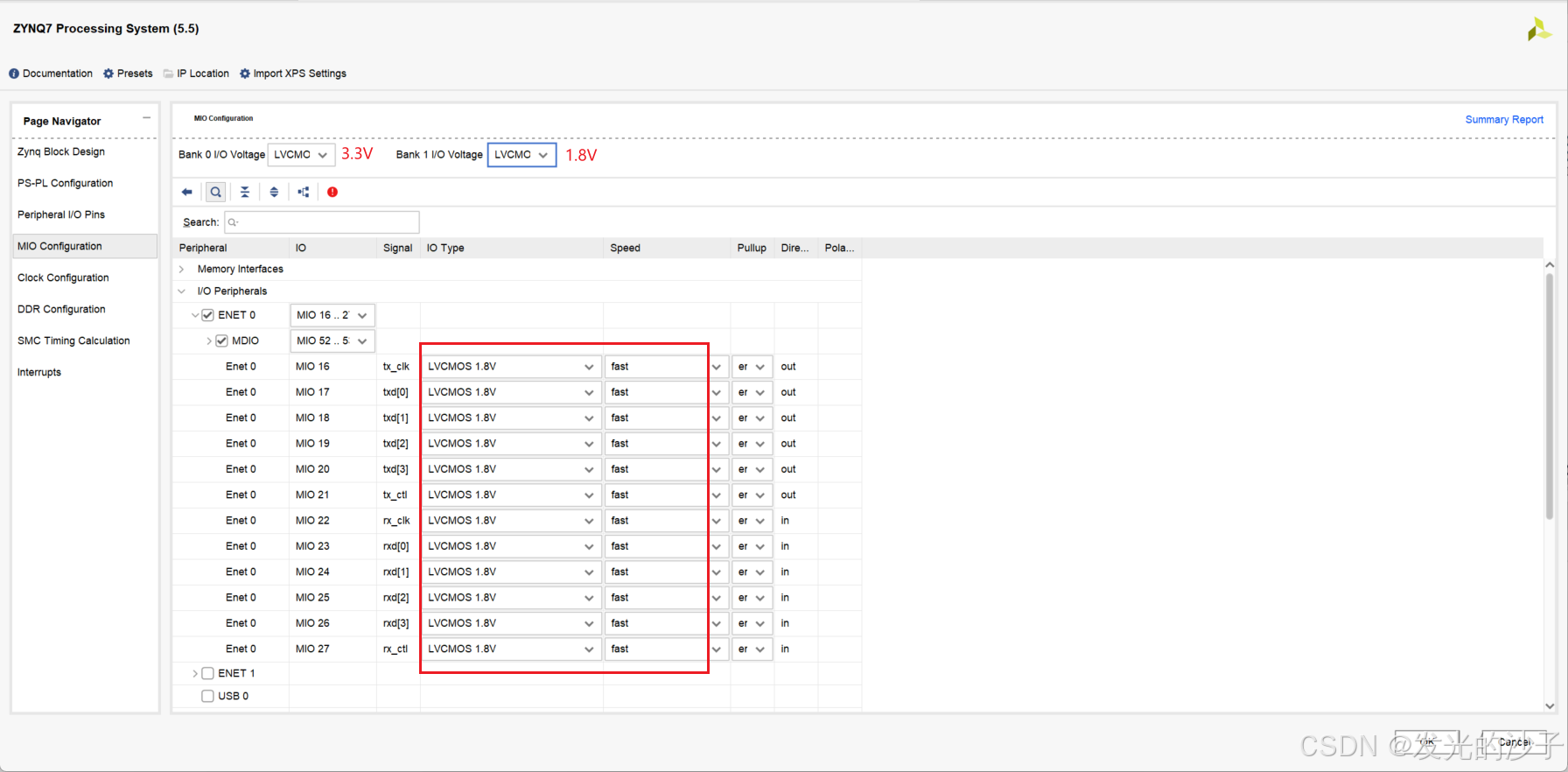

6)修改 Enet0 的电平标准为 HSTL 1.8V,Speed 为 fast,这些参数非常重要,如果不修改,网络可能不通。其他部分保持默认。

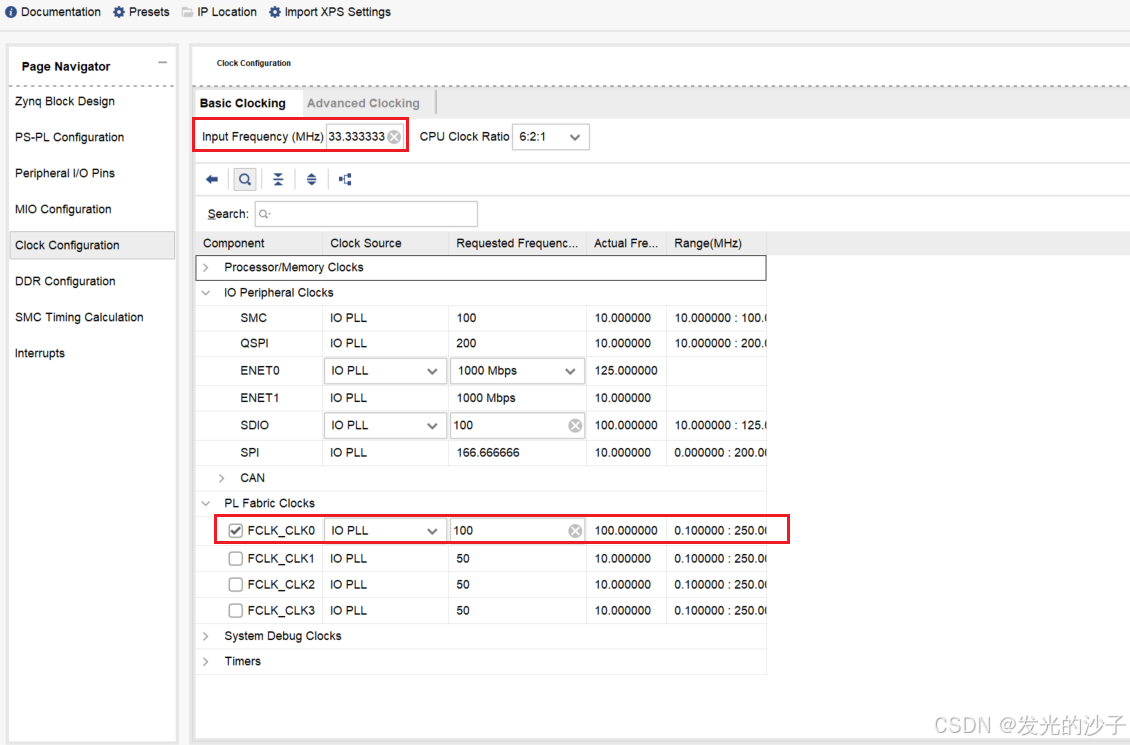

7)如果上述都按我说的设置,那么在此处的时钟,FCLK_CLK0(AXI-HP0)通道就无法设置为150MHz(应该是142MHz),所以为了兼容设置,我们设置AXI-HP通道的速率为100MHz。

7)如果上述都按我说的设置,那么在此处的时钟,FCLK_CLK0(AXI-HP0)通道就无法设置为150MHz(应该是142MHz),所以为了兼容设置,我们设置AXI-HP通道的速率为100MHz。

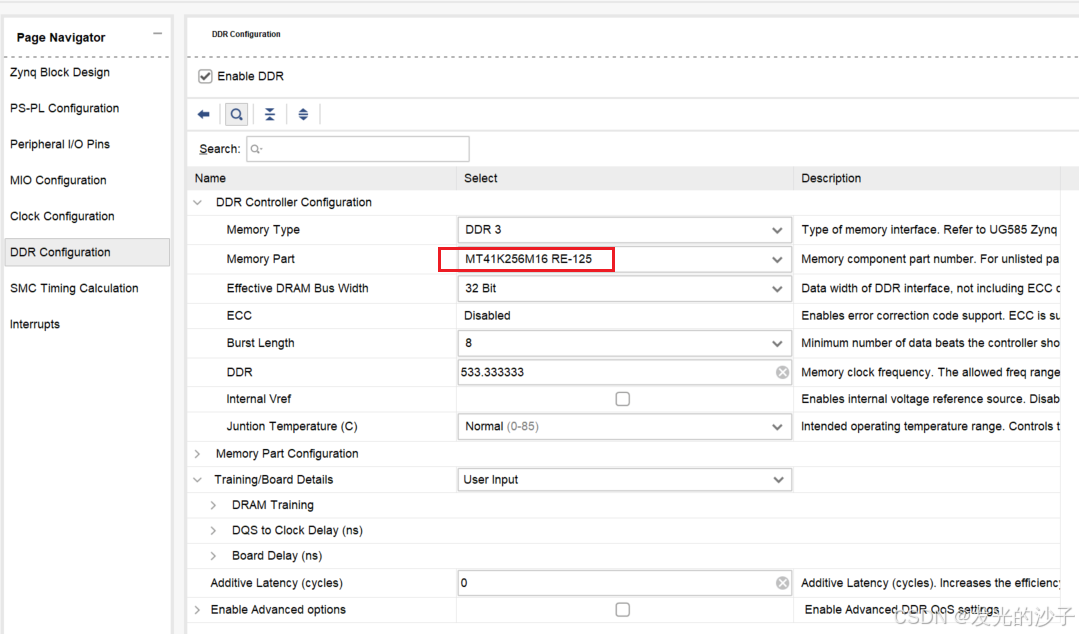

8)DDR配置:在“DDR Configuration”选项卡中可以配置 Ps 端 ddr 的参数,配置 DDR3 型号为“MT41J256M16 RE-125”,这里ddr3 型号并不是板子上的ddr3 型号,而是参数最接近的型号。Effective DRAM Bus Width",选择“32 Bit'

至此,PS端的CPU就配置好了,点击左下角的OK即可。

至此,PS端的CPU就配置好了,点击左下角的OK即可。

2、添加下述模块,并依据我的接线连接。地址自动分配。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2580

2580

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?