《可编程数字逻辑电路设计》课程中Quartus II软件的使用说明

VHDL和Verilog HDL不一样。

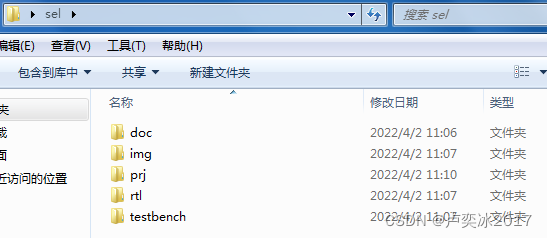

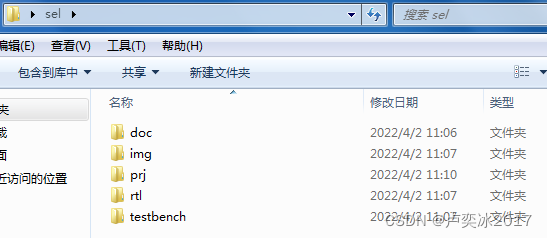

1.新建文件夹,里面包含5个子文件夹(doc/img/prj/rtl/testbench)

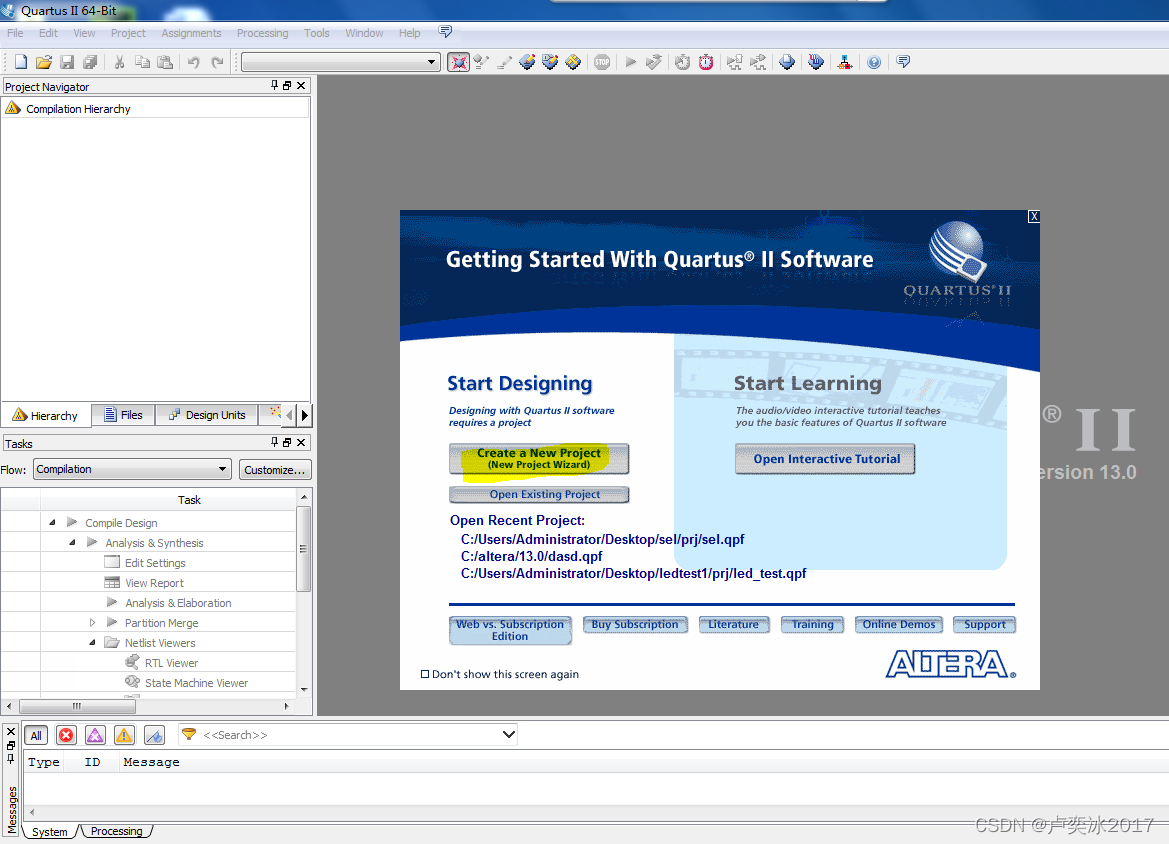

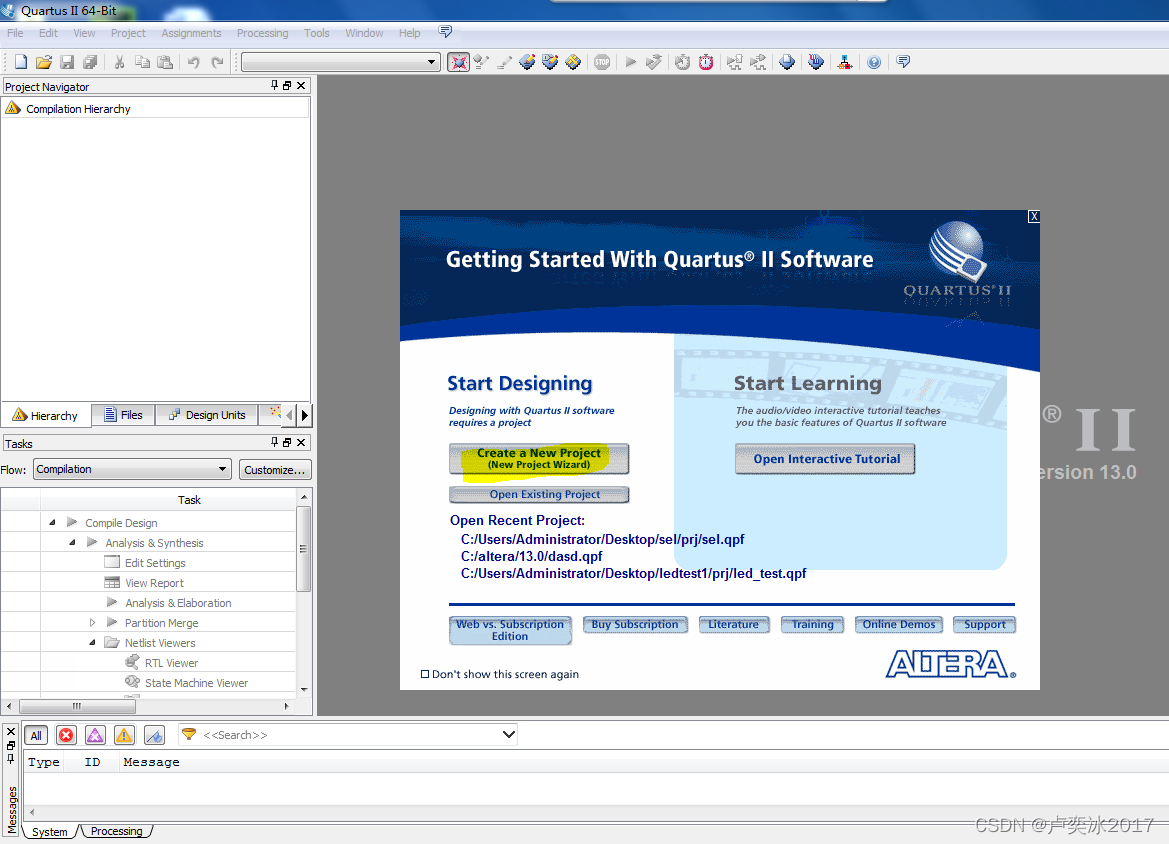

2.打开Quartus II软件 ,创建新工程。

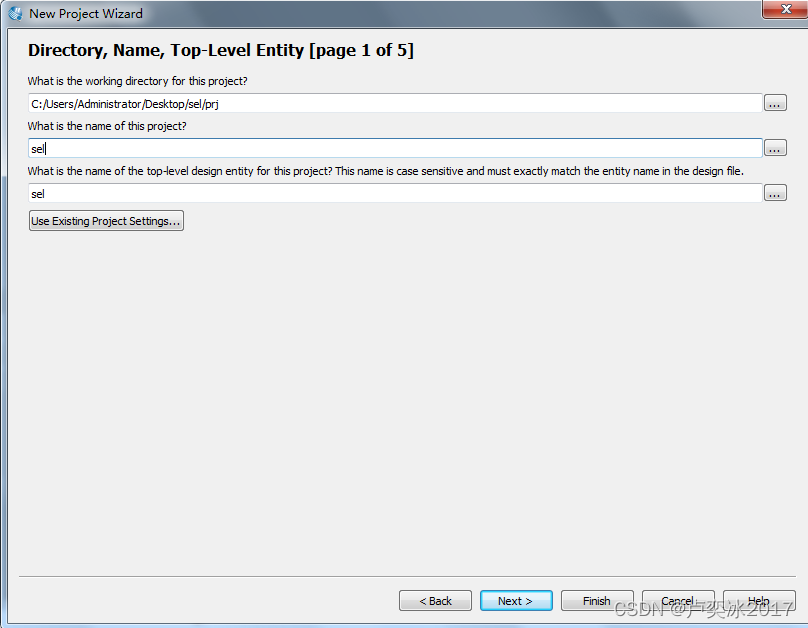

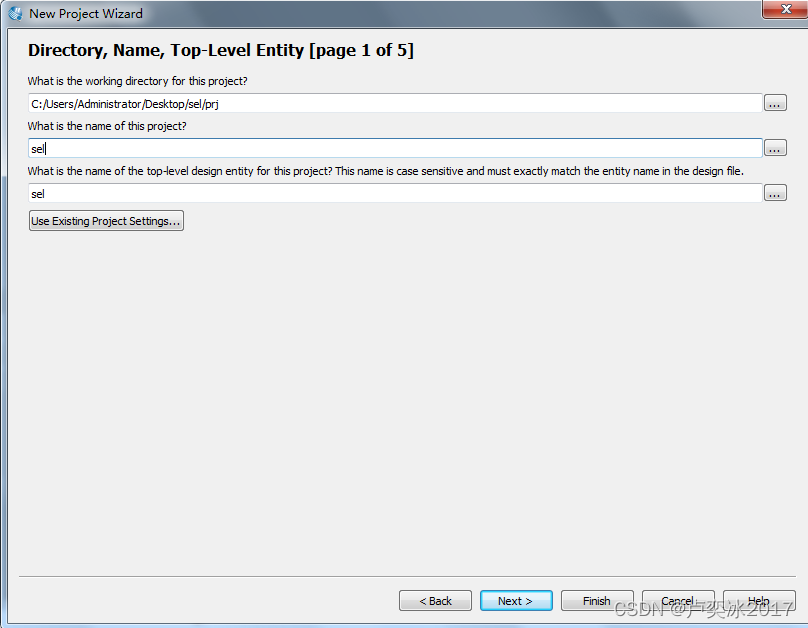

3. 选择工程目录为步骤1新建的文件夹的路径;为这个工程起个名字(sel)。

3. 选择工程目录为步骤1新建的文件夹的路径;为这个工程起个名字(sel)。

4.设置为Cyclone IV E,引脚数256,速度8,选择设备为EP4CE10F...

4.设置为Cyclone IV E,引脚数256,速度8,选择设备为EP4CE10F...

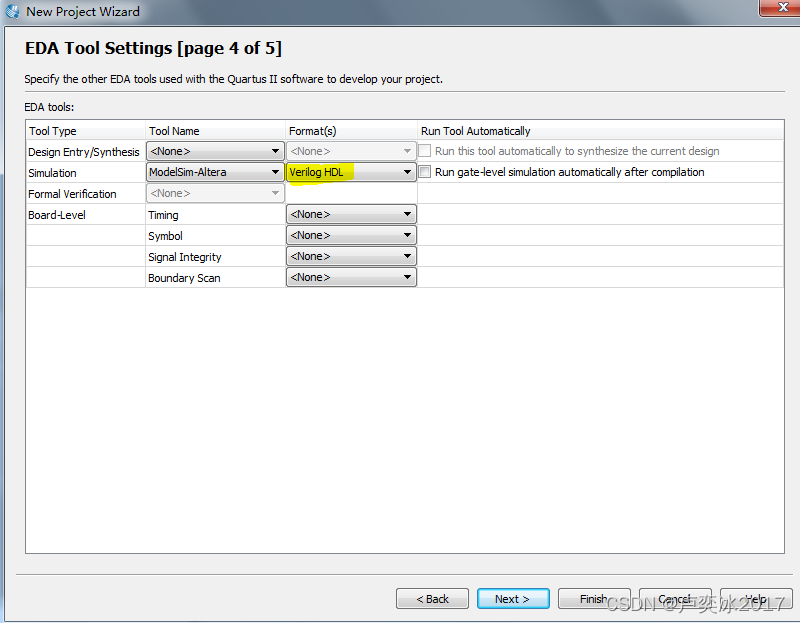

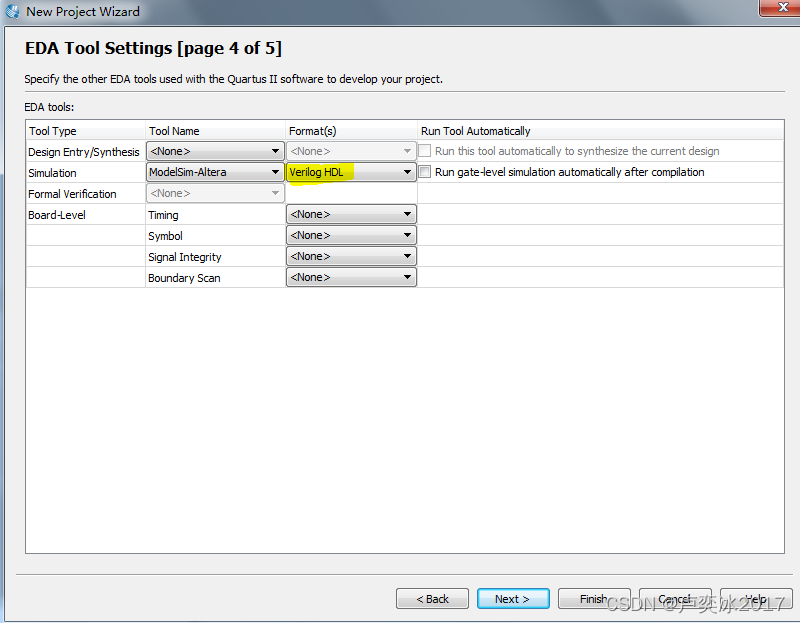

5.仿真环境:Verilog HDL

5.仿真环境:Verilog HDL

6.完成。Finish!

6.完成。Finish!

该文介绍了如何使用QuartusII软件进行VerilogHDL设计,详细步骤包括工程创建、文件组织、设置参数、编写二选一数据选择器代码,并讲解了Verilog的关键元素如模块、端口、逻辑操作符等。此外,还涉及到了测试代码的编写、编译以及代码链接的建立。

该文介绍了如何使用QuartusII软件进行VerilogHDL设计,详细步骤包括工程创建、文件组织、设置参数、编写二选一数据选择器代码,并讲解了Verilog的关键元素如模块、端口、逻辑操作符等。此外,还涉及到了测试代码的编写、编译以及代码链接的建立。

《可编程数字逻辑电路设计》课程中Quartus II软件的使用说明

VHDL和Verilog HDL不一样。

1.新建文件夹,里面包含5个子文件夹(doc/img/prj/rtl/testbench)

2.打开Quartus II软件 ,创建新工程。

3. 选择工程目录为步骤1新建的文件夹的路径;为这个工程起个名字(sel)。

3. 选择工程目录为步骤1新建的文件夹的路径;为这个工程起个名字(sel)。

4.设置为Cyclone IV E,引脚数256,速度8,选择设备为EP4CE10F...

4.设置为Cyclone IV E,引脚数256,速度8,选择设备为EP4CE10F...

5.仿真环境:Verilog HDL

5.仿真环境:Verilog HDL

6.完成。Finish!

6.完成。Finish!

4709

4709

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?