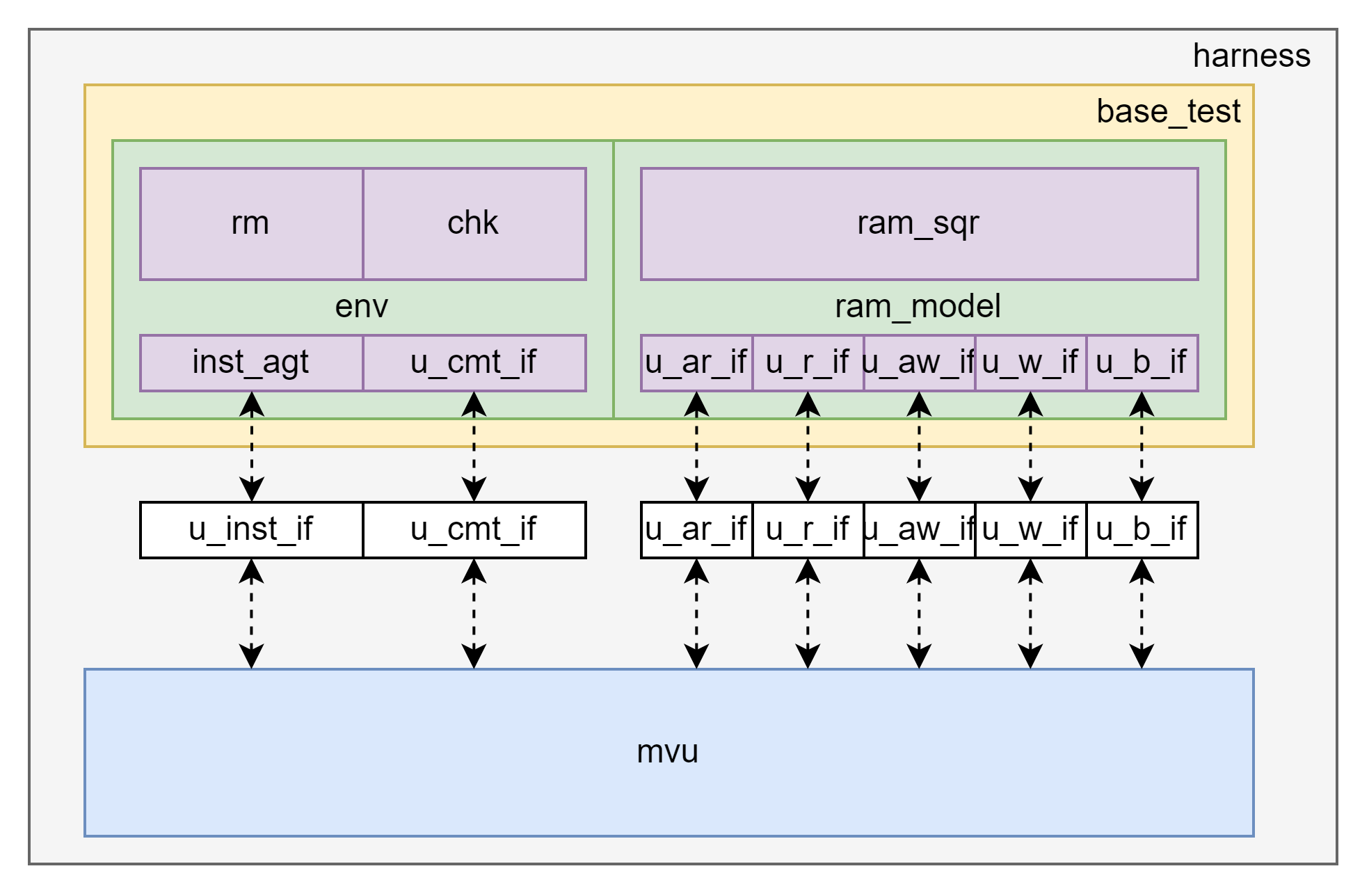

在完成了所有的utils包括apb_utils之后,就要进行验证环境的整体搭建,因此我们再把验证环境拿出来看一下:

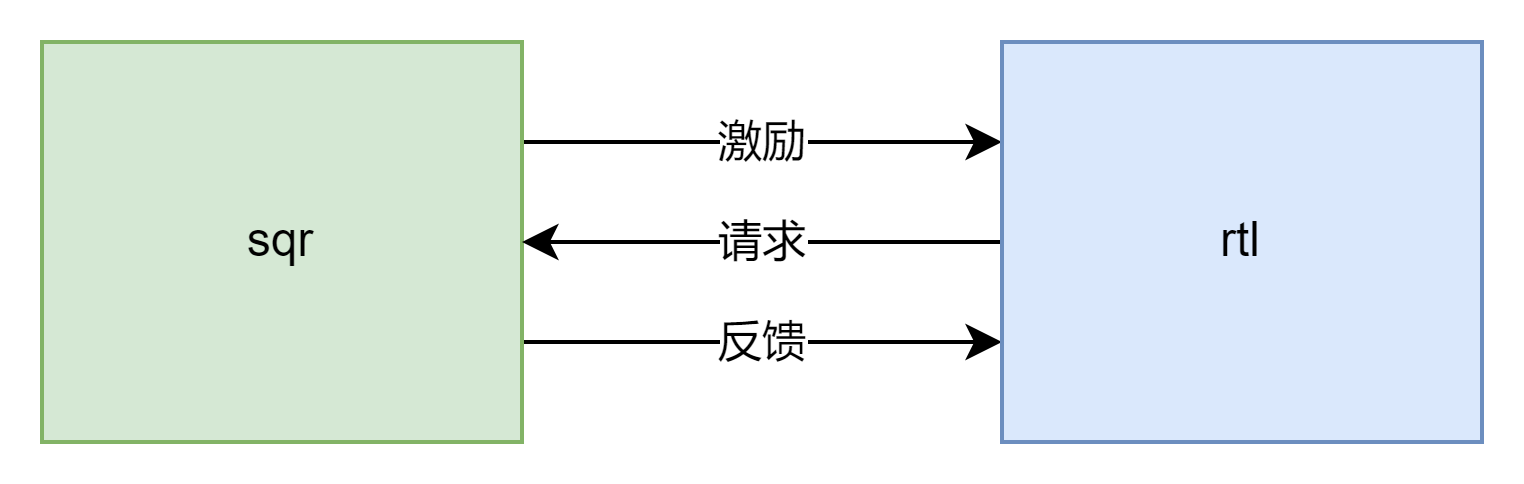

按照由底至顶层的思路,接下主要有五大部分需要我们完成:ram_model、reference_model、env、base_test和harness,这一篇从最难的ram_model开始说起。这个最难其实是对我自己而言的,因为我在转UVM方法学的过程中留了一个遗留问题没有解决,就是多种seq/sqr协同并且rtl交互的问题:

关于转UVM方法学以及后面的事可以看看在知乎的更文:

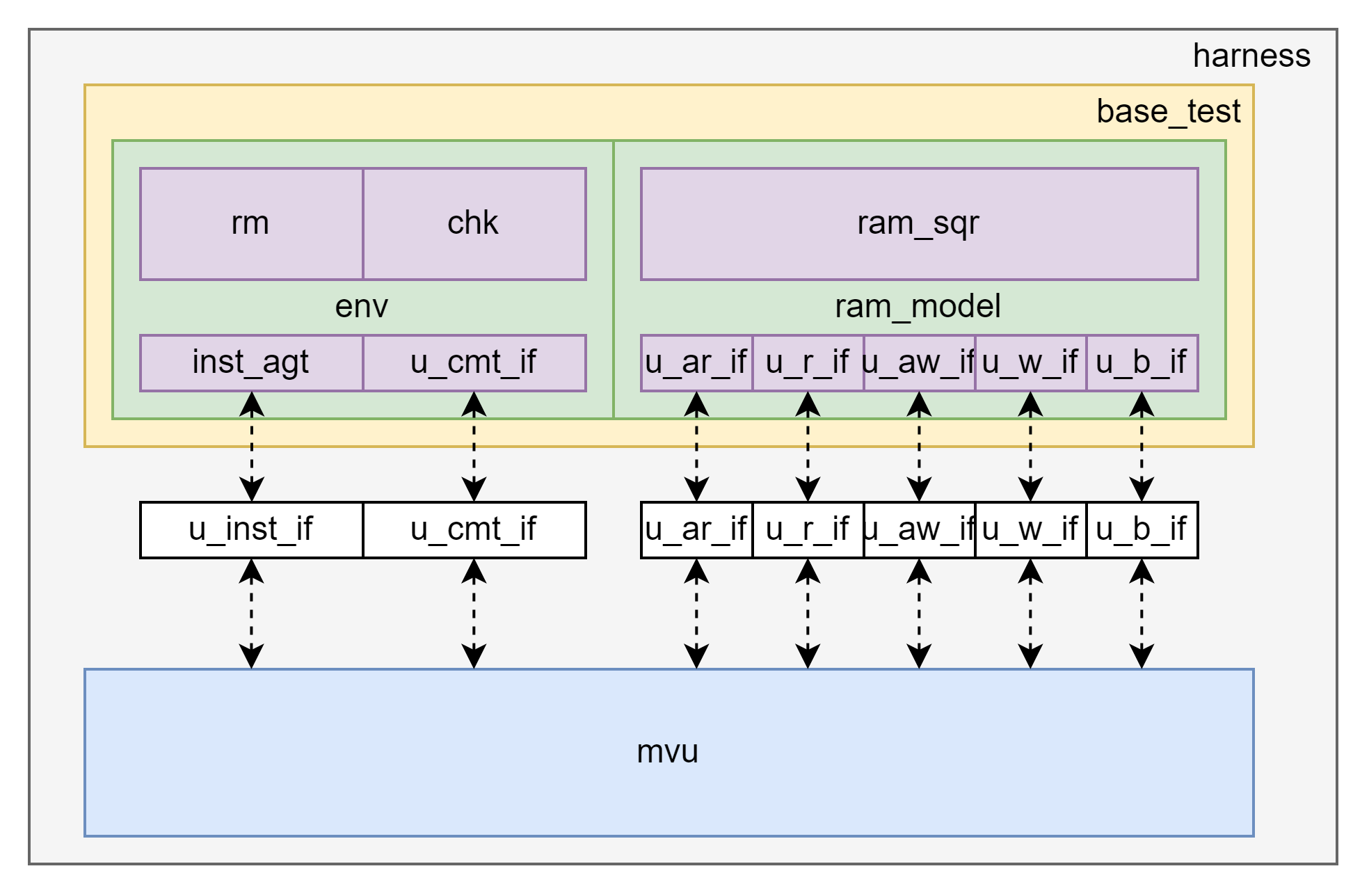

在完成了所有的utils包括apb_utils之后,就要进行验证环境的整体搭建,因此我们再把验证环境拿出来看一下:

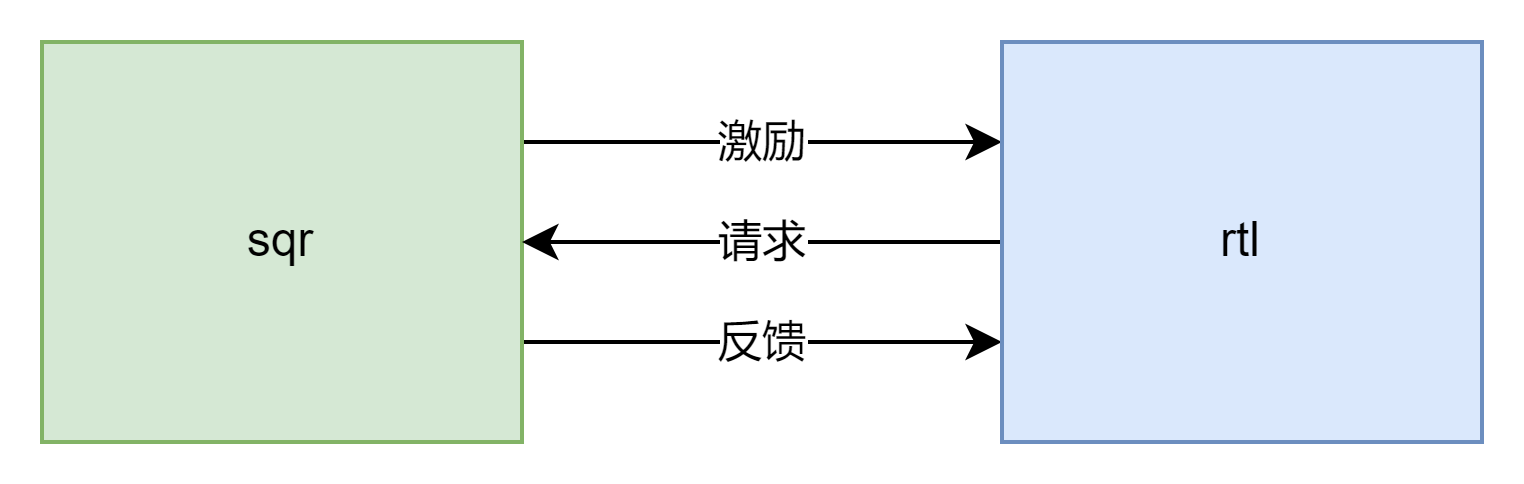

按照由底至顶层的思路,接下主要有五大部分需要我们完成:ram_model、reference_model、env、base_test和harness,这一篇从最难的ram_model开始说起。这个最难其实是对我自己而言的,因为我在转UVM方法学的过程中留了一个遗留问题没有解决,就是多种seq/sqr协同并且rtl交互的问题:

关于转UVM方法学以及后面的事可以看看在知乎的更文:

369

369

2991

2991

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?