Simulation debug capabilities of ATPG: A method to check the values simulated

ATPG’s goal is to create a set of patterns that achieves a given test coverage, where test coverage is the total percentage of testable faults the pattern set detects.

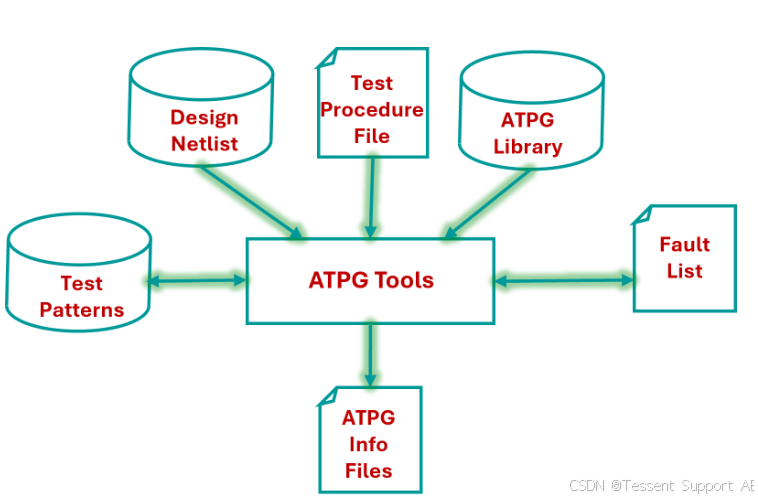

ATPG consists of two main steps: 1) generating patterns to get hard detection only and, 2) performing fault simulation on the generated pattern to determine if the target fault is hard detected or if other undetected faults are possibly detected. Tessent ATPG tools automate these two steps into a single operation or ATPG process. This ATPG process results in patterns you can then save with added tester-specific formatting, enabling a tester to load the pattern data into a chip’s scan cells and otherwise apply the patterns correctly.

The two most typical methods for pattern gene

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

613

613

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?