生成时钟

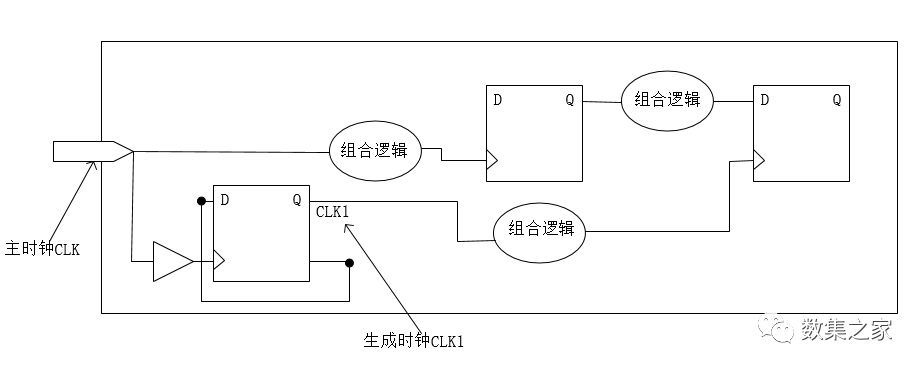

在设计中有这样一类时钟,它是基于一个主时钟并通过相关逻辑转换后,在相位、频率、占空比等方面和主时钟有一定变化的分支时钟。我们可以把这类时钟定义为生成时钟,因此,生成时钟的时钟源来自主时钟,其相位参考主时钟,如下图所示。

使用SDC命令create_generated_clock来定义生成时钟,示例命令如下:

create_clock -period 10 -waveform {0 5} [get_ports CLK]

create_generated_clock -name CLKDIV3 -source CLK -divide_by 3 [get_ports DFF/Q]

以上命令定义的是一个基于主时钟CLK的分支时钟CLKDIV3,CLKDIV3的频率是主时钟的1/3,即生成时钟的周期是主时钟的3倍。生成时钟CLKDIV3与主时钟CLK的时钟信号波形的对比图如下图所示。

本文详细介绍了FPGA设计中时钟生成的概念,包括如何使用SDC命令创建生成时钟,以及在相位和占空比上的设置。通过示例展示了create_generated_clock命令的用法,探讨了生成时钟与主时钟的关系,以及它们在时钟延迟上的特点。同时,文章指出当时钟由多个信号混合产生时,创建独立时钟更为合适。

本文详细介绍了FPGA设计中时钟生成的概念,包括如何使用SDC命令创建生成时钟,以及在相位和占空比上的设置。通过示例展示了create_generated_clock命令的用法,探讨了生成时钟与主时钟的关系,以及它们在时钟延迟上的特点。同时,文章指出当时钟由多个信号混合产生时,创建独立时钟更为合适。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1386

1386

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?