一、PHY

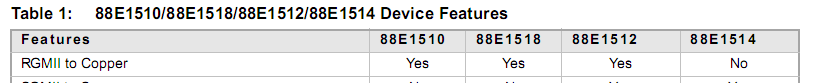

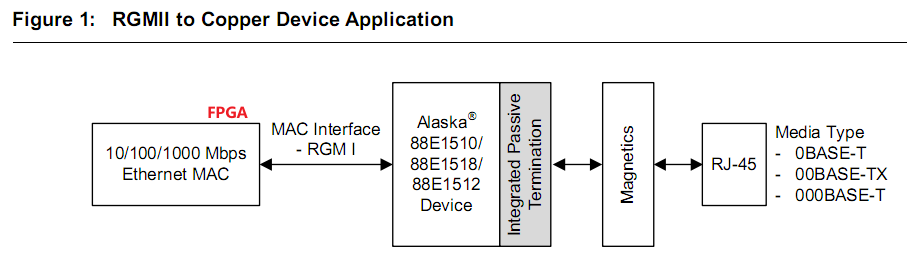

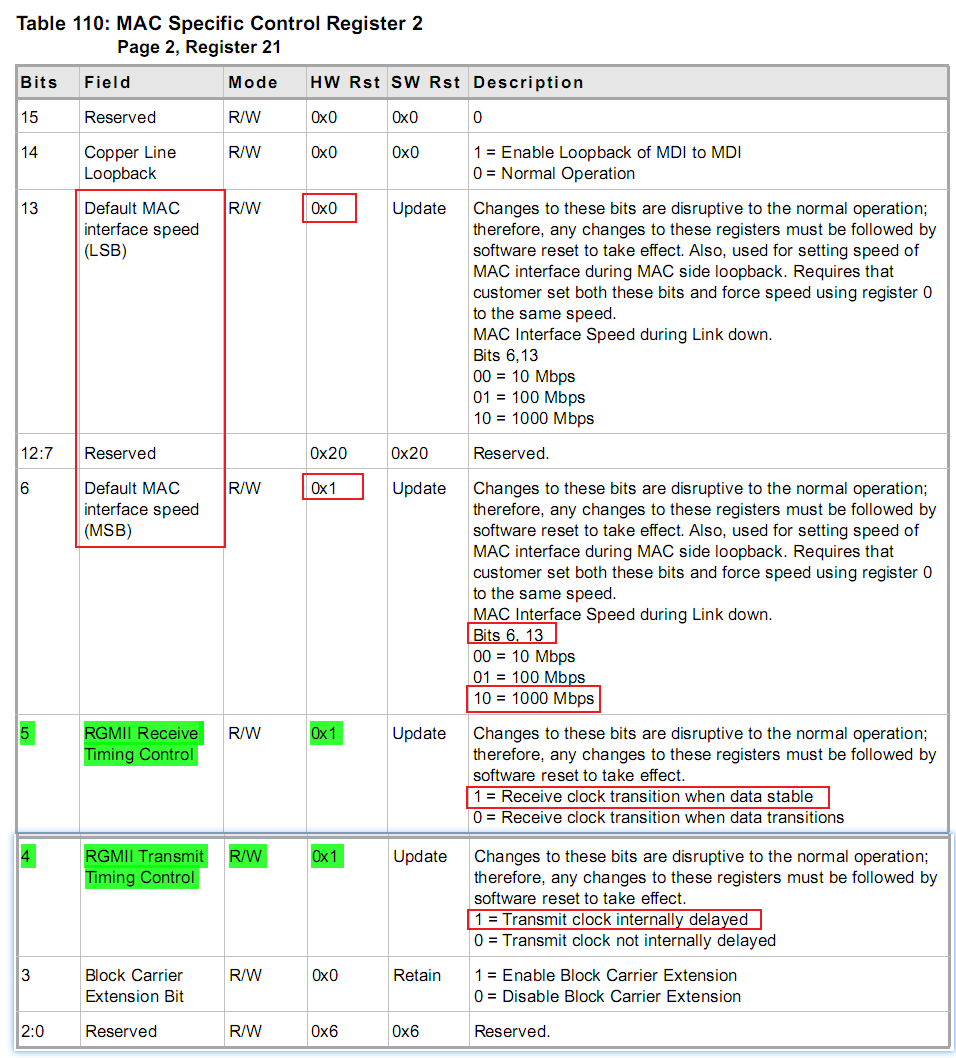

采用Marvell Alaska 88E15xx ,RGMII to Copper

二、RGMII接口

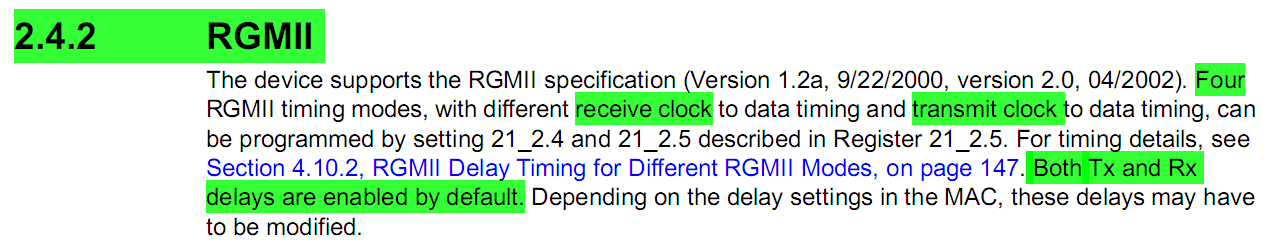

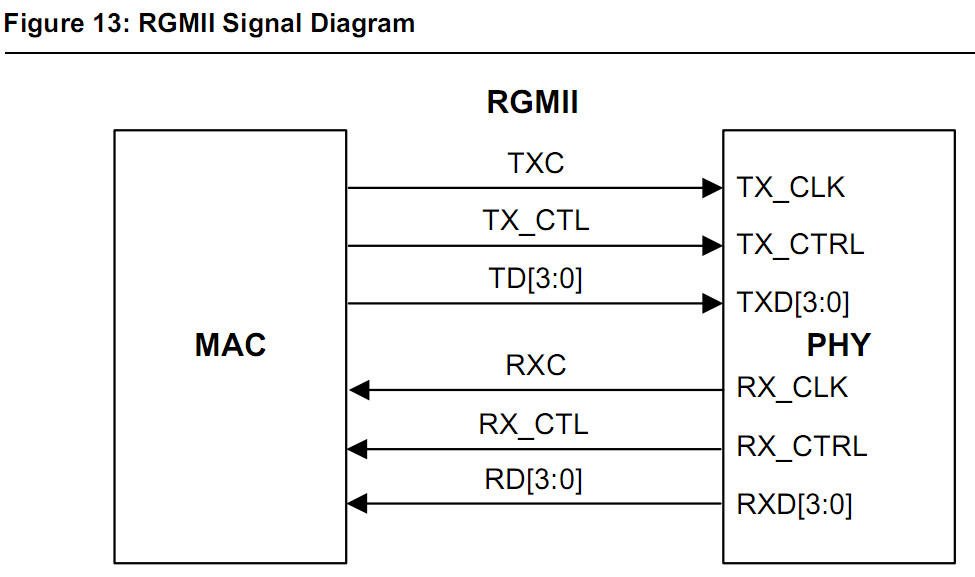

RGMII接口中,可以分别调整发送clk上的延时2ns,接收clk上的延时2ns。默认收发clk都添加了2ns延时,可通过reg配置。默认速率为千兆。

![]()

三、RGMII时序约束

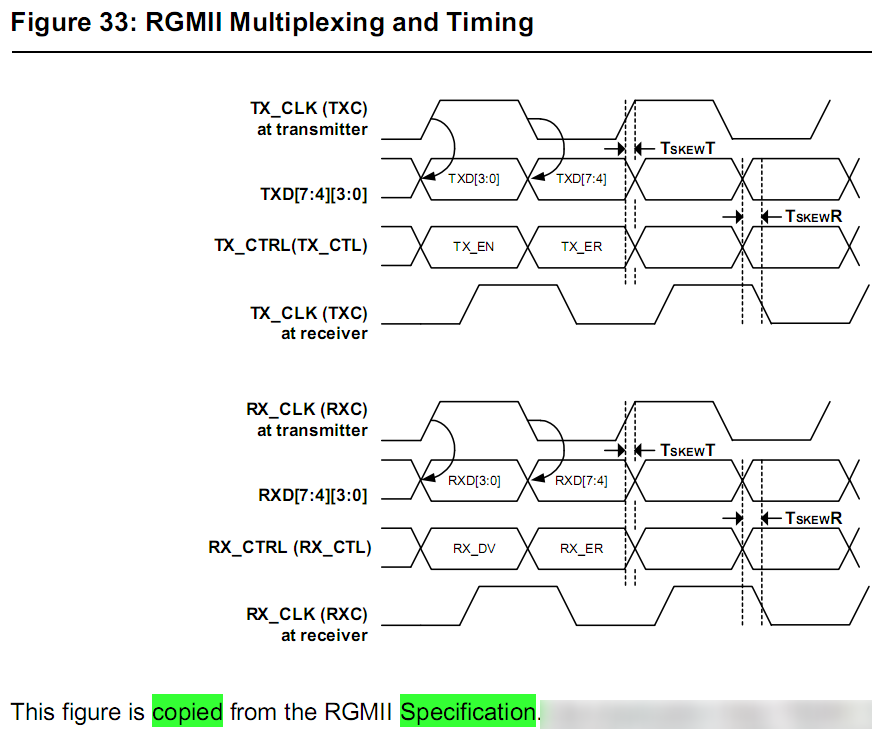

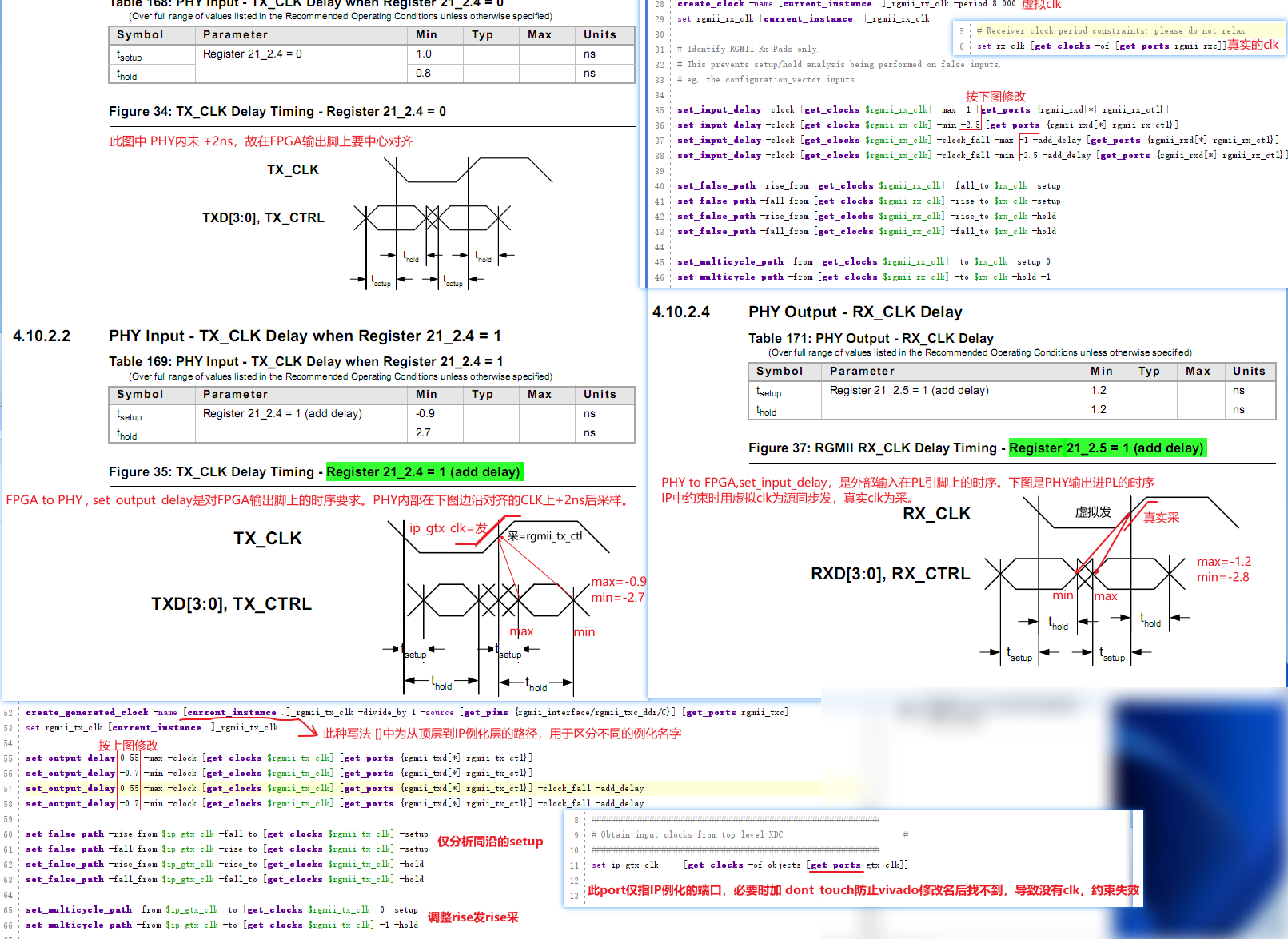

TX,RX都是rise发送数据的[3:0],采样时仍然由rise采样[3:0]。fall发[7:4]fall采[7:4]]。在做input时序约束时,引入虚拟时钟,实现rise发rise采的约束。output约束也按照rise发rise采约束,通过多周期set_multicycle_path 调整建立时间和保持时间的沿,用set_false_path去掉不同沿的setup和相同沿的hold伪路径分析。vivado默认收发采样用不同沿。引入虚拟时钟类似于MMCM-waveform有相位跳变。RGMII有自己的标准说明书,各厂家需遵守。

input/output 约束:“头大尾小”,数据头max,数据尾min。

6293

6293

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?