关于IP的设置说明:

1、若要查看并修改IP的源文件,则不能使用IP的Core container模式,否则所有源文件被打包在容器中(.src/xx/ip/目录下的.xcix文件包含IP配置和源文件),只能用Vivado查看,不能用其它软件打开并修改。在vivado中选中IP后右击选Disable Core Container (也可在软件settings->IP->Core Containers去掉所有IP的容器),即可在工程目录下找到源文件并修改(.src/xx/ip/目录下为.xci文件仅包含IP配置,源文件在.gen/xx/ip/目录下)。修改源文件后的IP可再Enable Core Container把文件打包起来,改动部分仍在,只要不重新Generate Output Products 文件。

2、需要修改IP源文件时,IP生成文件时用Global模式,改动部分可以随工程一起编译。OOC模式仅在生成文件后编译一次生成Design Checkpoint即.DCP文件,后续直接调用且不再编译。

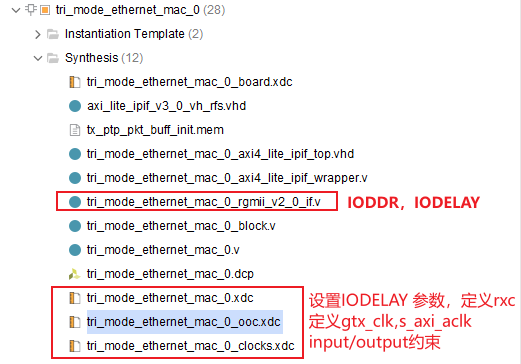

一、IP中文档结构

虽然在vivado中打开时显示Read-only,但是可在目录下找到文件,用其它软件打开修改。IP中根据用户需求要更改的文件主要有4个。

二、文件说明

1、tri_mode_ethernet_mac_0_rgmii_v2_0_if.v

xxx_if.v中是RGMII接口的处理文件,包含IDDR,ODDR,IDELAY,ODELAY等,延时元件的例化、级联都在此文件中。

1)TXC

文件中的默认:TXC用ODDR转发,并延时2ns后输出,与数据中心对齐。单个IODELAY的延时在UltraScale+器件中最大1.1ns,因此需要ODELAY+IDELAY级联才能实现。

注意:

- w.r.t. : with respect to

- 每个IO都有一个Bitslice,其中包括IOserdes、IODELAY。芯片结构中IDELAY在上,Odelay在下。级联时只能I+O交替向下级联下一个IO bitslice的延时组件,可以一直级联到IO所在字节组的最低边界。则最大延时取决于IO在字节组中的位置,在最上时可级联出最大延时。

- 每个BANK包括52个IO,分为4个字节组。每个字节组包括13个IO,上7个IO为upper半字节,下6个IO为lower半字节。

- 同一个bitslice中的IDELAY,ODELAY的延时值必须相同。同时路径上也会增加300ps左右的延时。

- 延时组件属性 Cascade setting (MASTER, NONE, SLAVE_END, SLAVE_MIDDLE) 级联设置中标注级联所在的位置,或不级联。

//----------------------------------------------------------------------------

// RGMII Transmitter Clock Management

//----------------------------------------------------------------------------// Delay the transmitter clock relative to the data.

// For 1 gig operation this delay is set to produce a 90 degree phase

// shifted clock w.r.t. gtx_clk_bufg so that the clock edges are

// centralised within the rgmii_txd[3:0] valid window.// Instantiate the Output DDR primitive

ODDRE1 #(

.SRVAL (1'b0)

) rgmii_txc_ddr (

.Q (rgmii_txc_odelay),

.C (tx_clk),

.D1 (1'b1),

.D2 (1'b0),

.SR (tx_reset)

);

// Instantiate the Output Delay primitive (delay output by 2 ns). In order to

// achieve 2ns, an ODELAY is cascaded with an IDELAY from the bitslice

// immediately below it.

ODELAYE3 #(

.DELAY_VALUE (1000),

.DELAY_TYPE ("FIXED"),

.CASCADE ("MASTER"),

.REFCLK_FREQUENCY (333.333),

.SIM_DEVICE ("ULTRASCALE_PLUS")

)

delay_rgmii_tx_clk (

.ODATAIN (rgmii_txc_odelay),

.DATAOUT (rgmii_txc_obuf),

.CLK (1'b0),

.CE (1'b0),

.INC (1'b0),

.CNTVALUEIN (9'h0),

.CNTVALUEOUT (),

.LOAD (1'b0),

.RST (1'b0),

.CASC_IN (1'b0),

.CASC_RETURN (delay_rgmii_tx_clk_casc_return),

.CASC_OUT (delay_rgmii_tx_clk_casc_out),

.EN_VTC (1'b1)

);IDELAYE3 #(

.DELAY_VALUE (0),

.DELAY_TYPE ("FIXED"),

.CASCADE ("SLAVE_END"),

.REFCLK_FREQUENCY (333.333),

.SIM_DEVICE ("ULTRASCALE_PLUS")

)

delay_rgmii_tx_clk_casc (

.IDATAIN (1'b0),

.DATAOUT (delay_rgmii_tx_clk_casc_return),

.DATAIN (1'b0),

.CLK (1'b0),

.CE (1'b0),

.INC (1'b0),

.CNTVALUEIN (9'h0),

.CNTVALUEOUT (),

.LOAD (1'b0),

.RST (1'b0),

.CASC_IN (delay_rgmii_tx_clk_casc_out),

.CASC_RETURN (1'b0),

.CASC_OUT (),

.EN_VTC (1'b1)

);

2)TXD

数据在ODDRE1后仅用1个ODELAY延时

//---------------------------------------------------------------------------

// RGMII Transmitter Logic :

// drive TX signals through IOBs onto RGMII interface

//---------------------------------------------------------------------------

// Instantiate Double Data Rate Output components. Then

// put data and control signals through ODELAY components to

// provide similiar net delays to those seen on the clk signal.//ODDRE1 + ODELAYE3 //代码结构

3)RXC

rxc不能用IDELAY延时,输入后接入2个BUFG,一个给数据的IDDR采样,一个给后续的逻辑处理IDDR输出的数据

// Route rgmii_rxc through a BUFG and onto clock routing

BUFG

bufg_rgmii_rx_clk (

.I (rgmii_rxc_ibuf),

.O (rx_clk_int)

);// Route rgmii_rxc through a BUFG for connecting to IDDR components

BUFG

bufg_rgmii_rx_clk_iddr (

.I (rgmii_rxc_ibuf),

.O (rx_clk_iddr)

);

4)RXD,RXCTL

接收的数据先经过IDELAY延时后,用IDDR转换。

//---------------------------------------------------------------------------

// RGMII Receiver Logic : receive signals through IOBs from RGMII interface

//---------------------------------------------------------------------------// Drive input RGMII Rx signals from PADS through IODELAYS.

// Please modify the IODELAY_VALUE according to your design.

// For more information on IDELAYCTRL and IODELAY, please refer to

// the User Guide.IDELAYE3 + IDDRE1

2、tri_mode_ethernet_mac_0_ooc.xdc

在IP生成时选择global模式时该文件不使用,仅在OOC模式使用。如果在顶层的XDC文件中已经定义,最好把此处的注释掉,避免多处定义起冲突。

# This constraints file contains default clock frequencies to be used during creation of a

# Synthesis Design Checkpoint (DCP). For best results the frequencies should be modified

# to match the target frequencies.

# This constraints file is not used in top-down/global synthesis (not the default flow of Vivado).

###################################

# TX Clock period Constraints

###################################

# Transmitter clock period constraints: please do not relax

create_clock -name gtx_clk_ooc -period 8.000 [get_ports gtx_clk]

set_property HD.CLK_SRC BUFGCTRL_X0Y0 [get_ports gtx_clk]###################################

# AXI-Lite Clock period Constraints

###################################

create_clock -name cpu_clk_ooc -period 8.000 [get_ports s_axi_aclk]

set_property HD.CLK_SRC BUFGCTRL_X0Y2 [get_ports s_axi_aclk]

3、tri_mode_ethernet_mac_0.xdc

创建输入FPGA的RXC,若在顶层已经创建,此处最好注释掉。

set_property DELAY_VALUE设置各延时模块的延时值;CASCADE 设置级联属性; IODELAY_GROUP 设置分组;

- 同一个bank的延时元件为一个组,共享一个IDELAYCRTL,都约束为同一个组。若多个bank都有延时,IDELAYCTRL可以分别定义并约束到各组,也可以只在top文件定义一个,由vivado自动复制到各bank用。

- 延时值在UltraScale+中最大1100ps;

- 某个字节组中在混合模式下有用到Bitslice_control时,会用此来校准延时,而不是用IDELAYCTRL。

############################################################

# RX Clock period Constraints (per instance) #

############################################################

# Receiver clock period constraints: please do not relax

create_clock -period 8 [get_ports rgmii_rxc]############################################################

# RGMII: IODELAY Constraints

############################################################

# Please modify the value of the IDELAY_VALUE/ODELAY_VALUE according to your design.

# For more information on IDELAYCTRL and IODELAY, please refer to the User Guide.

#

# Apply the same DELAY_VALUE to all RGMII RX inputs.

# DELAY_VALUE is the time represenatation of the desired delay in ps

# This is to provide a similiar Clock Path and Data Path delay.

set_property DELAY_VALUE 1000 [get_cells {rgmii_interface/delay_rgmii_rx* rgmii_interface/rxdata_bus[*].delay_rgmii_rx*}]

# Group IODELAY components

set_property IODELAY_GROUP tri_mode_ethernet_mac_iodelay_grp [get_cells {rgmii_interface/delay_rgmii_tx* rgmii_interface/txdata_out_bus[*].delay_rgmii_tx*}]

set_property IODELAY_GROUP tri_mode_ethernet_mac_iodelay_grp [get_cells {rgmii_interface/delay_rgmii_rx* rgmii_interface/rxdata_bus[*].delay_rgmii_rx*}]

4、tri_mode_ethernet_mac_0_clock.xdc

此模块中是正式的input delay,output delay约束,具体数值来源见上一篇。

此中定义了一个虚拟时钟,虽没有具体的IO对应它,但它的起点为0与rgmii_rxc同步,周期相同。

############################################################

# RX Clock period Constraints (per instance) #

############################################################

# Receiver clock period constraints: please do not relax

set rx_clk [get_clocks -of [get_ports rgmii_rxc]]############################################################

# Obtain input clocks from top level XDC #

############################################################

set ip_gtx_clk [get_clocks -of_objects [get_ports gtx_clk]]

#BLOCK CONSTRAINTS

############################################################

# For Setup and Hold time analysis on RGMII inputs #

############################################################# define a virtual clock to simplify the timing constraints

create_clock -name [current_instance .]_rgmii_rx_clk -period 8.000

set rgmii_rx_clk [current_instance .]_rgmii_rx_clk# Identify RGMII Rx Pads only.

# This prevents setup/hold analysis being performed on false inputs,

# eg, the configuration_vector inputs.set_input_delay -clock [get_clocks $rgmii_rx_clk] -max -1 [get_ports {rgmii_rxd[*] rgmii_rx_ctl}]

set_input_delay -clock [get_clocks $rgmii_rx_clk] -min -2.5 [get_ports {rgmii_rxd[*] rgmii_rx_ctl}]

set_input_delay -clock [get_clocks $rgmii_rx_clk] -clock_fall -max -1 -add_delay [get_ports {rgmii_rxd[*] rgmii_rx_ctl}]

set_input_delay -clock [get_clocks $rgmii_rx_clk] -clock_fall -min -2.5 -add_delay [get_ports {rgmii_rxd[*] rgmii_rx_ctl}]set_false_path -rise_from [get_clocks $rgmii_rx_clk] -fall_to $rx_clk -setup

set_false_path -fall_from [get_clocks $rgmii_rx_clk] -rise_to $rx_clk -setup

set_false_path -rise_from [get_clocks $rgmii_rx_clk] -rise_to $rx_clk -hold

set_false_path -fall_from [get_clocks $rgmii_rx_clk] -fall_to $rx_clk -holdset_multicycle_path -from [get_clocks $rgmii_rx_clk] -to $rx_clk -setup 0

set_multicycle_path -from [get_clocks $rgmii_rx_clk] -to $rx_clk -hold -1############################################################

# For Setup and Hold time analysis on RGMII outputs #

############################################################create_generated_clock -name [current_instance .]_rgmii_tx_clk -divide_by 1 -source [get_pins {rgmii_interface/rgmii_txc_ddr/C}] [get_ports rgmii_txc]

set rgmii_tx_clk [current_instance .]_rgmii_tx_clkset_output_delay 0.55 -max -clock [get_clocks $rgmii_tx_clk] [get_ports {rgmii_txd[*] rgmii_tx_ctl}]

set_output_delay -0.7 -min -clock [get_clocks $rgmii_tx_clk] [get_ports {rgmii_txd[*] rgmii_tx_ctl}]

set_output_delay 0.55 -max -clock [get_clocks $rgmii_tx_clk] [get_ports {rgmii_txd[*] rgmii_tx_ctl}] -clock_fall -add_delay

set_output_delay -0.7 -min -clock [get_clocks $rgmii_tx_clk] [get_ports {rgmii_txd[*] rgmii_tx_ctl}] -clock_fall -add_delayset_false_path -rise_from $ip_gtx_clk -fall_to [get_clocks $rgmii_tx_clk] -setup

set_false_path -fall_from $ip_gtx_clk -rise_to [get_clocks $rgmii_tx_clk] -setup

set_false_path -rise_from $ip_gtx_clk -rise_to [get_clocks $rgmii_tx_clk] -hold

set_false_path -fall_from $ip_gtx_clk -fall_to [get_clocks $rgmii_tx_clk] -holdset_multicycle_path -from $ip_gtx_clk -to [get_clocks $rgmii_tx_clk] 0 -setup

set_multicycle_path -from $ip_gtx_clk -to [get_clocks $rgmii_tx_clk] -1 -hold

6293

6293

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?