导读:苹果(Apple)刚刚发布的iPhone12pro max将dTOF技术带进手机应用,再次激起社会各界对3D感知成像技术的广泛关注。而作为3D感知模组的两个重要模块(发射端、接受端)之一的发射端——垂直腔面半导体激光器(VCSEL),重新被大众所瞩目。

与此同时,我们脑海里不禁闪现出种种疑问:何谓激光?何谓半导体激光器?亦何谓之垂直腔面半导体激光器?所以,本文将从“何谓激光”切入,进而到半导体激光器,最后揭开垂直腔面半导体激光器的神秘面纱。

Ⅰ 何谓激光

激光,即受激辐射光放大( Light Amplification by Stimulated Emission of Radiation),追根溯源,其发明得益于1916年爱因斯坦对原子受激辐射与自发辐射关系的系统阐述而形成的著名爱因斯坦关系式,基于此理论激光器被快速发明。激光是20世纪以来继核能、电脑、半导体之后,人类的又一重大发明,因具有单色性好、发散角极小、高亮度、相干性好的特性而广泛应用于各行各业。那么,形成激光需要满足三个必要条件:

(1) 泵浦源:把能量供给低能级的电子,激发使其成为高能级电子,能量供给的方式有电荷放电、光子、化学作用等;

(2) 增益介质:被激发、释放光子的电子所在的物质,其物理特性会影响所产生激光的波长等特性。

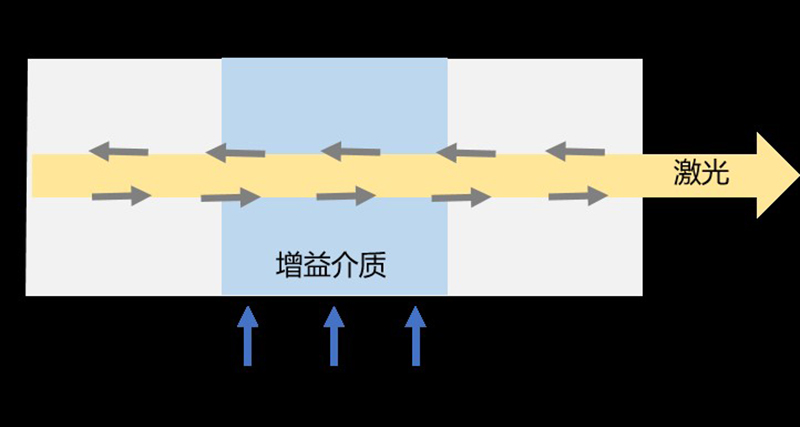

(3) 光学谐振腔:是两面互相平行的镜子,一面全反射,一面半反射。作用是把光线在反射镜间来回反射,目的是使被激发的光多次经过增益介质以得到足够的放大,当放大到可以穿透半反射镜时,激光便从半反射镜发射出去。因此,此半反射镜也被称为输出耦合镜(Output Coupler)。两镜面之间的距离也对输出的激光波长有着选择作用,只有在两镜间的距离能产生共振的波长才能产生激光(如图1)。

图1 激光器原理示意图

Ⅱ半导体激光器

半导体激光器是采用半导体材料作为工作物质的激光器,将载流子注入半导体PN结,从而产生的大量电子与空穴复合,进而形成受激辐射。在晶体的解理面端点处的反射而形成光学谐振腔从而不断增益形成激光。具有体积小、寿命长,并可采用简单的注入电流的方式来泵浦等优点。

与其他种类激光器一致,半导体激光器同样需要满足上面所提到的三个基本条件。通过对半导体异质结施加正向偏压,向有源区注入载流子来实现处在高能态导带底的电子数大于处于低能态价带顶的空穴数目即粒子数反转;对于光学谐振腔可以利用晶体的[110]面作为自然解理面来形成F-P腔而实现光学谐振,谐振腔的长度需满足所发射激光半波长的整数倍;泵浦注入需要足够强使得光增益等于或大于各种损耗之和以实现激光稳定振荡输出。根据出光方向的不同,我们可以将半导体激光体分为两大类,出光方向平行于衬底表面的边发射激光器(EEL)以及我们今天所介绍的主角——出光方向垂直于衬底表面的垂直腔面发射激光器(VCSEL)。

Ⅲ 垂直腔面发射激光器(VCSEL)

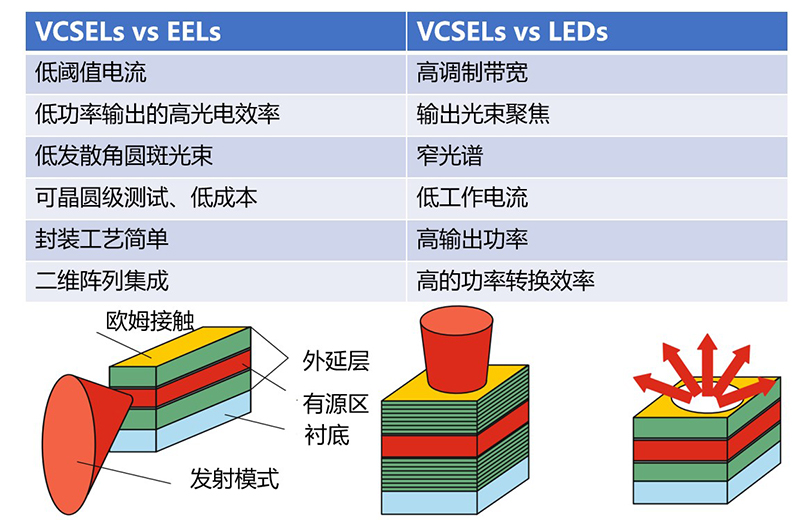

1977 年日本东京工业大学 Iga教授首次提出了垂直腔面发射激光器(vertical-cavity surface-emitting laser,简称 VCSEL)的概念。相比于EEL,VCSEL具有易集成、光束质量好、调制带宽高、寿命长、单模输出等优点(如图2)。广泛应用于光通信、 激光医疗、工业加工、 激光显示、 激光指示、 激光传感、 航空国防、安全防护等领域。随着高端制造业、 智慧城市、智能家居、智能手机虚拟现实、增强现实和智能驾驶等领域的快速发展, VCSEL的应用领域将进一步拓展。

图2 VCSEL与EEL&LED优势对比

1 VCSEL结构原理

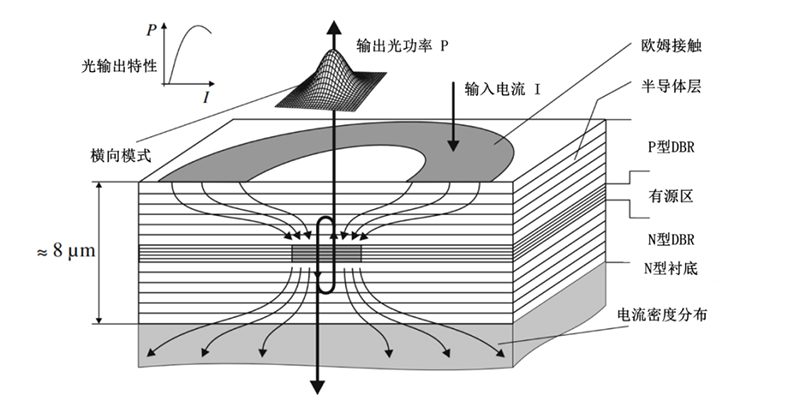

VCSEL的基本结构如图3所示,自上而下包括P型欧姆接触电极、P型掺杂的分布式布拉格反射镜(Distributed Bragg Reflector,DBR)、氧化限制层、多量子阱有源区、N型掺杂DBR、衬底以及N型欧姆接触电极。量子阱有源区位于n型掺杂和p型掺杂的DBR之间。DBR反射镜具有大于99%的反射率。有源区的光学厚度为1/2激光波长的整数倍,通过P-contact向有源区注入电流并产生受激辐射的光子在DBR中往复被反射并谐振放大,从而形成激光。

图3 VCSEL结构原理示意图

其中,DBR作为谐振腔的反射镜,由高低折射率介质或半导体材料交替外延生长而成,每层材料的光学厚度为激光波长的1/4。采用薄膜干涉与反射相变原理,当光穿过一层薄膜时,会在上下表面发生两次反射,薄膜的厚度会影响两次反射的光程差,如果控制薄膜的厚度为(1/4+N)波长的整数倍,则两次反射的光程差为(1/2+2N),光程差对应180°的相变,所以上下界面两次反射最终同相,叠加增强即增加了总体的反射系数;高低折射率介质或半导体材料交替外延生长,光有光密介质射向光疏介质在界面亦会发生180°的相变,所以光经过每层DBR都会增加一定的反射系数。对于光出射面DBR通过适当的减小其层数获得较小的反射系数而保证激光透过而射出。

2 VCSEL设计律

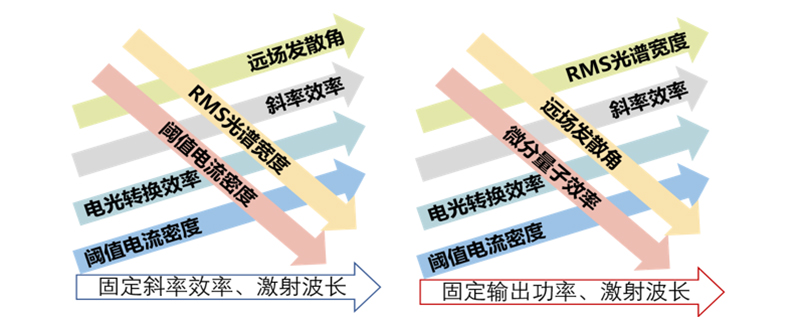

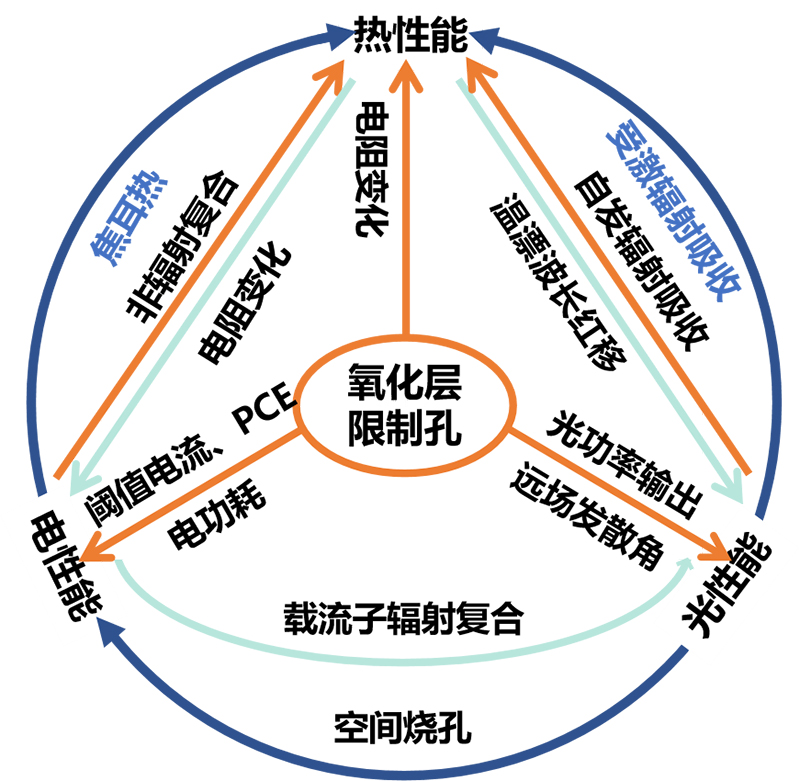

VCSEL的设计需要从整体考量,包括电学性能、光学性能、热学性能、可靠性四大方面的因素。其中,电学性能包括输出功率、阈值电流密度、微分量子效率、电光转换效率、斜率效率等;光学性能包括激射波长、远场发散角、RMS光谱宽度等;热学性能包括温漂系数、工作温度范围等;可靠性包括寿命、一致性等。以上各个参量之间相互关联,此消彼长。所以要获得一款完美的VCSEL几乎不可能,我们往往会根据既定基础参数以及实际应用需求设计”性能”价比更高的产品。

图4 VCSEL性能参数设计

3 VCSEL工艺过程

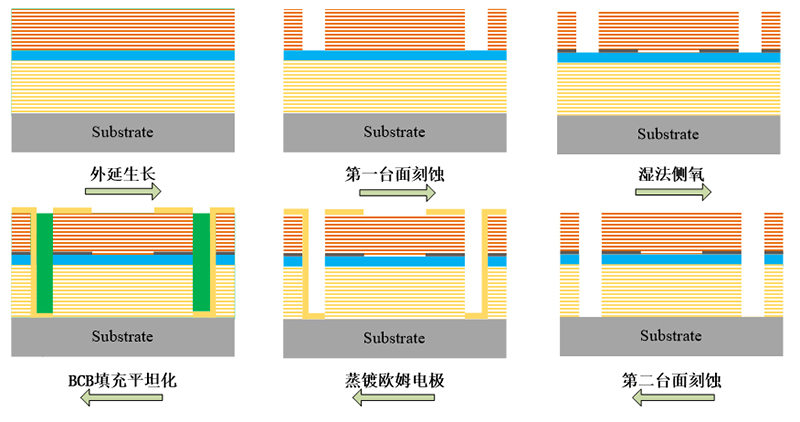

VCSEL的整个工艺过程可以分为两大部分,外延生长和芯片制程,其中外延工艺至关重要,外延结构的优劣基本决定了VCSEL器件的性能,目前各大厂家一般采用MOCVD的方式进行生长,总厚度约8-10um,全结构共200多层,一般先生长每一种单层,通过各种测试设备确定单层的质量、组分、载流子浓度和生长速率等后再进一步外延整个结构。因为各层参数的变化,例如DBR层数、掺杂浓度或者有源区的异质面结构的改变都会对整体VCSEL的特性有比较大的影响。

图5 VCSEL芯片制程工艺过程

VCSEL芯片制程基本为常规的半导体工艺制程,包括光刻、刻蚀、沉积等工艺基本工艺流程(如图5),通过侧氧工艺制作氧化限制孔, 侧氧工艺为VCSEL芯片制程中比较重要的一步,也是难点工艺,因为氧化限制孔的工艺参数牵动着VCSEL的光参数、电参数以及热参数(如图6)。侧氧工艺基本原理为VCSEL中的高 Al 组分层(如Al0.98Ga0.02As 和 Al As)在高温湿法氧化中被氧化成 Al2O3。高Al组分层(折射率~3)被氧化成 Al2O3(折射率~1.6)后,氧化区和非氧化区之间存在有效折射率差从而起到一定光限制作用。氧化限制层的横向结构形状通常为圆形,所以VCSEL的光斑基本为圆形。

图6 VCSEL氧化限制层相关机理

4 3D成像技术对VCSEL的需求

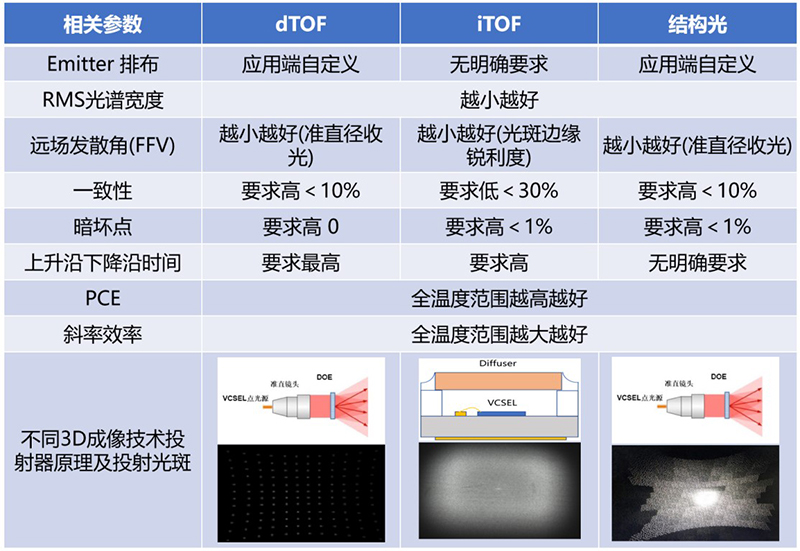

上面主要介绍了VCSEL的前世今生、基本原理以及生产工艺,那么在3D传感领域对于VCSEL的性能、稳定性有哪些要求呢,小编将从光电转换效率(PCE)、波长、上升下降沿时间等参数进行总结与对比(如图7)。

图7 不同3D成像技术对VCSEL需求对比表(图片来自网络)

总之,VCSEL是实现大规模并行光处理所必须的器件,在3D传感特别是在消费级应用的加持下,VCSEL会在半导体激光技术中取得重大突破并拓展到更多的应用领域。

参考:[1] VCSELs: Fundamentals, Technology and Applications of Vertical-Cavity Surface-Emitting Lasers 2013.

2166

2166

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?