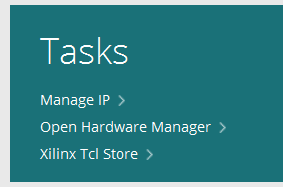

1.以manage ip的方式创建

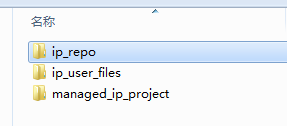

Tools>create and package...,配置该IP 的名称,并且选择该IP 的保存路径。默认的IP 核存放路径与manage IP 的工程路径是一个层次。

建议以后养成习惯:专门建一个manage IP工程,在此工程下Tools>create and package...且选择IP路径时,在ip_repo下新建一个文件夹,即每个IP单独一个文件夹,便于管理。

2.封装时选择edit ip

【注意】这里一定要选择“Edit IP”,否则,软件只是生成了框架文件,而不会创建一个关于IP 核的工程,这样对于IP 核的进一步设计很不利,虽然可以人为创建一个工程将相应的文件加入,但是这个需要更强的经验。所以强烈建议这一步选择“Edit IP”。

3.封装前先综合

跟纯PL 开发流程类似,代码写完了,要运行综合,检查编写的代码是否能够综合成功。 避免IP加到新工程中综合实现时才报错。

4.merge change

因为我们修改了软件自动生成的两个文件,软件认为会对Customization Parameters 页面,Ports and Interfaces 页面,Customization GUI 页面等产生影响,因此显示图标如下:

相关的页面左侧图标标识有修改标记,右上方也有提示更新的操作入口。

在任何一个页面点击上面的更新操作,其他页面也会同步更新。除非更新所涉及到的文件跟其他页面无关。更新成功后,显示图标变为绿色对勾。

【注意】如果修改代码后,这些页面不更新,说明你是直接打开的IP 核工程文档,而不是在Manage IP 模式下。

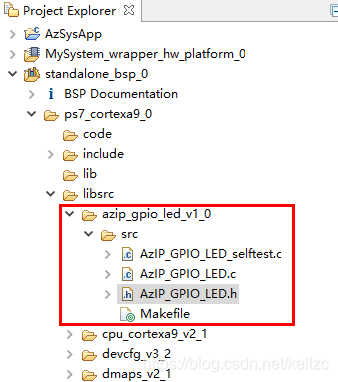

5.向导生成的IP有对应的测试文件和h文件

用户自定义IP 的驱动程序框架也是由向导生成的,开打BSP 工程的libsrc,可以看到添加的模块驱动文件。

本文详细介绍IP核的创建、编辑、综合、更新及测试流程,包括使用manageIP方式创建IP,选择EditIP进行编辑,封装前综合代码,以及如何处理mergechange。同时,文章还提到了向导生成的IP核包含测试文件和h文件。

本文详细介绍IP核的创建、编辑、综合、更新及测试流程,包括使用manageIP方式创建IP,选择EditIP进行编辑,封装前综合代码,以及如何处理mergechange。同时,文章还提到了向导生成的IP核包含测试文件和h文件。

1076

1076