补发

阻塞赋值 =

非阻塞赋值 <= 只能用于寄存器类型变量进行赋值

module blocking

module blocking

(

input wire sys_clk,

input wire sys_rst,

input wire [1:0] in,

output reg [1:0] out

);

reg [1:0] in_reg; //方便在波形上观察延迟一拍效果

always@(posedge sys_clk or negedge sys_rst)

if(sys_rst == 1'b0)

begin

in_reg=1'b0;

out=1'b0;

else

begin

in_reg = in;

out =in_reg;

endmodule

tb_blocking

`timescale 1ns/1ns

module tb_blcoking();

reg sys_clk;

reg sys_rst;

reg in;

wire out;

initial

begin

sys_clk <= 1'b1;

sys_rst <= 1'b0;

#10

sys_rst <= 1'b1;

#210

sys_rst <= 1'b0;

#40

sys_rst <= 1'b1;

end

always #10 sys_clk <= ~sys_clk;

always #10 on <= {$random}%4;

blockong blocking_inst

(

.sys_clk(sys_clk),

.sys_rst(sys_rst),

.in(in),

.out(out)

);

endmodule

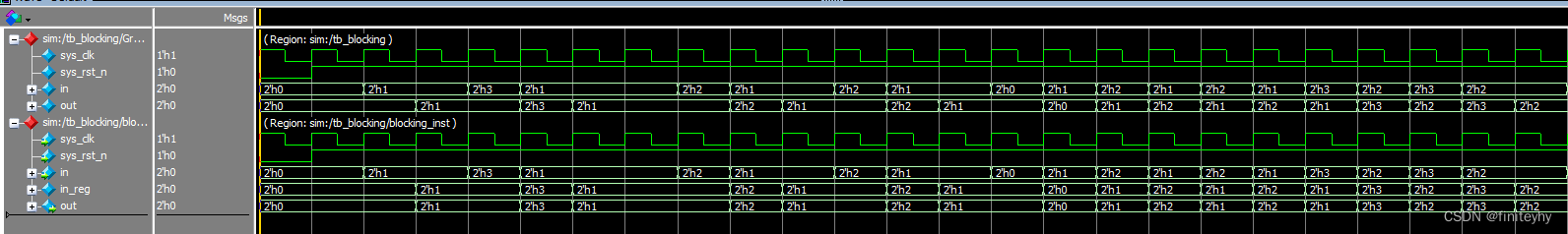

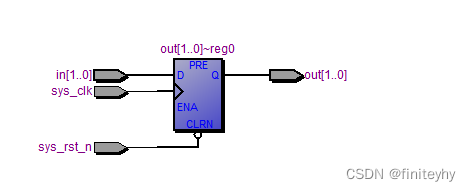

RTL视图

out与in一个寄存器 延迟一拍

非阻塞赋值

module blocking

(

input wire sys_clk,

input wire sys_rst,

input wire [1:0] in,

output reg [1:0] out

);

reg [1:0] in_reg; //方便在波形上观察延迟一拍效果

always@(posedge sys_clk or negedge sys_rst)

if(sys_rst == 1'b0)

begin

in_reg=1'b0;

out=1'b0;

else

begin

in_reg <= in;

out <=in_reg;

endmodule

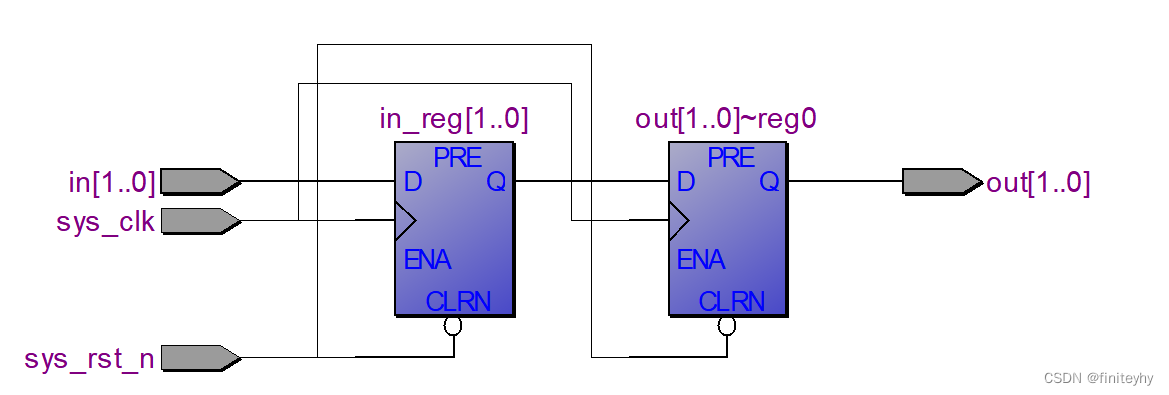

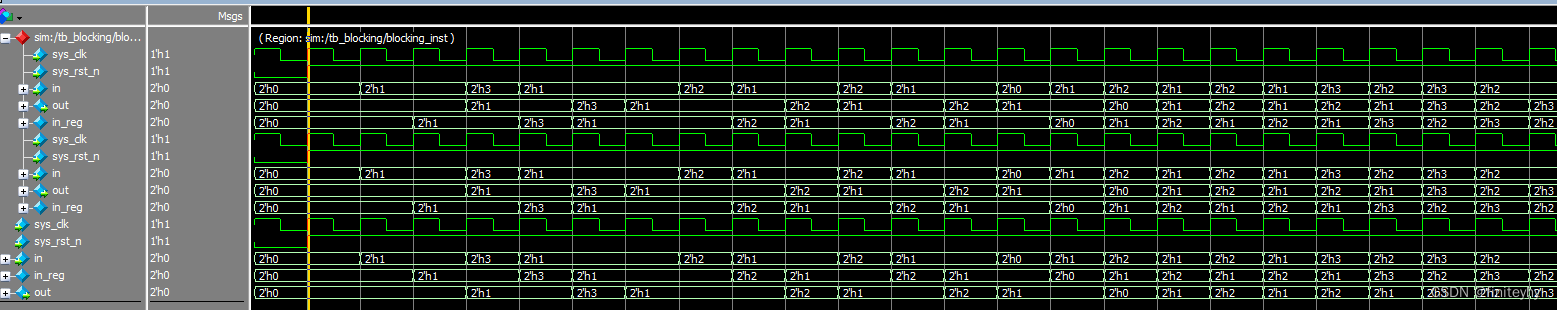

RTL视图

out延迟in两拍,非阻塞赋值,in_reg延迟in一拍,out延迟in_reg一拍

本文探讨了在Verilog设计中,阻塞和非阻塞赋值的区别,以及它们如何影响寄存器之间的延迟。通过实例展示了阻塞赋值导致的延迟为一拍,而非阻塞赋值则延迟两拍,强调了在实时系统中的同步作用。

本文探讨了在Verilog设计中,阻塞和非阻塞赋值的区别,以及它们如何影响寄存器之间的延迟。通过实例展示了阻塞赋值导致的延迟为一拍,而非阻塞赋值则延迟两拍,强调了在实时系统中的同步作用。

1104

1104

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?