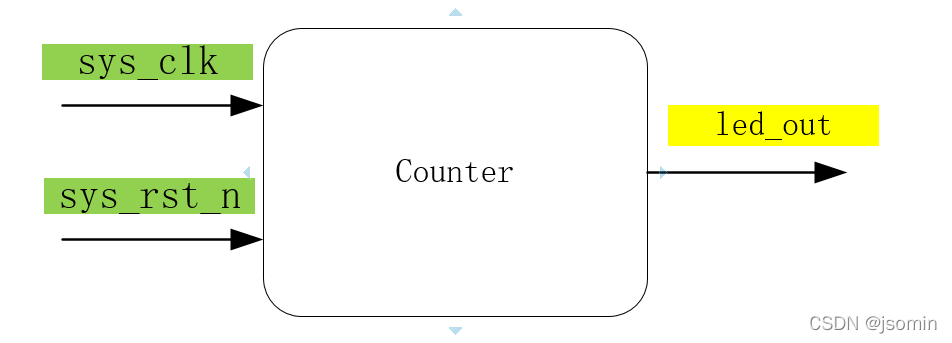

计数器结构

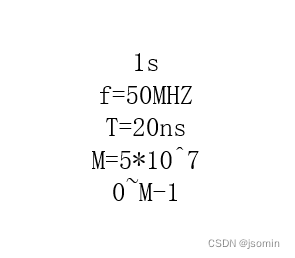

时钟频率为50MHz

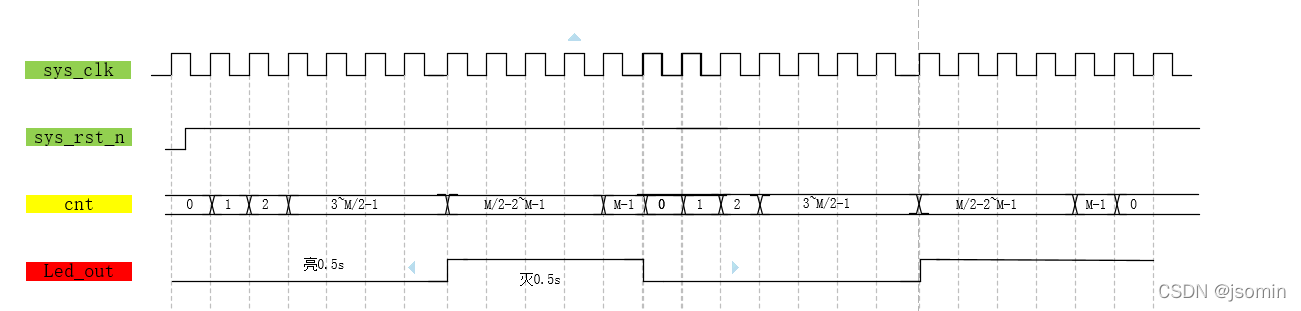

需要计数到M-1,波形图

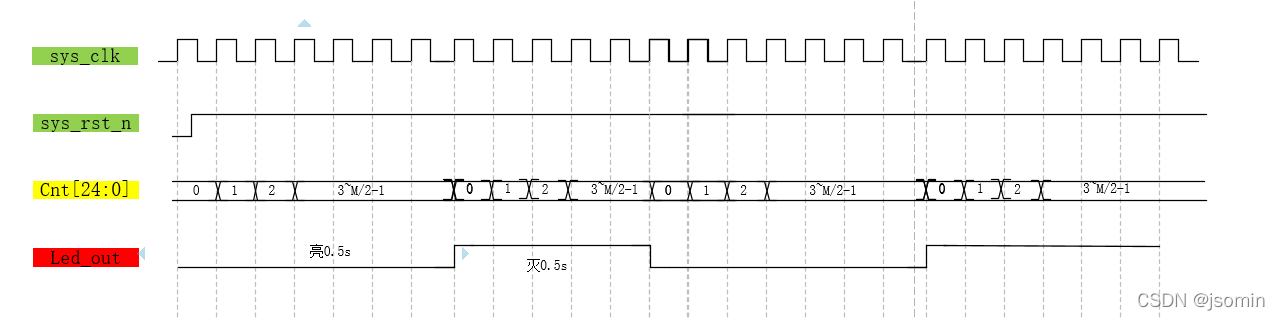

如果计数到M/2-1,波形图

两种区别在于计数器的位宽,计数到M/2-1需要用到的位宽比M-1少一位,更可以节约资源。

`timescale 1ns/1ns

module tb_counter();

reg sys_clk,

reg sys_rst_n,

wire led_out;

initial

begin

sys_clk = 1'b1;

sys_rst_n <=1'b0;

#20

sys_rst_n <= 1'b1;

end

always #10 sys_clk = ~sys_clk;

initial

begin

$timeformat(-9,0,"ns",6);

$moni

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2611

2611

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?