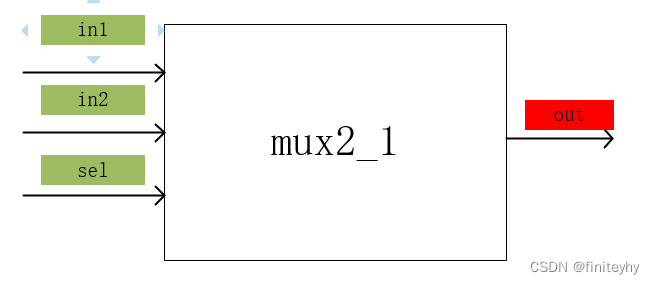

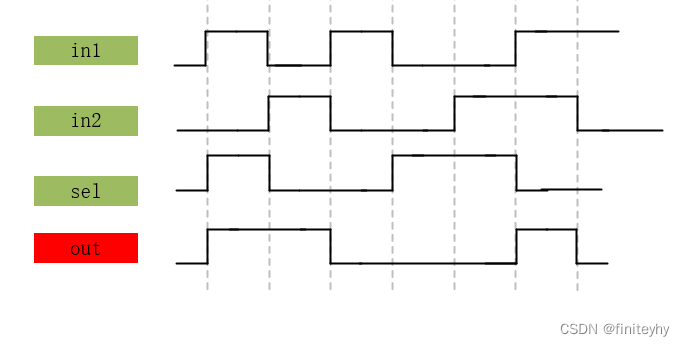

当位选信号sel为高电平,输出in1,低电平输出in2

module mux2_1

module mux2_1

(

input wire in1,

input wire in2,

input wire sel,

output wire out

);

case(sel):

1'b1: out <= in1;

1'b0: out <= in2;

default: out<=in1;

endcase

endmodule

module tb_mux2_1

module mux2_1();

wire in1;

wire in2;

wire sel;

wire out;

initial

begin

in1 <=1'b0;

in2 <=1'b0;

sel <=1'b0;

end

always #10 in1 <= {$random}%2;

always #10 in2 <= {$random}%2;

always #10 sel <= {$random}%2;

mux2_1 mux2_1_inst

(

.in1(in1),

.in2(in2),

.sel(sel),

.out(out)

)

endmodule

该博客介绍了使用Verilog语言实现2:1数据选择器(MUX)的过程。通过case语句,当选择信号sel为高电平时,输出in1,为低电平时输出in2。同时,提供了测试平台tb_mux2_1,用于随机改变输入和选择信号,验证模块的正确性。

该博客介绍了使用Verilog语言实现2:1数据选择器(MUX)的过程。通过case语句,当选择信号sel为高电平时,输出in1,为低电平时输出in2。同时,提供了测试平台tb_mux2_1,用于随机改变输入和选择信号,验证模块的正确性。

3895

3895

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?