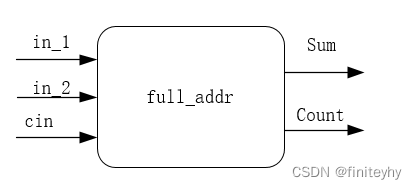

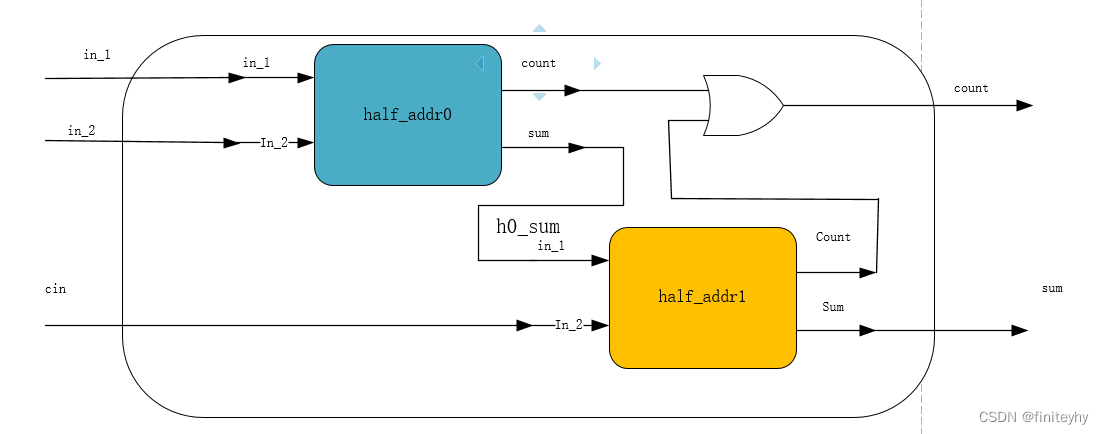

模块化 调用半加器模块 在全加器模块中对两个半加器分别进行实例化

用两个半加器实现全加器 ,用或门连接两个进位信号

module full_addr

module full_addr

(

input wire in1,

input wire in2,

input wire cin,

output wire sum,

output wire count

);

wire h0_sum;

wire h0_count;

wire h1_count;

half_addr half_addr_inst0

(

.in1(in1),

.in2(in2),

.sum(h0_sum),

.count(h0_count)

);

half_addr half_addr_inst1

(

.in1(h0_sum),

.in2(cin),

.sum(sum),

.count(h1_count)

);

assign count=(h0_count | h1_count)

endmodulemodule tb_full_addr

module tb_full_addr();

reg in1;

reg in2;

reg cin;

wire sum;

wire count;

initial

begin

i

该博客介绍了如何使用Verilog语言设计一个全加器模块,通过实例化两个半加器并用或门连接进位信号来实现。在全加器模块`full_addr`中,输入包括两个二进制数`in1`和`in2`以及进位输入`cin`,输出为和`s`和进位输出`count`。同时,提供了测试平台`tb_full_addr`来验证全加器的功能,通过随机改变输入信号并观察输出,确保设计正确无误。

该博客介绍了如何使用Verilog语言设计一个全加器模块,通过实例化两个半加器并用或门连接进位信号来实现。在全加器模块`full_addr`中,输入包括两个二进制数`in1`和`in2`以及进位输入`cin`,输出为和`s`和进位输出`count`。同时,提供了测试平台`tb_full_addr`来验证全加器的功能,通过随机改变输入信号并观察输出,确保设计正确无误。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

321

321

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?