混合信号 PCB 布局中,“干扰” 是最常见的问题 —— 即使遵循基础原则,也可能因 “参数把控不当”“细节疏忽” 出现串扰超标、地弹过大、电源噪声干扰等问题,这些问题会直接导致模拟信号失真、数字信号码错,甚至系统崩溃。今天,我们针对三大核心干扰问题,分析 “产生原因、解决方案与预防措施”,结合实际案例,帮你快速定位并解决问题。

一、常见问题 1:串扰超标 —— 模拟线与数字线耦合干扰

问题表现:示波器测量模拟信号时,出现与数字信号同步的噪声(如模拟信号上叠加 100MHz 时钟噪声),串扰幅值 > 5mV(模拟信号幅值通常 < 100mV),导致信号信噪比(SNR)<50dB(设计要求≥60dB)。

1. 核心原因

-

布线间距不足:模拟线与数字线间距未满足 “3 倍线宽原则”,甚至平行布线长度 > 10mm,电容耦合与电感耦合增强;例如,模拟线宽 0.2mm,数字线宽 0.2mm,间距 0.3mm(未达 0.6mm),平行布线 20mm,串扰幅值可达 8mV;

-

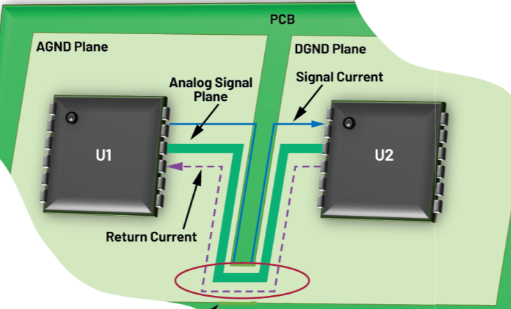

信号层规划不当:多层板中,模拟信号层与数字信号层未隔接地平面,导致层间耦合;例如,6 层板中模拟层(顶层)与数字层(内层 1)相邻,无接地层隔离,串扰幅值比隔接地层时增加 3 倍;

-

数字信号边沿速率过快:数字信号边沿速率(如上升时间 < 1ns)越快,高频分量越丰富,辐射能力越强,串扰越严重;例如,1GHz 时钟信号(上升时间 0.5ns)比 100MHz 时钟信号(上升时间 5ns)的串扰幅值大 5 倍。

2. 解决方案

-

调整布线间距与走向:若串扰幅值 <10mV,可增大模拟线与数字线的间距(如从 0.3mm 增至 0.8mm),或缩短平行布线长度(如从 20mm 减至 5mm);例如,某工业 PCB 模拟线与数字线间距从 0.3mm 增至 0.6mm 后,串扰幅值从 8mV 降至 2mV;若串扰幅值> 10mV,需改变布线走向,避免平行(采用垂直交叉布线),交叉处间距≥1mm;

-

增加屏蔽与接地平面:在模拟线两侧布接地铜箔(连接至模拟地),形成 “双线屏蔽”,或在多层板中增加模拟地平面(位于模拟层下方),隔离数字层;例如,某医疗 PCB 在模拟线两侧加屏蔽后,串扰幅值从 12mV 降至 1mV;

-

减缓数字信号边沿速率:通过数字芯片配置(如 MCU 的 GPIO 输出模式)或串接阻尼电阻(如在时钟线串接 22Ω 电阻),减缓信号上升 / 下降时间(如从 0.5ns 增至 1ns),减少高频分量;需注意:边沿速率不可过慢,避免影响数字信号时序(如时序裕量≥20%)。

3. 预防措施

-

布局初期规划 “模拟布线通道” 与 “数字布线通道”,避免两类线路交叉或平行;

-

多层板设计时,确保模拟信号层与数字信号层之间隔接地平面;

-

选择边沿速率匹配需求的数字芯片(如无需高速通信时,选上升时间 > 1ns 的芯片),避免过度设计。

二、常见问题 2:地弹过大 —— 接地网络设计不当

问题表现:示波器测量模拟地与数字地之间的电位差(地弹电压)>100mV(设计要求≤50mV),模拟信号随数字信号的开关同步波动,例如 MCU 执行指令时,模拟传感器信号出现 5% 的波动。

1. 核心原因

-

多点共地:模拟地与数字地在多个节点连通(如 ADC 处与电源入口处均共地),形成闭合回路,数字电流在回路中产生地环流,导致地弹;例如,数字电流 1A,回路电阻 0.1Ω,地弹电压可达 0.1V;

-

接地铜箔过窄:模拟地或数字地铜箔线宽 <0.3mm,接地电阻过大(>0.5Ω),数字电流流过时产生压降,形成地弹;例如,数字地铜箔线宽 0.2mm,长度 10mm,电阻约 0.2Ω,数字电流 0.5A 时,地弹电压达 0.1V;

-

数字电路开关电流过大:数字芯片(如功率驱动芯片、高速 MCU)的开关电流 > 1A,在接地网络中产生较大压降,导致地弹;例如,电机驱动芯片的开关电流 2A,接地电阻 0.1Ω,地弹电压可达 0.2V。

2. 解决方案

-

改为单点共地:拆除多余的共地节点,仅保留一处共地(如 ADC 处或电源入口处),消除闭合回路与地环流;例如,某工业 PCB 原在 ADC 与电源入口两处共地,地弹 0.15V;改为仅在 ADC 处单点共地后,地弹降至 0.03V;

-

加宽接地铜箔:将模拟地与数字地铜箔线宽增至≥0.5mm(多层板采用接地平面,电阻 < 0.01Ω),减少接地电阻;例如,数字地铜箔从 0.2mm 加宽至 0.6mm 后,电阻从 0.2Ω 降至 0.05Ω,地弹从 0.1V 降至 0.025V;

-

降低数字开关电流:选用低功耗数字芯片(如 MCU 选 STM32L 系列,工作电流 < 10mA),或在数字电路中加电流限制电阻(如功率驱动芯片前串接 1Ω 电阻),减少开关电流;例如,电机驱动芯片的开关电流从 2A 降至 1A 后,地弹从 0.2V 降至 0.1V。

3. 预防措施

-

接地网络设计时,明确单点共地位置,避免多点连通;

-

多层板优先采用接地平面(而非走线),单层 / 双层板需保证接地铜箔宽≥0.5mm;

-

选型时评估数字芯片的开关电流,避免超过接地网络的承载能力。

三、常见问题 3:电源噪声干扰 —— 电源滤波与隔离不足

问题表现:示波器测量模拟电源电压时,出现高频噪声(如 100MHz-1GHz 的尖峰噪声),噪声幅值 > 50mV(设计要求≤20mV),模拟电路输出信号失真(如运放输出出现高频纹波)。

1. 核心原因

-

电源未隔离:模拟电源与数字电源共用同一电源模块(如同一 LDO),数字电路的开关噪声通过电源传导至模拟电路;例如,数字电源的 100MHz 噪声通过 LDO 耦合至模拟电源,幅值达 80mV;

-

滤波元件选型或布局不当:模拟电源仅加 0.1μF 陶瓷电容(仅滤除 > 100MHz 高频噪声),未加低频滤波电容(如 10μF 电解电容),低频噪声(1kHz-1MHz)未被抑制;或滤波电容远离电源引脚(距离 > 10mm),电源线寄生电感削弱滤波效果;

-

电源布线不合理:模拟电源布线与数字电源布线平行且间距 <2mm,耦合噪声;或模拟电源布线过长(>50mm),寄生电感增大,噪声更容易叠加。

2. 解决方案

-

独立电源与隔离:为模拟电路与数字电路配置独立电源模块(如模拟用低噪声 LDO,数字用普通 LDO),或在共用电源中加电源隔离芯片(如 TI 的 ISO7740),阻断噪声传导;例如,某医疗 PCB 原共用 LDO,模拟电源噪声 80mV;改为独立低噪声 LDO 后,噪声降至 15mV;

-

优化滤波设计:模拟电源采用 “多级滤波”(如 100μF 电解电容 + 10μF 钽电容 + 0.1μF 陶瓷电容),覆盖低频至高频噪声;滤波电容紧贴电源引脚(距离≤3mm),减少寄生电感;例如,某工业 PCB 在模拟电源加 100μF+0.1μF 电容,且距离引脚 2mm,噪声从 60mV 降至 18mV;

-

调整电源布线:模拟电源布线与数字电源布线间距≥3mm,避免平行布线;缩短模拟电源布线长度(≤30mm),线宽≥0.5mm,减少寄生电感;例如,模拟电源布线从 60mm 减至 20mm 后,噪声从 55mV 降至 22mV。

3. 预防措施

-

电源设计初期规划独立的模拟电源与数字电源,优先选用低噪声电源模块;

-

滤波电容按 “低频 + 高频” 组合选型,布局时紧贴电源引脚;

-

电源布线避开数字干扰源,控制长度与间距。

混合信号 PCB 的干扰问题多源于 “细节把控不足”,只要精准定位干扰路径,针对性调整布局、接地或滤波设计,就能有效解决问题,保障信号质量。

131

131

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?