混合信号 PCB 布局没有 “统一模板”,但需遵循 “分区隔离、接地优化、布线管控、元件布局合理” 四大核心原则 —— 这些原则是规避干扰、保障信号质量的关键,任何环节的疏忽都可能导致系统失效。

一、分区设计:明确 “模拟区” 与 “数字区”,物理隔离干扰

分区是混合信号 PCB 布局的 “第一步”,核心是将模拟电路与数字电路在 PCB 上划分独立区域,通过物理距离减少耦合干扰,具体需遵循 “明确边界、合理划分、隔离间距” 三个要点。

1. 明确分区边界

首先需在 PCB 设计软件(如 Altium Designer、Cadence)中划定 “模拟区” 与 “数字区” 的边界,边界需清晰且连续,避免两类电路交叉。例如,可沿 PCB 长边或短边划分直线边界,模拟区占 PCB 面积的 1/3-1/2(根据模拟电路规模调整),数字区占剩余面积。边界处可预留 “隔离带”(宽度 0.5-1mm,无铜无布线),进一步减少干扰耦合。

2. 按信号流向划分区域

分区需结合 “信号流向”,避免信号跨区折返。例如,工业传感器 PCB 的信号流向为 “传感器→运放(模拟放大)→ADC(模拟转数字)→MCU(数字处理)→通信模块(数字传输)”,布局时应按此顺序从左到右划分:左侧为模拟区(传感器、运放),中间为 “过渡区”(ADC,连接模拟与数字),右侧为数字区(MCU、通信模块)。若 ADC 放在数字区,模拟信号需跨区传输,会增加被干扰的风险。

3. 控制隔离间距

模拟区与数字区的最小间距需根据数字信号频率调整:数字信号频率 <100MHz 时,间距≥2mm;频率 100MHz-1GHz 时,间距≥3mm;频率> 1GHz 时,间距≥5mm。例如,MCU 时钟频率为 1GHz 时,模拟区与数字区间距若仅 2mm,耦合噪声可达 5mV,远超 mV 级模拟信号的耐受范围;增至 5mm 后,耦合噪声可降至 0.5mV 以下。

反例案例:某消费电子 PCB 将模拟音频电路(20Hz-20kHz)与数字蓝牙电路(2.4GHz)间距设为 1mm,导致音频输出出现明显杂音(噪声幅值 10mV);调整间距至 5mm 后,杂音消失,噪声降至 0.3mV。

二、接地设计:“独立接地,单点共地”,避免地环流

接地是混合信号 PCB 布局的 “核心难点”,错误的接地方式(如模拟地与数字地直接连通)会产生地环流,导致模拟信号失真。正确的接地原则是 “模拟地(AGND)与数字地(DGND)独立设计,单点共地”,具体需遵循三个要点。

1. 独立接地网络

在 PCB 布局时,需为模拟电路与数字电路设计独立的接地铜箔:模拟地仅连接模拟元件的接地引脚(如运放、传感器、ADC 的 AGND 引脚),数字地仅连接数字元件的接地引脚(如 MCU、通信芯片、存储器的 DGND 引脚),两类接地网络在 PCB 上不直接连通,避免数字电流流入模拟地。

2. 单点共地位置

模拟地与数字地需在 “单一节点” 连通(即单点共地),共地位置需选在 “干扰最小的区域”—— 通常为电源入口处或 ADC 芯片附近。例如,在电源入口处共地:模拟电源(如 3.3V_A)与数字电源(如 3.3V_D)均从总电源(如 5V)转换而来,总电源的接地端作为共地点,模拟地与数字地在此处汇合;在 ADC 附近共地:ADC 芯片同时有 AGND 与 DGND 引脚,可将两类接地网络在 ADC 的接地引脚处直接连通(需参考 ADC datasheet,部分芯片要求 AGND 与 DGND 短接)。

需避免 “多点共地”:若模拟地与数字地在多个节点连通,会形成闭合回路,数字电流在回路中产生地环流,导致模拟地电位波动。例如,某医疗 PCB 在 ADC 与电源入口两处共地,形成地环流,导致心电信号出现 50Hz 工频干扰;改为仅在 ADC 处单点共地后,干扰消失。

3. 接地铜箔设计

模拟地铜箔需 “完整、宽厚”,避免细窄走线(线宽≥0.5mm),减少接地电阻(模拟地电阻≤0.1Ω),防止地弹;数字地铜箔可适当窄些(线宽≥0.2mm),但需保证数字电流路径通畅。此外,模拟电路下方应尽量铺模拟地铜箔,形成 “屏蔽层”,减少外部辐射干扰。

三、元件布局:“靠近信号源,远离干扰源”

元件布局需围绕 “缩短信号路径、减少干扰耦合” 展开,具体遵循四个原则:

1. 敏感模拟元件远离数字干扰源

模拟电路中的敏感元件(如运放、传感器、ADC 的模拟输入端)需远离数字干扰源(如 MCU、时钟振荡器、功率开关管),最小间距需满足:与 MCU 间距≥3mm,与时钟振荡器间距≥5mm,与功率开关管间距≥10mm。例如,运放若靠近 100MHz 时钟振荡器(间距 2mm),会拾取时钟噪声,导致输出信号失真;增至 5mm 后,失真度从 5% 降至 0.1%。

2. 信号路径最短

模拟信号路径需尽可能短,避免长线传输(模拟信号线长度≤50mm,高频模拟信号≤20mm),减少信号衰减与干扰拾取。例如,温度传感器与运放的距离应≤10mm,若增至 30mm,信号衰减会从 0.5% 增至 5%,且易受干扰。

数字信号路径也需短,但优先级低于模拟信号 —— 若数字信号路径长,可通过阻抗匹配(如串接电阻)优化,而模拟信号路径长则难以通过后期优化弥补。

3. 滤波元件靠近电源引脚

模拟电路的电源滤波元件(如 10μF 电解电容 + 0.1μF 陶瓷电容)需紧贴模拟芯片的电源引脚(距离≤5mm),数字电路的滤波元件(如 0.1μF 陶瓷电容)需紧贴数字芯片的电源引脚(距离≤3mm),确保滤波效果。若滤波电容远离引脚(如 10mm),电源线的寄生电感会削弱滤波效果,电源噪声仍会进入芯片。

4. ADC 芯片 “跨区布局”

ADC 作为模拟与数字信号的接口,需 “跨模拟区与数字区布局”:ADC 的模拟输入端(如 Vin+、Vin-)放在模拟区,靠近运放;数字输出端(如 DOUT、SCLK)放在数字区,靠近 MCU;ADC 的 AGND 引脚接模拟地,DGND 引脚接数字地,两类接地在 ADC 处单点共地(需符合芯片要求)。这种布局可缩短模拟信号与数字信号的路径,减少跨区传输带来的干扰。

四、布线管控:“隔离、屏蔽、阻抗匹配”

混合信号 PCB 布线需严格控制 “模拟线与数字线的间距”“敏感线的屏蔽”“阻抗匹配”,具体规则:

1. 模拟线与数字线的间距

模拟信号线与数字信号线的最小间距需满足 “3 倍线宽原则”(间距≥3× 线宽),若数字信号频率 > 1GHz,需满足 “5 倍线宽原则”。例如,模拟线宽 0.2mm,数字线宽 0.2mm,二者间距需≥0.6mm;数字信号频率 1.5GHz 时,间距需≥1mm。

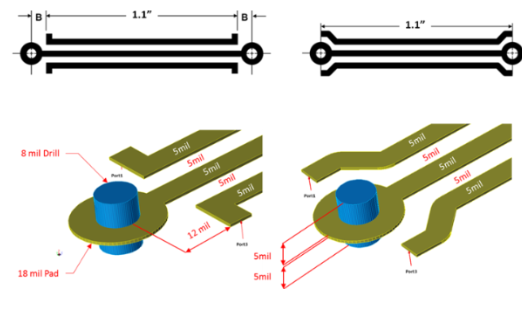

2. 敏感模拟线屏蔽

对于极敏感的模拟线(如 μV 级心电信号、nA 级电流信号),需采用 “屏蔽布线”:在模拟线两侧布接地铜箔(模拟地),形成 “双线屏蔽”,或在模拟线上方铺接地铜皮(需打孔连接至模拟地),形成 “立体屏蔽”。屏蔽层需与模拟地连通,且无断点,避免屏蔽失效。

3. 阻抗匹配

高频模拟信号(如射频信号)与高速数字信号(如 USB、PCIe)需做阻抗匹配:模拟射频线阻抗通常为 50Ω,数字差分线(如 USB4)阻抗通常为 100Ω,布线时需通过线宽、层间距控制阻抗(参考阻抗计算公式),避免信号反射。

混合信号 PCB 布局需 “先分区、再接地、后布线”,每个原则都需结合信号特性与干扰风险,才能实现 “模拟信号低失真、数字信号无干扰” 的目标。

131

131

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?