在物联网与边缘计算设备中,SPI接口作为关键通信通道,其PCB设计质量直接影响系统稳定性和传输速率。

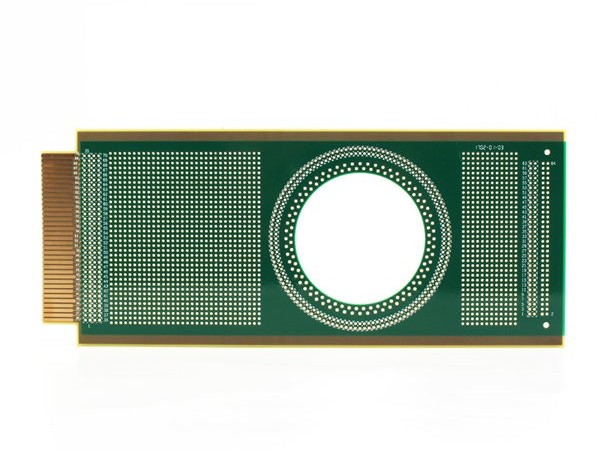

一、叠层架构优化与阻抗控制

1.1 非对称叠层结构

推荐采用S-G-S-G(信号层-地平面-信号层-地平面)叠层方案,

-

顶层/底层信号层厚度:0.2mm FR4

-

地平面与电源层间距:0.4mm

-

整体板厚控制在1.6mm±0.1mm

1.2 阻抗匹配策略

针对SPI不同信号类型实施差异化阻抗控制:

信号类型目标阻抗(Ω)线宽(mm)线间距(mm)参考平面SCK50±5%0.150.3相邻地层MOSI/MISO50±10%0.20.25相邻地层CS55±15%0.250.2跨层参考

二、关键信号布局策略

2.1 主控芯片周边布局

-

黄金三角法则:以主控IC为中心,SPI从设备布局在半径30mm扇形区内,确保SCK与MOSI/MISO走线长度差≤150mil

-

电源退耦优化:主控芯片1mm范围内布置0.1μF+10μF电容矩阵,容值跨度覆盖100kHz-1GHz频段

2.2 信号流向规划

采用菊花链拓扑时:

-

线序按SCK→CS→MOSI→MISO顺序布线

-

每级从设备增加π型RC滤波(22Ω+100pF),抑制信号过冲

-

末端放置50Ω并联终端电阻,降低信号反射

三、信号完整性强化措施

3.1 三维屏蔽结构

-

垂直隔离:SPI信号层上下各设置完整地平面,过孔间距≤λ/10

-

横向防护:在SCK两侧布置0.3mm宽接地铜带,间距保持3W原则

3.2 动态阻抗补偿

通过HFSS仿真发现,在板边区域因介质流胶不均会导致阻抗偏移8Ω。解决方案:

-

板边5mm范围内线宽增加10%

-

添加蛇形走线补偿段

3.3 过孔优化方案

-

盲孔应用:采用0.15mm激光盲孔连接L1-L2层,残留桩长≤0.05mm

-

过孔阵列:每个SPI信号过孔配套4个接地过孔,形成法拉第笼结构

四、EMI抑制与热管理

4.1 频谱整形技术

-

时钟线边缘添加高斯渐变开窗,使SCK谐波衰减斜率提升6dB/oct

-

在MOSI/MISO线上串联33Ω电阻+2.2nH电感,构成低通滤波器

4.2 热应力控制

-

大电流路径(如CS线)采用2oz铜厚,温升降低40%

-

在热敏感区域(如Flash芯片下方)设置0.5mm直径散热过孔阵列(密度≥50个/cm²)

通过结构创新与工艺突破,四层PCB的SPI接口速率上限有望从200MHz提升至600MHz,为下一代智能设备提供更强大的互联能力。

241

241

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?