Advanced Package Designer

1. 介绍

为了有效地设计这些复杂的软件包,需要一个复杂的实现工具来解决电气和物理约束。Cadence IC封装设计技术以其高效、灵活和可靠的密集、先进封装设计实现而在世界范围内得到认可。集成的信号和电源完整性分析可确保在整个设计周期内共同应对电气和物理挑战。使用Cadence IC封装设计技术,设计人员可以通过首次成功满足压缩的进度要求。

2. Cadence集成电路封装设计技术

集成电路封装是目前硅封装板设计流程中的一个关键环节。Cadence Allegro平台为PCB和复杂封装的设计和实施提供了完整且可扩展的技术。Cadence IC封装设计技术允许设计师优化复杂的单模和多模引线键合和倒装芯片设计,以实现降低成本和提升性能,同时还能满足较短的项目时间表。

这种约束驱动的行业标准技术支持系统规划、高级OSAT和基于铸造的封装设计,从单个模具到复杂系统。Cadence IC封装设计技术实现了高效的引线键合设计技术、约束感知基板互连设计以及详细的互连提取、建模和信号完整性/功率传输分析。

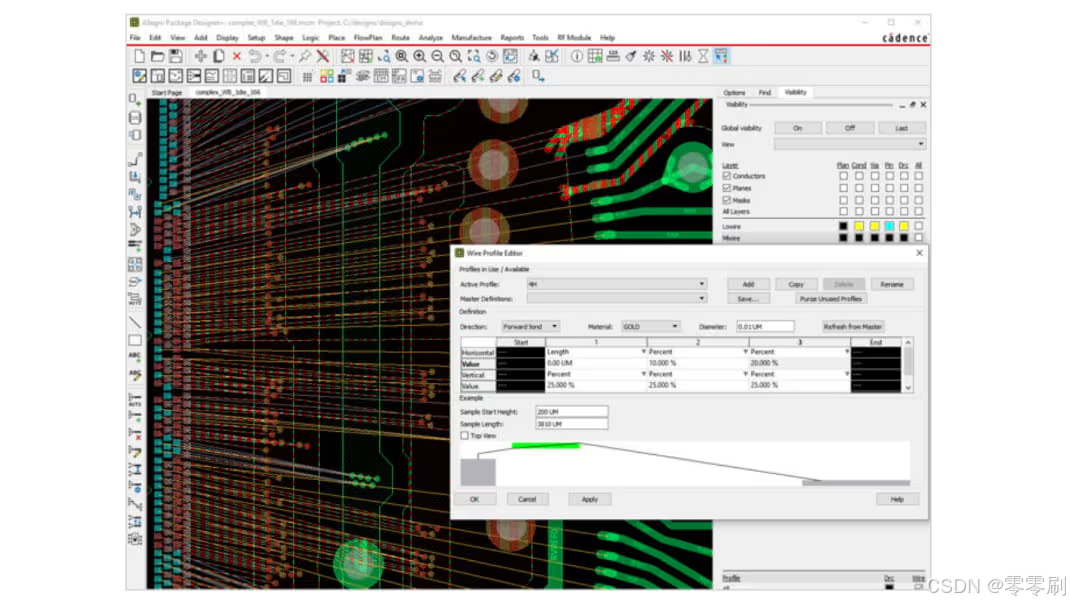

图 1 约束驱动的交互式引线键合包括跨多个号线层的推压

Cadence IC封装布局设计技术可用于多个不同的产品和层次,包括∶

- Allegro P

订阅专栏 解锁全文

订阅专栏 解锁全文

1082

1082