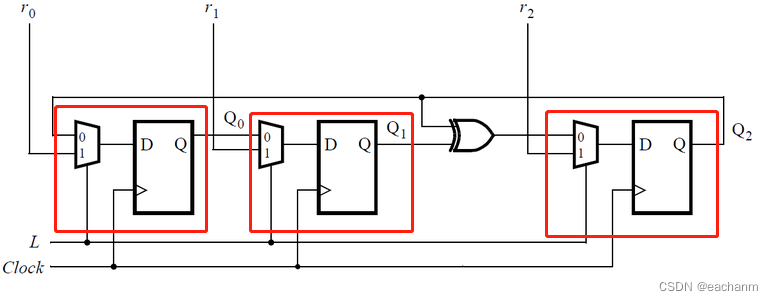

考虑下面的顺序电路:

假设您要为此线路实现分层 Verilog 代码,使用具有触发器和多路复用器的子模块的三个实例化。为此子模块编写一个名为 top_module 的 Verilog 模块(包含一个触发器和多路复用器)。

即写个子模块就行,2选1数据选择器和寄存器

module top_module (

input clk,

input L,

input r_in,

input q_in,

output reg Q);

always@ (posedge clk)

if(L)

Q <= r_in;

else

Q <= q_in;

endmodule

文章描述了一个使用Verilog编程的任务,要求创建一个名为top_module的模块,该模块包含一个触发器和一个2选1数据选择器。此模块基于输入信号L、r_in和q_in,在时钟上升沿更新输出Q。当L为高时,Q的值被设置为r_in,否则设置为q_in。

文章描述了一个使用Verilog编程的任务,要求创建一个名为top_module的模块,该模块包含一个触发器和一个2选1数据选择器。此模块基于输入信号L、r_in和q_in,在时钟上升沿更新输出Q。当L为高时,Q的值被设置为r_in,否则设置为q_in。

396

396

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?