分频:单个时钟周期变长,频率变小,若50Mhz实现2分频,则分频后为25Mhz

倍频:单个时钟周期变短,频率变大

50Mhz 对应一个计数为0.02us,也就是20纳秒,计数到1us要50个计数,其他可自己算,下面是产生1us、1ms、1s的方法

module count_time

#(

parameter CNT_1US_MAX = 6'd49,

parameter CNT_1MS_MAX = 10'd999,

parameter CNT_1S_MAX = 10'd999

)

(

input wire sys_clk,

input wire sys_rst_n,

output reg led_out

);

//50Mhz为20ns

reg [9:0]cnt_1s; //让1ms计数到1000

reg [9:0]cnt_1ms; //让1us计数到1000

reg [5:0]cnt_1us; //计数到50

reg cnt_en;

//1us

always@ (posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_1us <= 6'd0;

else if(cnt_1us == CNT_1US_MAX)

cnt_1us <= 6'd0;

else

cnt_1us <= cnt_1us +6'd1;

//1ms

always@ (posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_1ms <= 10'd0;

else if(cnt_1ms == CNT_1MS_MAX && cnt_1us == CNT_1US_MAX)

cnt_1ms <= 10'd0;

else if(cnt_1us == CNT_1US_MAX)

cnt_1ms <= cnt_1ms +10'd1;

else

cnt_1ms <= cnt_1ms;

//1s

always@ (posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_1s <= 10'd0;

else if(cnt_1s == CNT_1S_MAX && cnt_1ms == CNT_1MS_MAX && cnt_1us == CNT_1US_MAX)

cnt_1s <= 10'd0;

else if(cnt_1us == CNT_1US_MAX && cnt_1ms == CNT_1MS_MAX )

cnt_1s <= cnt_1s + 10'd1;

else

cnt_1s <= cnt_1s;

//控制状态

always@ (posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_en <= 1'b0;

else if(cnt_1s == CNT_1S_MAX && cnt_1ms == CNT_1MS_MAX && cnt_1us == CNT_1US_MAX)

cnt_en <= ~cnt_en;

else

cnt_en <= cnt_en;

always@ (posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

led_out <= 1'b1;

else if((cnt_en == 1'b0) && (cnt_1ms <= cnt_1s)

|| (cnt_en == 1'b1) && (cnt_1ms >= cnt_1s))

led_out <= 1'b0;

else

led_out <= 1'b1;

endmodule

时钟频率对应的时钟周期

5MHz 200ns

10MHz 100ns

20MHz 50ns

25MHz 40ns

33MHz 30ns

40MHz 25ns

50MHz 20ns

66MHz 15ns

80MHz 12ns

100MHz 10ns

120MHz 8.3ns

133MHz 7.5ns

166MHz 6.0ns

200MHz 5.0ns

250MHz 4.0ns

300MHz 3.3ns

333MHz 3.0ns

400MHz 2.5ns

500MHz 2.0ns

800MHz 1.2ns

1GHz 1.0ns

4GHz 0.25ns

常用单位换算

1GHz=1000MHz,1MHz=1000kHz,1kHz=1000Hz

1s=1000ms,1 ms=1000μs,1μs=1000ns

s(秒)、ms(毫秒)、μs(微秒)、ns(纳秒)

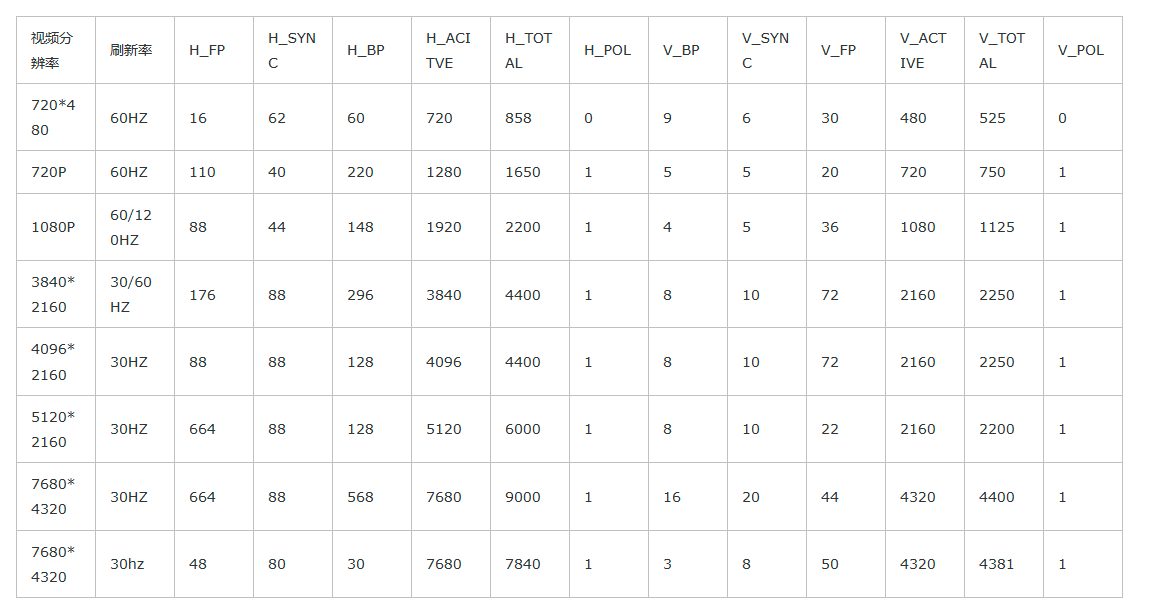

行扫描周期 * 场扫描周期 * 刷新频率 = 时钟频率

时钟频率与定时器设计

时钟频率与定时器设计

2216

2216

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?