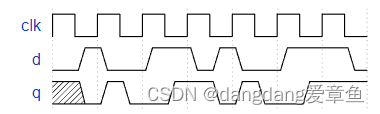

Dff

创建简单的触发器

代码如下:

module top_module (

input clk, // Clocks are used in sequential circuits

input d,

output reg q );//

// Use a clocked always block

// copy d to q at every positive edge of clk

// Clocked always blocks should use non-blocking assignments

always @(posedge clk)

q <= d;//组合电路用非阻塞赋值

endmoduleDFF8

创建位宽为8的D触发器:

代码如下:

module top_module (

input clk,

input [7:0] d,

output [7:0] q

);

always @(posedge clk)

q <= d;

endmoduleDff8r

本题多了同步复位信号,同步复位在触发源里面没有同步信号,只有时钟信号;

代码如下:

module top_module (

input clk,

input reset, // Synchronous reset同步复位信号

input [7:0] d,

output [7:0] q

);

always @(posedge clk) begin

if(reset)

q <= 0;

else

q <= d;

end

endmoduleDff8p

创建一个高电平同步复用的8位触发器,当复用信号不为0时,触发器必须复位为0x34而不是0,且时钟电路为低电平触发:

代码如下:

module top_module (

input clk,

input reset,

input [7:0] d,

output [7:0] q

);

always @(negedge clk)begin

if(reset)

q[7:0] <= 8'h0x34;

else

q <= d;

end

endmoduleDff8ar

高电平异步复位的8位触发器,由时钟的上升沿触发,触发源不再只是受时钟信号的影响,还受复位信号的影响:

代码如下:

module top_module (

input clk,

input areset, // active high asynchronous reset

input [7:0] d,

output [7:0] q

);

always @(posedge clk or posedge areset) begin

if(areset == 1)//当复位信号为高电平时触发,复位为0

q <= 8'b0;

else

q <= d;

end

endmoduleDff16e

创建一个16位的D触发器,加了一个多路选择器,当 byteena[1]为高电平时,输出q的高8位有d的高8位给出,当 byteena[0]为高电平时,输出q的低8位有d的低8位给出,还是同步复位;

代码如下:

module top_module (

input clk,

input resetn,

input [1:0] byteena,

input [15:0] d,

output [15:0] q

);

always @(posedge clk)begin

if(resetn == 0)begin

q <= 16'b0;

end

else begin

q[7:0] = byteena[0] ? d[7:0]:q[7:0];

q[15:8] = byteena[1] ? d[15:8]:q[15:8];

end

end

endmoduleExams/m2014 q4a

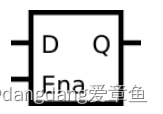

这是一个锁存器,所以是一个组合电路,所以和时钟无关,输出由输入和使能信号决定,由图可得,锁存器高电平触发:

代码如下:

module top_module (

input d,

input ena,

output q);

always @(*)begin

if(ena)

q = d;//组合电路所以用阻塞赋值

else

q = q;

end

endmoduleExams/m2014 q4b

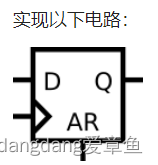

代码如下:

module top_module (

input clk,

input d,

input ar, // asynchronous reset

output q);

//如上电路图所示,如果接口处有小圈则只是低电平有效,否则是高电平有效

//上图有一个clk时钟和ar高电平复位信号,触发时输出为0

always @(posedge clk or posedge ar)begin

if(ar)

q = 1'b0;

else

q = d;

end

endmoduleExams/m2014 q4c

代码如下:

module top_module (

input clk,

input d,

input r, // synchronous reset

output q);

//上图为同步复位,所以触发源里面就不需要posedge复位电平了

always @(posedge clk)begin

if(r)

q <= 1'b0;

else

q <= d;

end

endmoduleExams/m2014 q4d

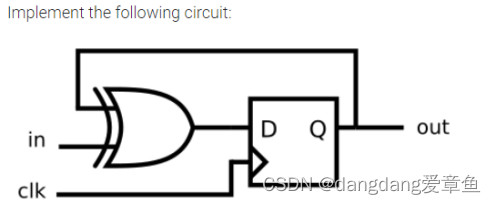

代码如下:

module top_module (

input clk,

input in,

output reg out);

//这是一个逻辑门结合触发器的电路

//注意:always块里面被赋值的变量必须是寄存器的形式

always@(posedge clk)begin

out = in ^ out;

end

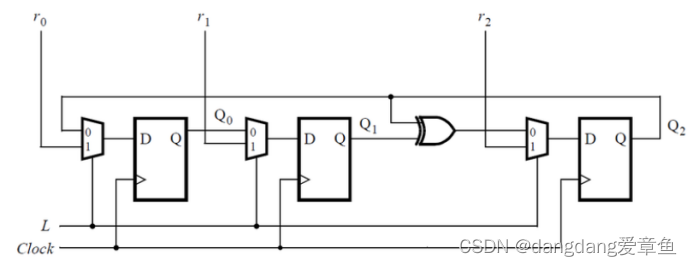

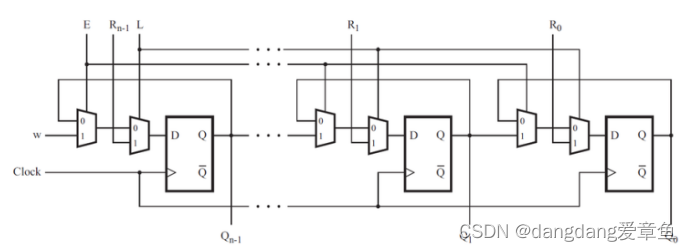

endmoduleMt2015 muxdff

考虑电路的逻辑顺序,用代码把一个触发器和一个多路选择器表示出来:

代码如下:

module top_module (

input clk,

input L,

input r_in,

input q_in,

output reg Q);

//只需要写一个触发器和一个多路选择器就可以

always @(posedge clk)begin

Q = L?r_in:q_in;

end

endmoduleExams/2014 q4a

组合电路

代码如下:

module top_module (

input clk,

input w, R, E, L,

output Q

);

//首先看D触发器的输出,输出由L和E决定,加上时钟

always @(posedge clk)begin

Q = L?R:(E?w:Q);

end

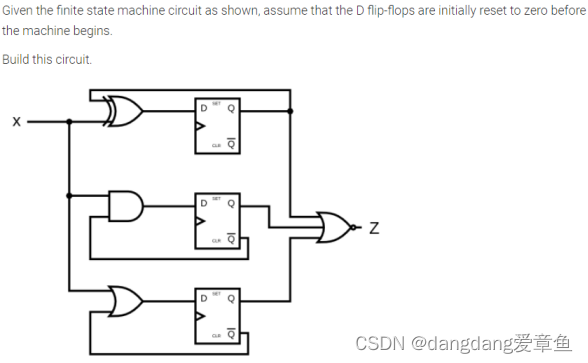

endmoduleExams/ece241 2014 q4

代码如下:

module top_module (

input clk,

input x,

output z

);

wire D0,D1,D2;

wire Q0,Q1,Q2;

assign D0 = x ^ Q0;

assign D1 = x & !Q1;

assign D2 = x | !Q2;

myDFF DFF_0(clk,D0,Q0);//使用位置式来实例化3个小模块

myDFF DFF_1(clk,D1,Q1);

myDFF DFF_2(clk,D2,Q2);

assign z = !(Q0 | Q1 | Q2);

endmodule

//实例化一个模块

module myDFF(

input clk,

input d,

output reg q);

always @(posedge clk)begin

q <= d;

end

endmoduleExams/ece241 2013 q7

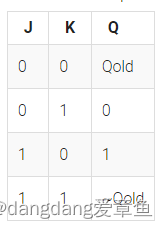

一个JK触发器有如下的真值表信息,JK触发器仅仅只能有一个D触发器和门电路组合而成,时钟信号高电平触发:

代码如下:

module top_module (

input clk,

input j,

input k,

output Q);

//利用真值表来判断Q的输出

always @(posedge clk)begin

Q <= j?(k?~Q:1'b1):(k?1'b0:Q);

end

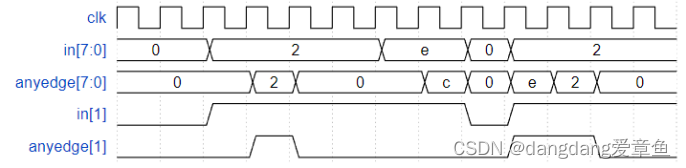

endmoduleEdgedetect

对于一个8位的变量,检测输出当输入信号发生跳变时输出信号会产生高电平;

代码如下:

module top_module (

input clk,

input [7:0] in,

output [7:0] anyedge

);

//只要输入有变化,检测输出都为高电平

reg [7:0] in_1;

always @(posedge clk)begin

in_1 <= in;

anyedge <= in ^ in_1;

end

endmoduleEdgecapture

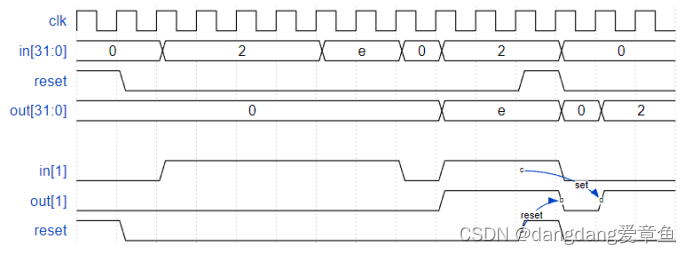

对于 32 位矢量中的每个位,捕获输入信号从一个时钟周期中的 1 变为下一个时钟周期的 0 时。“捕获”表示输出将保持1,直到寄存器复位(同步复位)。

每个输出位的行为类似于SR触发器:输出位应设置为(1)发生1到0转换后的周期。当复位为高电平时,输出位应在正时钟边沿复位(至0)。如果上述两个事件同时发生,则重置优先。在以下示例波形的最后 4 个周期中,“重置”事件比“设置”事件早一个周期发生,因此这里没有冲突。

在下面的示例波形中,为清楚起见,重置、输入 [1] 和输出 [1] 再次单独显示。

代码如下:

module top_module (

input clk,

input reset,

input [31:0] in,

output [31:0] out

);

reg [31:0] in_1;

always @(posedge clk)begin

in_1 <= in;

if(reset)

out <= 32'b0;

else

out <= (~in&in_1) | out;

end

endmoduleDualedge

当输入信号发生跳变时,输出信号也会跟着发生跳变,但是设置的触发器要么是时钟上升沿触发,要么是下降沿触发,如果设置一个时钟上升沿和下降沿同时触发的触发器,always块写成always @(posedge clk or negedge clk)这样是不合法的;所以我们可以分别用两个always块来表示;

代码如下:

module top_module (

input clk,

input d,

output q

);

//always @(posedge clk or negedge clk)这样写是不合法的,

//上升沿和下降沿不能同时出现在触发源里

//则需要用两个always块进行操作,但是不应该在多个模块中同时赋值给两个一样的变量

reg q_pedge;

reg q_nedge;

always @(posedge clk)

q_pedge <= d;

always @(negedge clk)

q_nedge <= d;

assign q = clk?q_pedge:q_nedge;

endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?