-

插槽结构图

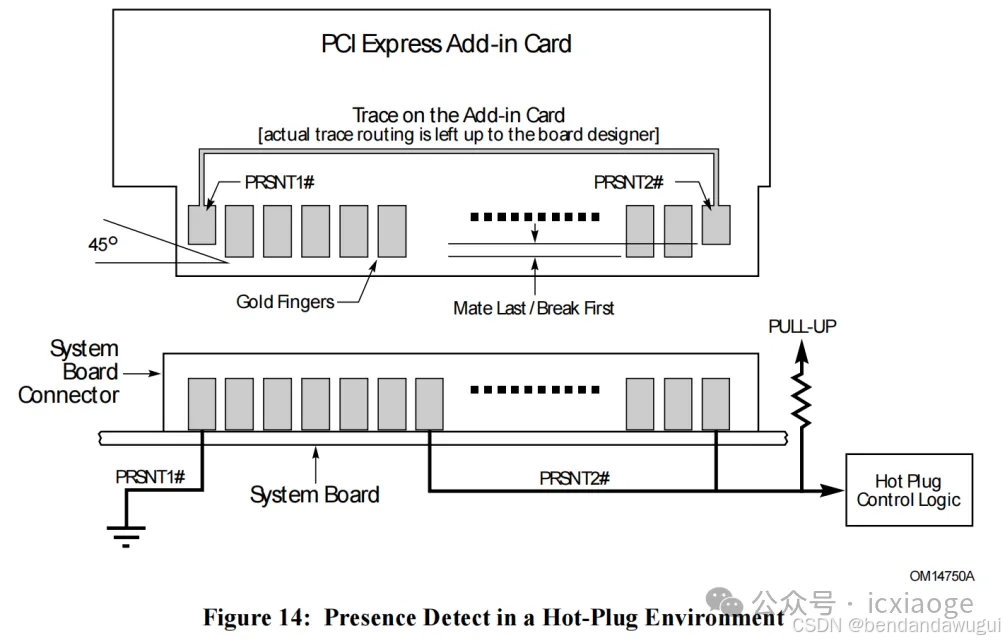

- 根据CEM标准,PCIe add-in card有两个用于热插拔机制的边带信号,分别是PRSNT1#和PRSNT2#,这两个信号是连接在一起的,且这两根信号的金手指长度要比其他的信号的金手指长度要短一点,而在system board connector(俗称插槽)上,PRSNT1#被固定接地,PRSNT2#则被弱上拉(PULL-UP)如下图中所示,当PCIe卡设备被完全插入插槽后,插槽上的PRSNT2#信号则会被PCIe卡设备的短路线连接到地,从而使得其变为低电平,hot plug control logic检测到PRSNT2#从高电平跳变到低电平,则会通知downstream port发现presence detect事件,downstream port会发送中断消息给RC,通知系统软件有设备插入。

- 热插拔基本原理

- 支持热插拔的Switch downstream port(简称dsp)的PCI express Capability structure必须实现slot control register 和 slot status register,当存在endpoint 插入或者拔出时,dsp的硬件逻辑会更新相关的状态寄存器,例如,endpoint插入和拔出时,slot status register中的Data link Layer state change会置1(因为 the data link layer link active bit of the link status register 发生了变化)

- switch内部存在专门管理热插拔的模块(Hot Plug Control Module),可以通过监控Slot Status Register检测到如下hot plug事件的发生:

- Power Fault Detected

- MRL Sensor Changed

- Presence Detect Change

- Command Completed

- Attention Button Pressed

- Data Link Layer State Changed

- 当检测到hot plug事件发生时,且slot control使能信号为1时,当前dsp发出中断消息通知host发生了hot plug事件,中断消息通常是通过MSIX或者MSI中断发送的,因为其他事件(例如功耗事件)也能触发中断消息;

- 因此系统软件收到中断时,会通过配置请求(cfg rd)读取DSP的状态寄存器,从而得出中断的具体原因;

- 例如通过读dsp的Link Status Register和Slot Status Register就能知道是否存在endpoint的插入和拔出;

-

• Link Status Register的Data Link Layer Link Active bit 为1 且 Slot Status Register的Data Link Layer State Changed 为1 ,则表示有endpoint插入slot

•Link Status Register的Data Link Layer Link Active bit 为0 且 Slot Status Register的Data Link Layer State Changed 为1 ,则表示有endpoint拔出slot

- 根据CEM标准,PCIe add-in card有两个用于热插拔机制的边带信号,分别是PRSNT1#和PRSNT2#,这两个信号是连接在一起的,且这两根信号的金手指长度要比其他的信号的金手指长度要短一点,而在system board connector(俗称插槽)上,PRSNT1#被固定接地,PRSNT2#则被弱上拉(PULL-UP)如下图中所示,当PCIe卡设备被完全插入插槽后,插槽上的PRSNT2#信号则会被PCIe卡设备的短路线连接到地,从而使得其变为低电平,hot plug control logic检测到PRSNT2#从高电平跳变到低电平,则会通知downstream port发现presence detect事件,downstream port会发送中断消息给RC,通知系统软件有设备插入。

PCIe个人理解专栏——【3】热插拔原理

于 2025-02-07 19:10:19 首次发布

95

95

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?