前言

随着FPGA的广泛应用,DDR作为大容量存储器件被广泛应用于FPGA中的数据缓存。现基于intel 的DDR4 IP提供的仿真例程进行基本的功能仿真。

一、DDR介绍

DDR即双倍率动态随机存储器,即时钟上升沿和下降沿都处理数据,是SDRAM速度的两倍。DDR的频率可以用工作频率和等效频率来表示,工作频率即DDR运行的实际频率,而由于DDR一个周期可以处理两次数据,所以等效频率为工作频率的两倍。截至目前,已经有DDR,DDR2,DDR3,DDR4,DDR5这几种。 个中差异,由于时间关系,在此就不展开。

二、仿真准备

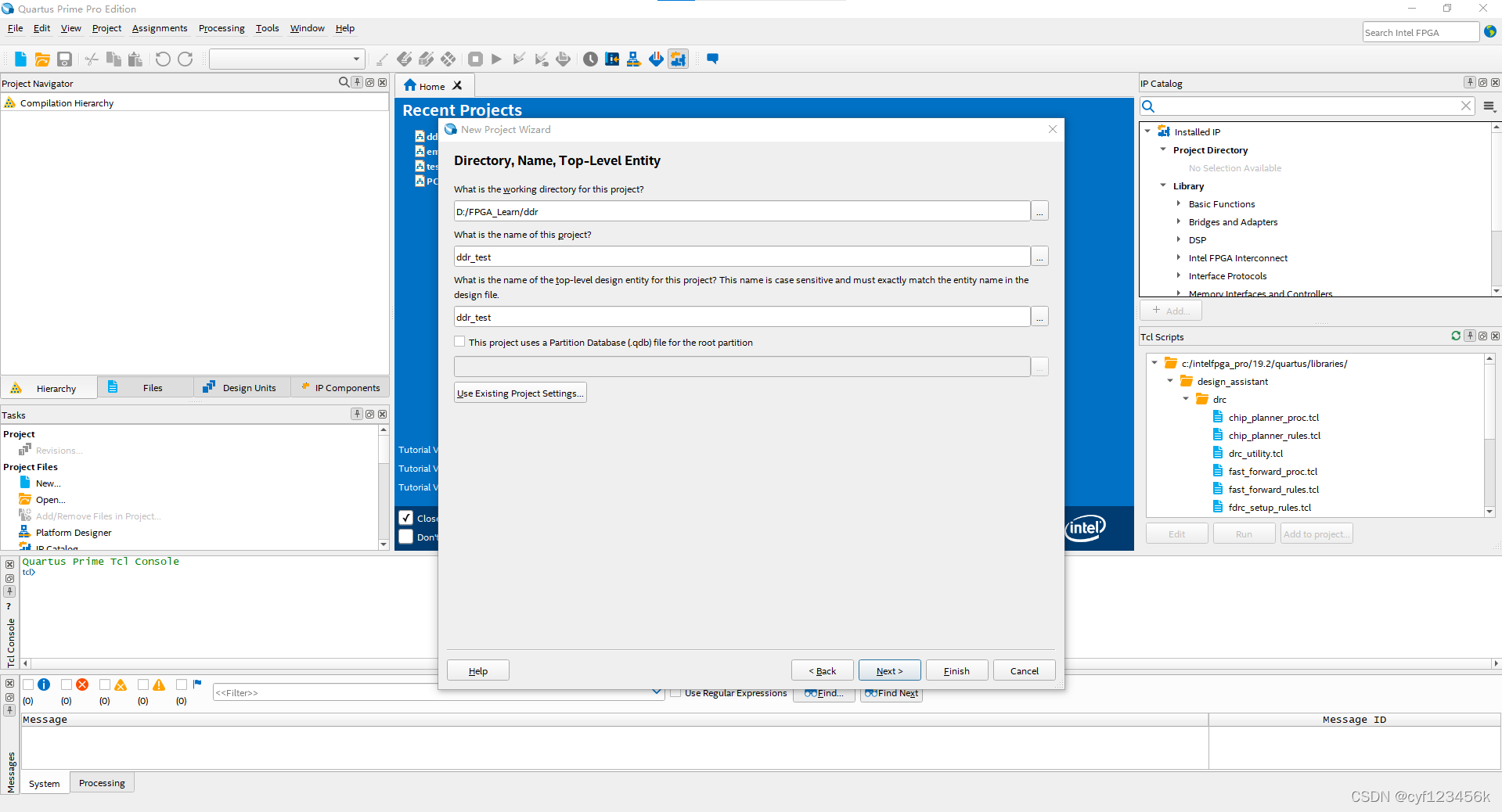

1.建立工程

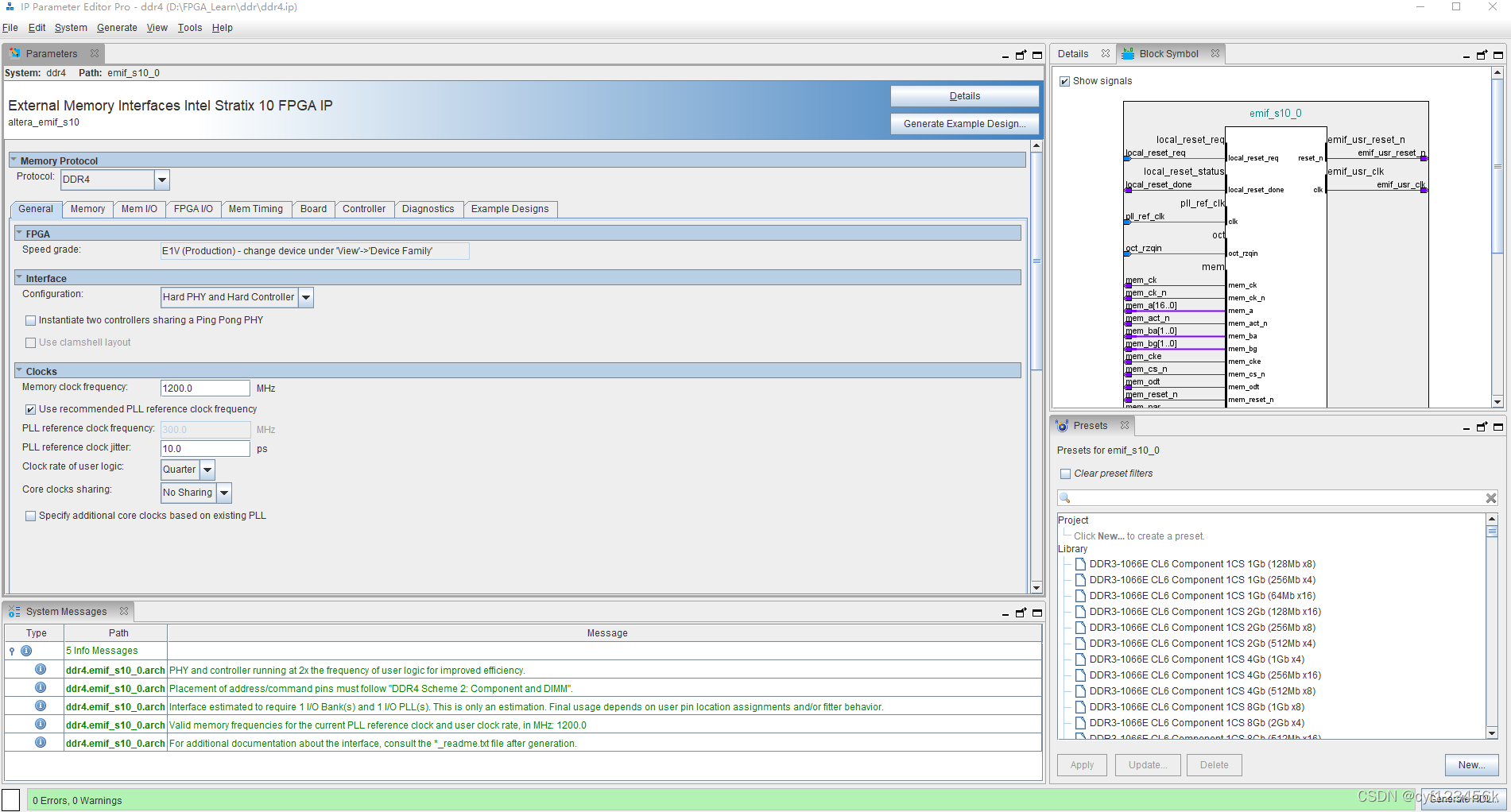

2.添加DDR IP

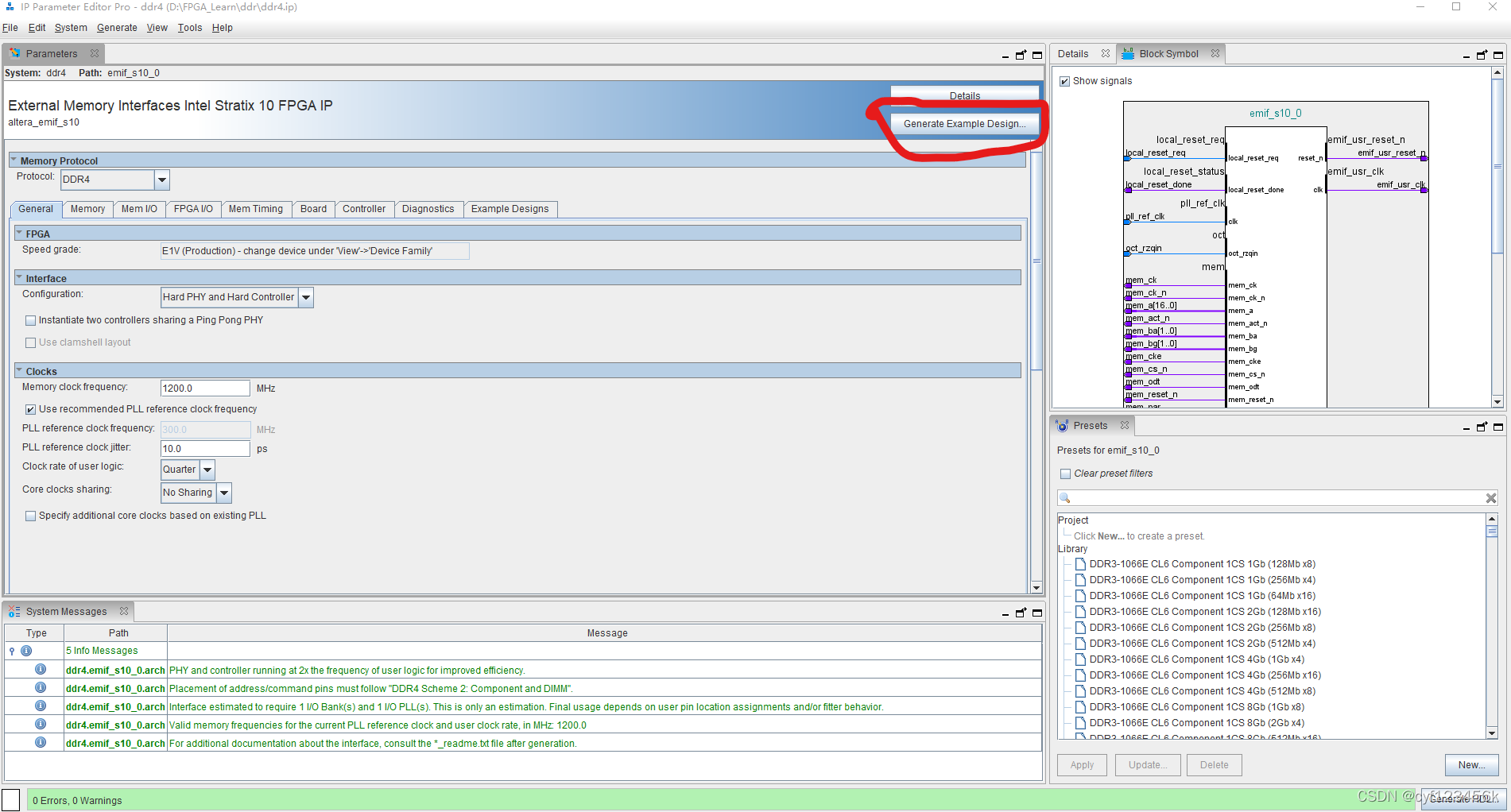

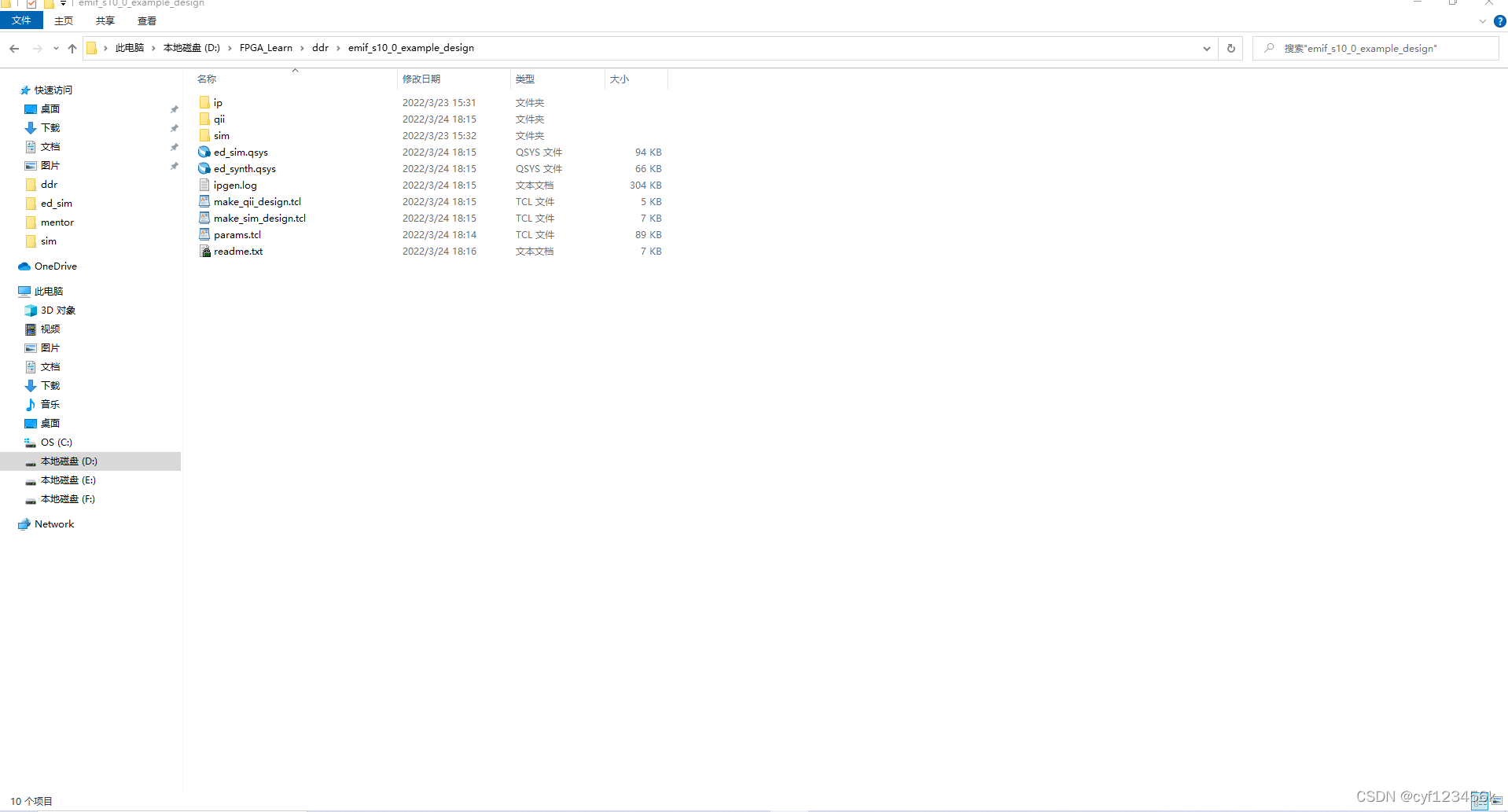

3.生成仿真工程

点击图示中Create Example Design ,默认会在工程目录下生成一个名为emif_s10_0_example_design的文件夹,如下图。

3.官方仿真

3.1 新建仿真脚本

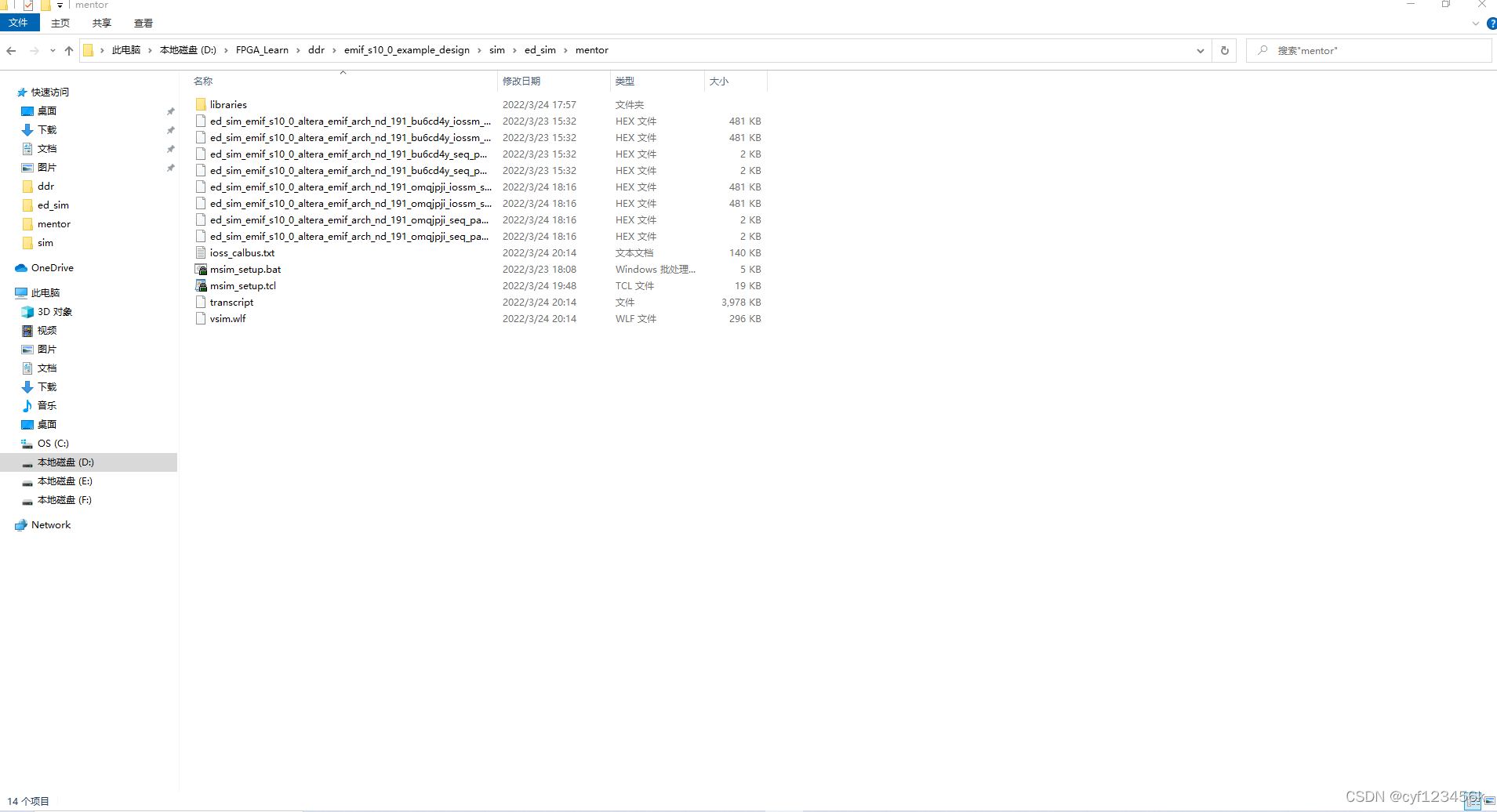

1.在emif_s10_0_example_design\sim\ed_sim\mentor路径下新建一个txt文件,输入下述命令,并保存为msim_setup.bat。(注:读者可根据自己的需要修改)

vsim -do ./msim_setup.tcl

如下图

3.2 Modelsim仿真

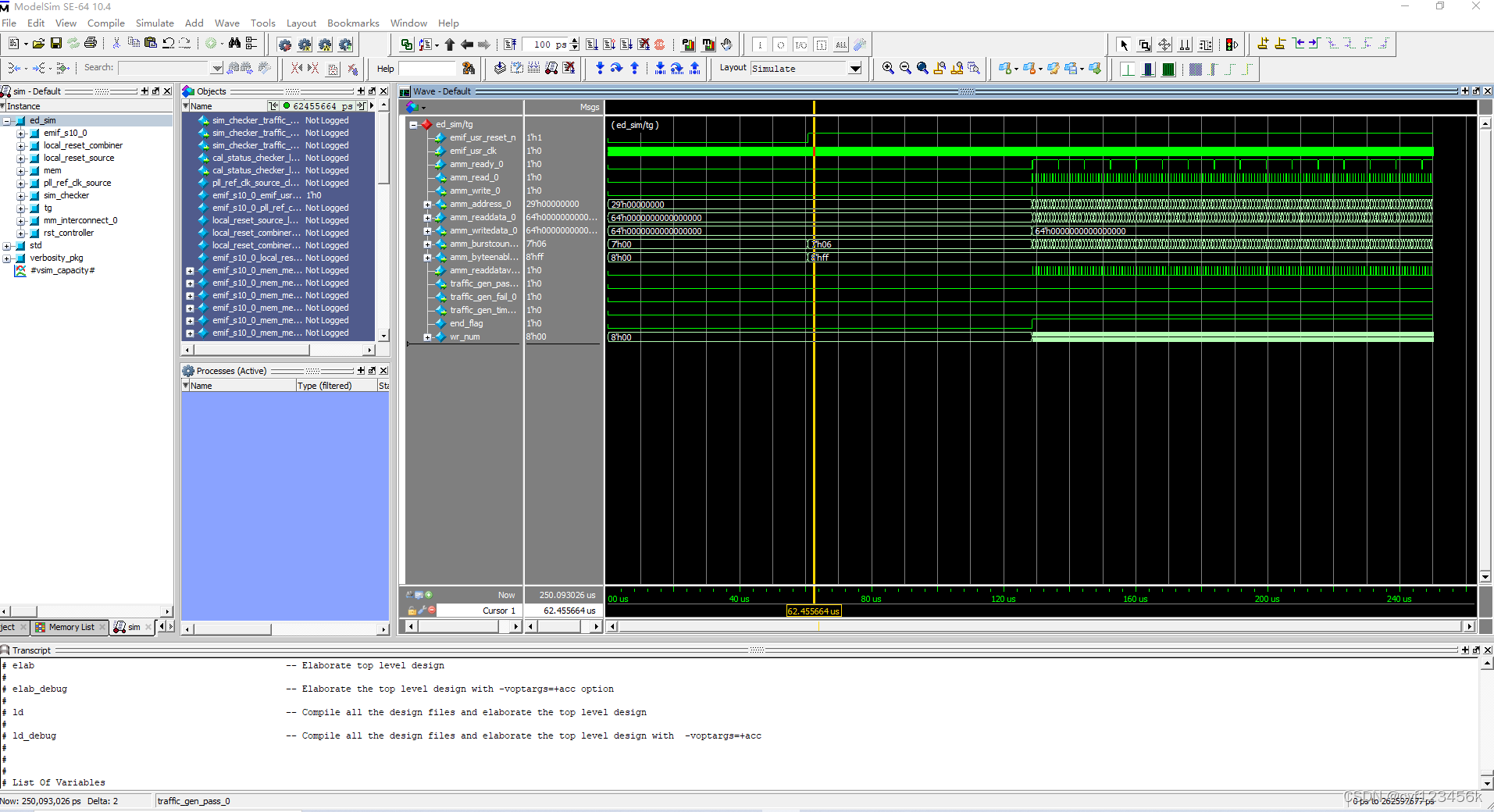

1.点击msim_setup.bat,便会自动运行modelsim。

2.在modelsim的命令窗口运行ld_debug。

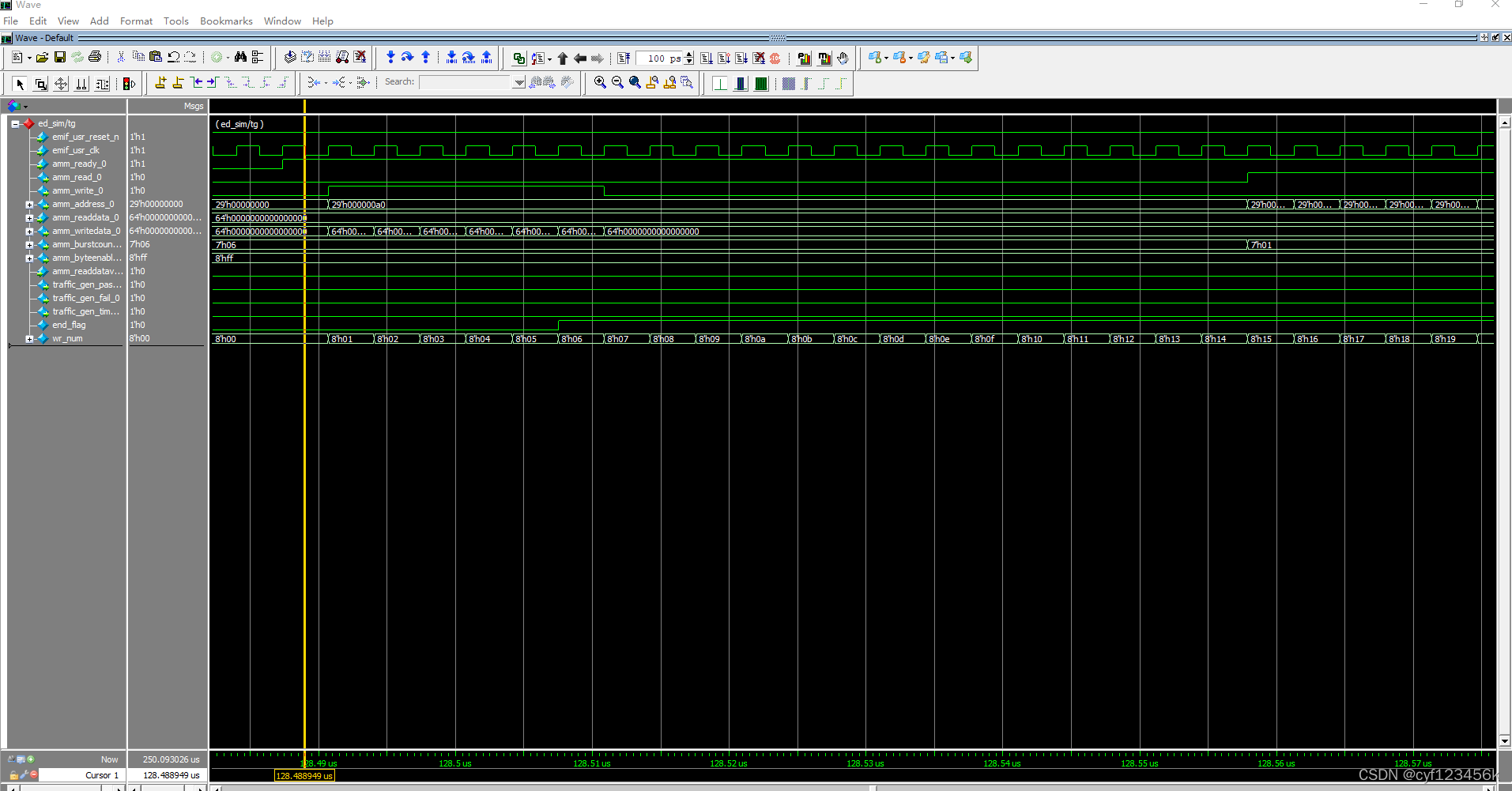

3.添加波形,运行run -all。

4.仿真修改

上述的仿真结果是根据官方例程的结果,下面介绍怎样修改例程,通过例程跑自己的控制代码。

4.1 修改msim_setup.tcl文件。

在msim_setup.tcl文件中加上下述代码:

alias rtl {

if [string is false -strict $SILENCE] {

echo "\[exec\] rtl"

}

eval vlog ../sim/ddr_control_sim.v #控制rtl

}

4.2 修改ed_sim文件

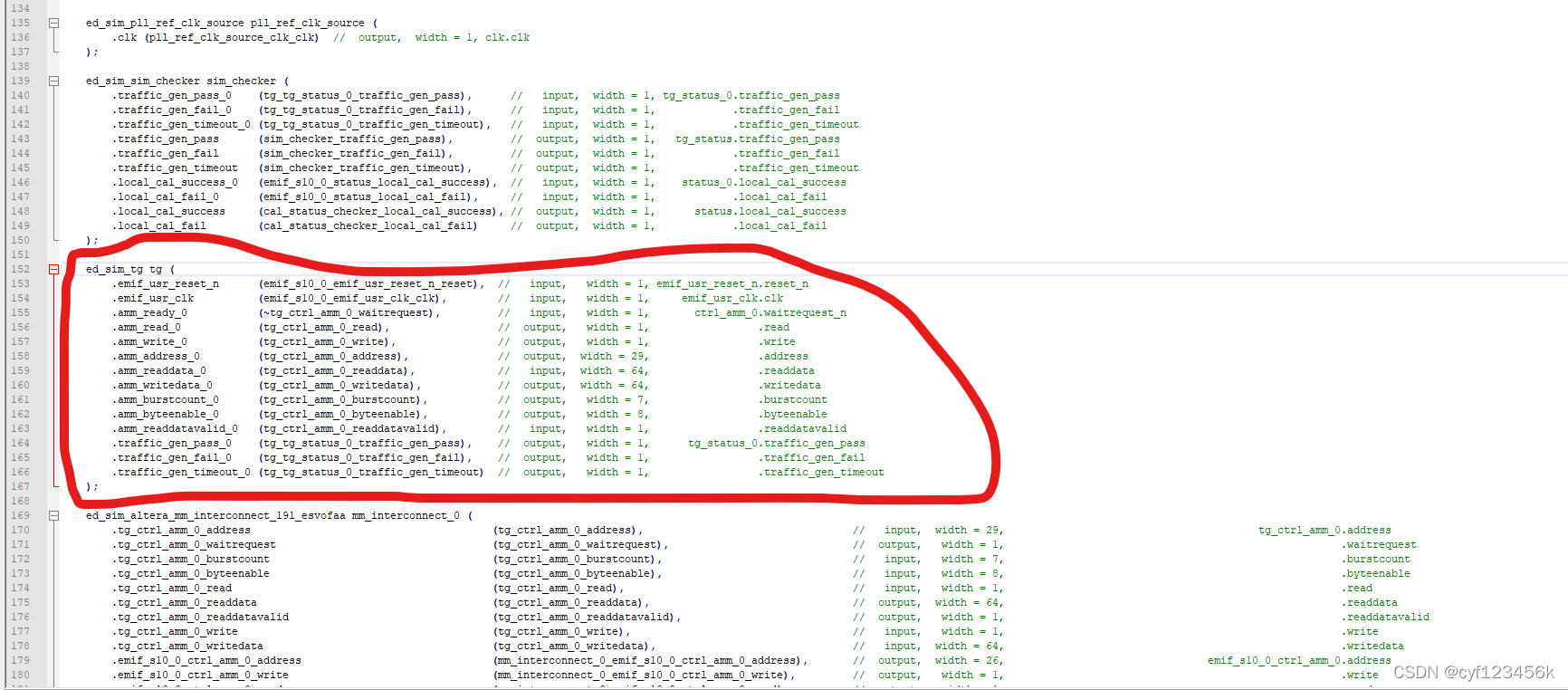

1.在emif_s10_0_example_design\sim\ed_sim\sim目录下找到ed_sim.v文件,并打开该文件。如下图:

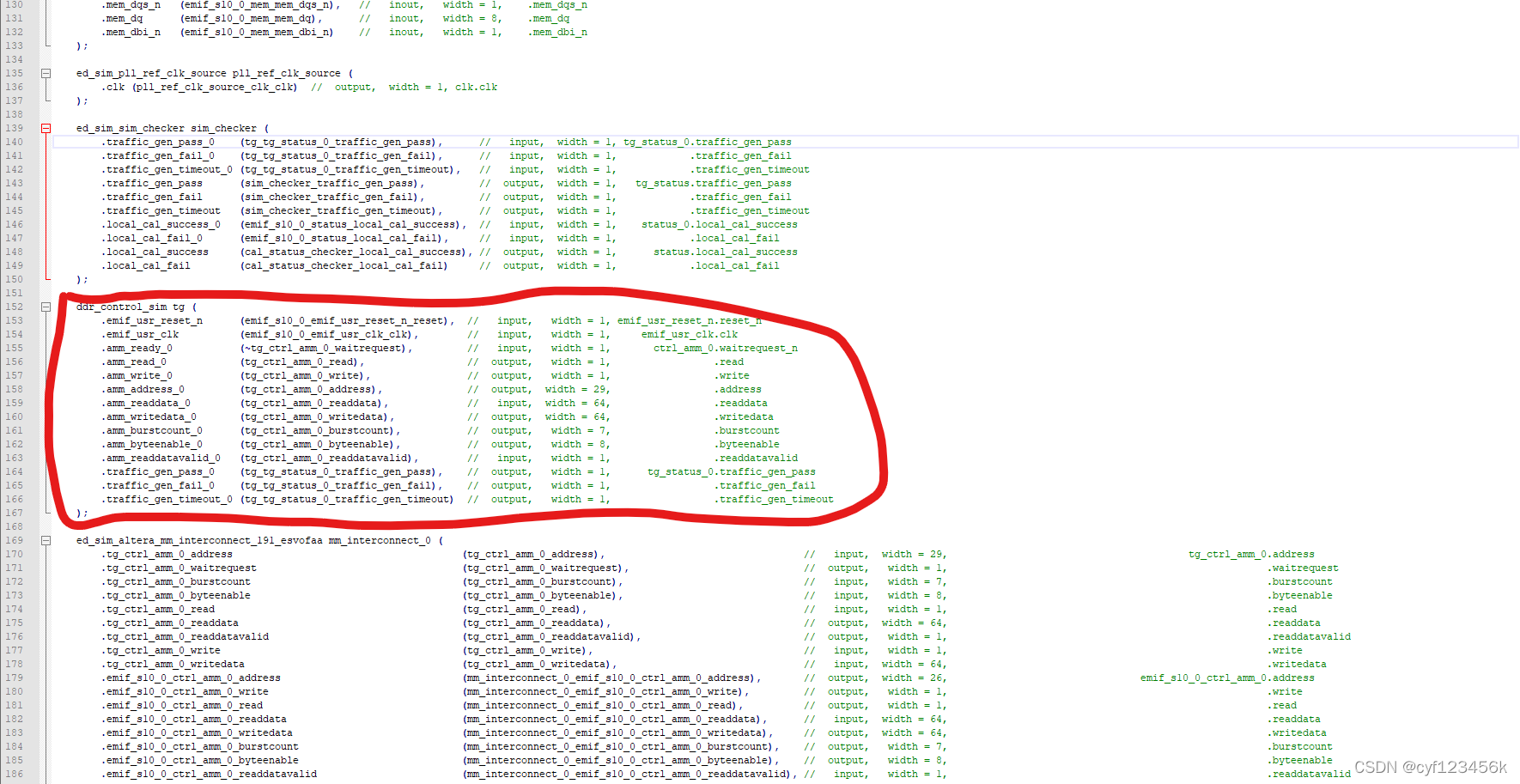

2.将图示部分修改为自己的控制代码。如下图:

3.输入do ./msim_setup.tcl 重新运行,输入rtl编译仿真文件,最后run -all。如下图:

附录

Intel Avalon接口介绍:Avalon® Interface Specifications

本文介绍了DDR4作为高性能存储器在FPGA中的应用,并基于Intel的DDR4 IP进行功能仿真。内容覆盖DDR的基本概念、仿真准备工作流程、官方仿真步骤及如何修改例程以实现自定义控制。

本文介绍了DDR4作为高性能存储器在FPGA中的应用,并基于Intel的DDR4 IP进行功能仿真。内容覆盖DDR的基本概念、仿真准备工作流程、官方仿真步骤及如何修改例程以实现自定义控制。

200

200

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?