本文主要介绍了DDR4设计方法与仿真分析,并示范SIwave如何做DDR4的瞬时眼图、SSN、on-die de-cap影响、DBI耗电分析与规范性测试。

1.DDR4和DDR3的区别

1.1 DDR4传输速度与带宽增加

DDR3 1600/1866MHz -> DDR4 1866/3200MHz

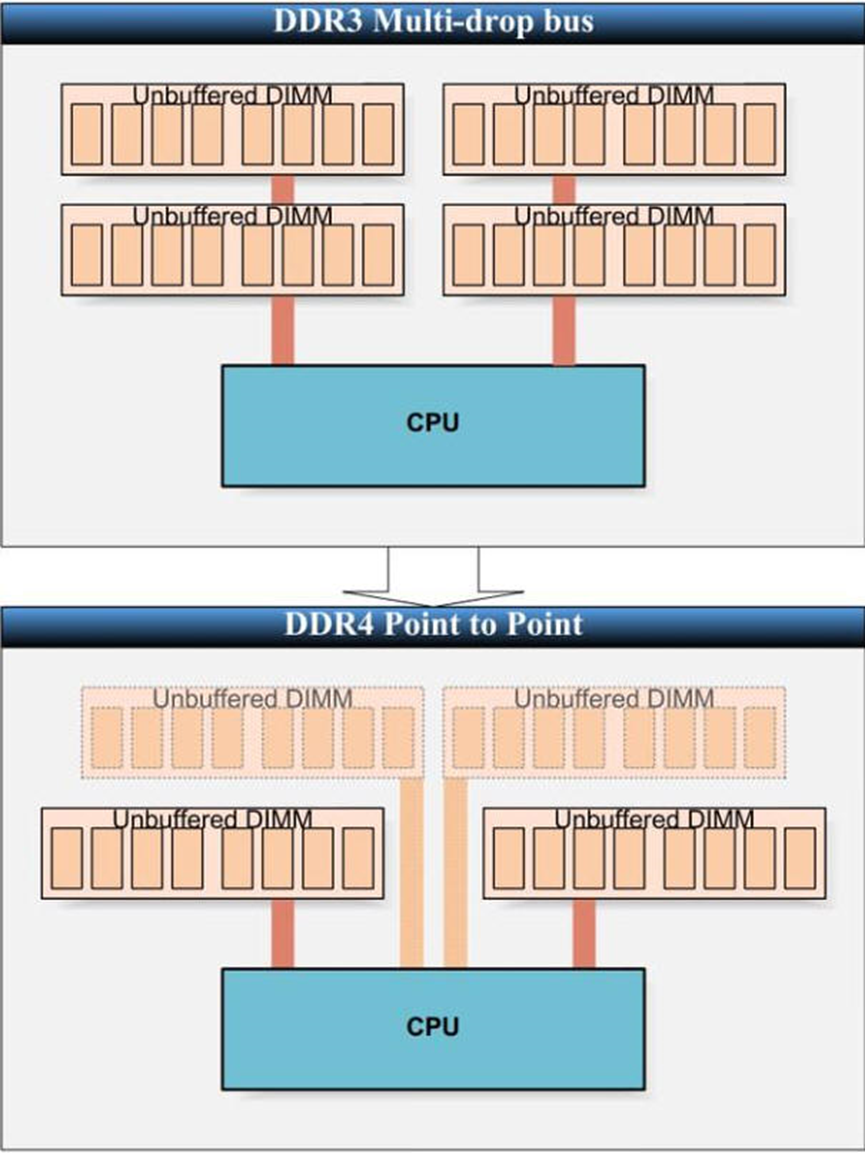

DDR3采用多点分支单流架构,DDR4采用点对点传输架构

DDR3采用了大水库理论,所有数据集中到一根大水管后送出。而DDR4则采用点对点分流架构,当每一条水管流量都很大时,累加起来的流量会超过单一条大水管,能避免单条信道传输带宽的瓶颈拖慢整体效能。

现在DDR4大部分还是采用2SPC (2 Slot per Channel)或称2DPC (2 DIMM per Channel)的架构,2017 Q1最新的Intel® Core™ i7-7920HQ处理器,最快支持到DDR4 2400MHz;开发中的2666/3200MHz也是采用2SPC传输架构。

1.2 DDR4更省电

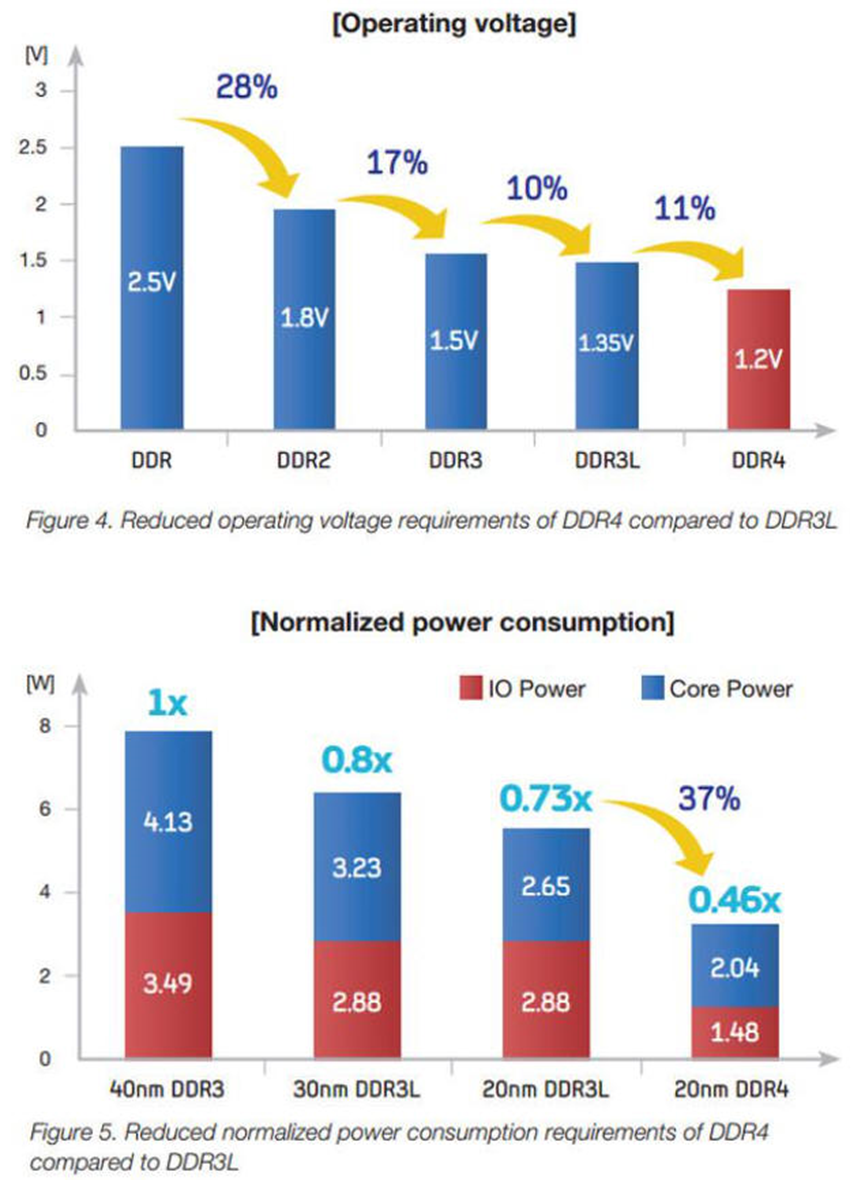

操作电压降低:DDR4(1.2V), DDR3(1.5V)。除了降低工作电压,LPDDR4支持深度省电模式(DPD, Deep Power Down Mode),DDR4支持Max Power Saving Mode,在暂时不需要用到内存的时候可进入休眠状态,可进一步减少待机时功率的消耗。

Deep Power Down Mode:SDRAM controller发送Deep Power Down命令可以将SDRAM芯片推送到一个极低功耗状态(约15uA)。这时候存储数组的power会被shutdown,也就是意味着所有的数据是丢失掉了,这时候,mode register的设定是保持的。当从Deep Power Down退出的时候,需要对SDRAM芯片进行一个完整的初始化过程。

DDR4搭载了温度自更新回馈机制(TCSE,Temperature Compensated Self-Refresh),能够降低芯片在自动更新时所需耗费的电力,同时,还导入了数据汇流反转机制(DBI,Data Bus Inversion),使得VDDQ电流量得到有效控制。

本文详述DDR4相较于DDR3在传输速度、带宽提升和节能方面的改进,如点对点传输架构和1.2V操作电压。此外,探讨了DDR4的高速信号技术,包括POD接口、DBI和TCSE如何降低功耗。文章还强调了设计方法的重要性,如3D封装技术、IC和系统的PI与SI优化,以及DDR4的SIwave仿真分析。

本文详述DDR4相较于DDR3在传输速度、带宽提升和节能方面的改进,如点对点传输架构和1.2V操作电压。此外,探讨了DDR4的高速信号技术,包括POD接口、DBI和TCSE如何降低功耗。文章还强调了设计方法的重要性,如3D封装技术、IC和系统的PI与SI优化,以及DDR4的SIwave仿真分析。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

95

95

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?