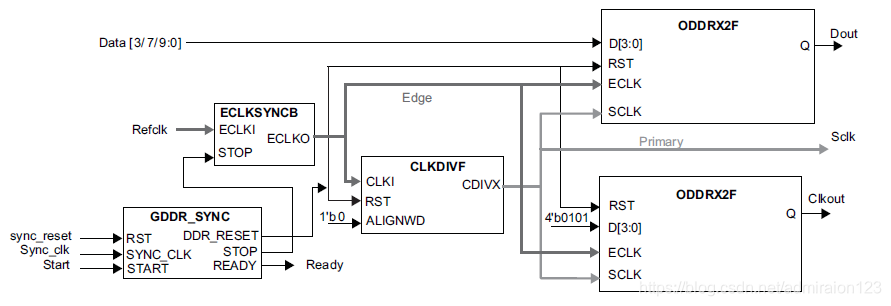

本文主要参考的是Lattice的I/O使用手册,芯片为ECP5-25,官网下载搜索TN1265即可。FPGA中,数据与采样的关系有两种,中心对齐和边沿对齐,I/O口的高速设计也就是围绕这两个展开的。对于边沿对齐,需要调整时钟,保证满足捕获触发器的时序要求;对于中心对齐,需要平衡数据和时钟的延时,满足捕获触发器的时序要求。例如下图1是发送时边沿对齐模式的配置,ECLKSYNCB模块用于将时钟布到ECLK网络,CLKDIVF用于分频。

图1 GDDRX2_TX.ECLK.Aligned Interface

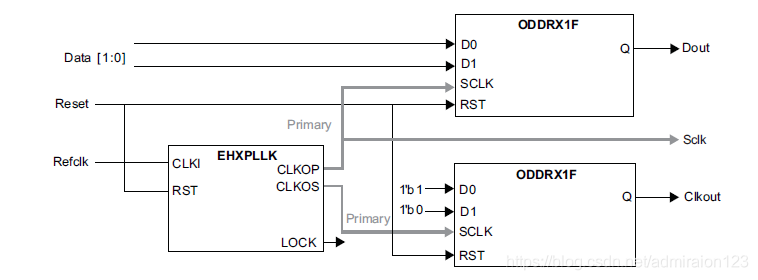

图2是发送时中心对齐模式配置,EHXPLLK用于产生相位差为90°的时钟。文档中还有许多配置,如I/O口双倍速率发送接收时怎么配置,MIPI接口怎么配置,具体内容较多,项目中也没用到,就不说了。

图2 GDDRX1_TX.SCLK.Centered Interface

项目中,FPGA时钟源采用外部晶振25M,FPGA系统时钟为125M,晶振时钟的引入脚必须是GPLL属性,该引脚直接连接FPGA内部PLL资源,不会降低时钟信号质量。ECP5-25中里有两个PLL,分别位于靠底部的左和右,即第6bank和第3bank,项目中用到的是LLC_GPLL0T_IN(因为项目时钟方案是两个phy芯片串联,晶振进入phy1,然后phy1给phy2时钟,phy2的输出给fpga,phy2位置靠近左边),注意 LLC_GPLL0C_IN是差分时钟用的,单线的必须接在true上。

对于网口,采用lattice里的ddr_generic搭建。时钟125M,接收模块采用中心对齐配置,发送模块采用边沿对齐配置。接收时钟通过PCLK属性引脚引入,经过rgmii_in出来的时钟也需要约束到主网络时钟上,然后通过fifo进行跨时钟域处理;发送时钟分为两部分,一部分给rgmii_out,直接用系统时钟即可;一部分给gamii_out1,用于调时钟相位,都需要约束到主时钟网络上。数据引脚需要分配到具有ddr属性的引脚上。至于网口的mdc时钟(速度相对于系统时钟来说很低)和mdio口,无需特定配置,普通I/O口就行。

对于sdram,sdr_clk时钟也需要约束到主时钟网络。由于pad 到I/O buffer有专用布线资源,因此对于数据口、地址等也最好将寄存器放入IO buffer里,保证数据在进出fpga后同步,可通过syn_useioff或者在综合策略里面修改。

对于spi flash,使用fpga里spi专用引脚即可。spi时钟可使用USRMCLK primitive调用。

对于ddr3,需要放在1.5V供电的bank中,DQ电平类型设置为SSTL15,DQS电平类型设置为SSTL15D(选择此类型后,其对应的COMP引脚会自动配置);对应的2bit DQS信号、8bit DQ信号、DM信号应放在一个DQS组内,且DQS信号必须约束在DQS组里的专用引脚;只能使用左右两边bank的I/O;CK也应配置为SSTL15D,且最好和DQS组放在同一边,以减小延时;地址和控制信号放在顶端或者DQS同一边;DDR3参考输入时钟ddr_clk_in也必须使用pll专用引脚;另外,对于配置了DDR memeory接口的bank,其VREF1必须作为参考电压输入;每个DQS数据组最好设置一个虚拟电源,抑制SSN。

对于serdes,使用的是lattice的硬核,位于芯片下端。如果使用外部时钟,需要走pll专用引脚。serdes时钟方案很多,会根据协议不同而不同,但一般4个通道的接收时钟按通道走,发送时钟都采用通道0发送时钟,tx_pll和cdr参考时钟采用一个时钟源。

另外,引脚分配应尽量靠近器件,应尽量使用fpga外部引脚,缩短PCB布线;对于bank中不使用的引脚,可设置成虚拟地或电源,与外部地、电源连接;可抑制供电不稳问题。

再补充一些引脚时序约束的东西:1,设计中infer GSR选项一定要打开(默认打开的),这样你的全局复位信号就会走芯片专有的硬件复位资源布线。2,在rtl代码中syn_useioff可以在顶层输入、输出使用哦I/O寄存器,提高I/O口时序。3,在rtl代码中syn_maxfan可以控制扇出,综合时如果扇出超出设定值,会自动添加寄存器分成多分。4,lpf文件中的block属性使用可以参考diamond在线help文档。

本文详细介绍了Lattice ECP5-25 FPGA的I/O设计,包括高速接口配置、时钟网络管理、DDR3内存接口、SerDes应用及引脚分配原则。深入探讨了数据与时钟的对齐方式,以及各种接口如网口、SDRAM、SPI Flash的配置细节。

本文详细介绍了Lattice ECP5-25 FPGA的I/O设计,包括高速接口配置、时钟网络管理、DDR3内存接口、SerDes应用及引脚分配原则。深入探讨了数据与时钟的对齐方式,以及各种接口如网口、SDRAM、SPI Flash的配置细节。

1436

1436

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?