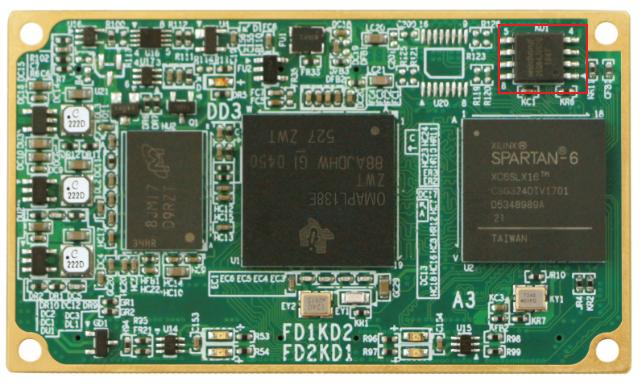

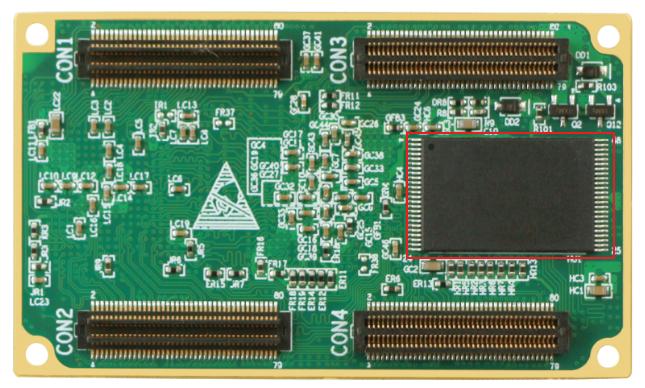

本文测试板卡是TL138/6748F-EVM开发板,它是创龙科技基于Omapl138/TMS320C6748+FPGA核心板开发。由于SOM-TL138F/SOM-TL6748F核心板管脚兼容,所以共用同一个底板。开发板采用核心板+底板的设计方式,尺寸为24cm*13cm,它主要帮助开发者快速评估核心板的性能。

核心板采用高密度8层板沉金无铅设计工艺,尺寸为66mm*38.6mm,板载3路高转换率DC-DC核心电压转换电源芯片,实现了系统的低功耗指标,精密、原装进口的B2B连接器引出全部接口资源,以便开发者进行快捷的二次开发使用。

ISE仿真库编译步骤

点击“开始菜单 -> Xilinx ISE Design Suite 13.2 -> ISE Design Tools -> 64-bit Tools -> Simulation Library Compilation Wizard”(如果是32位PC则点击32-bit Tools),如下图所示:

本文详细介绍了如何在ISE环境下编译针对Omapl138/TMS320C6748+FPGA核心板的仿真库。通过一系列步骤,包括启动Simulation Library Compilation Wizard,设置Modelsim路径,选择输出目录,并耐心等待长达1.5小时的编译过程。

本文详细介绍了如何在ISE环境下编译针对Omapl138/TMS320C6748+FPGA核心板的仿真库。通过一系列步骤,包括启动Simulation Library Compilation Wizard,设置Modelsim路径,选择输出目录,并耐心等待长达1.5小时的编译过程。

订阅专栏 解锁全文

订阅专栏 解锁全文

1543

1543

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?