HLS案例开发2_led_flash案例|基于FPGAKintex-7开发板

目录

HLS案例开发2_led_flash案例|基于FPGAKintex-7开发板

前 言

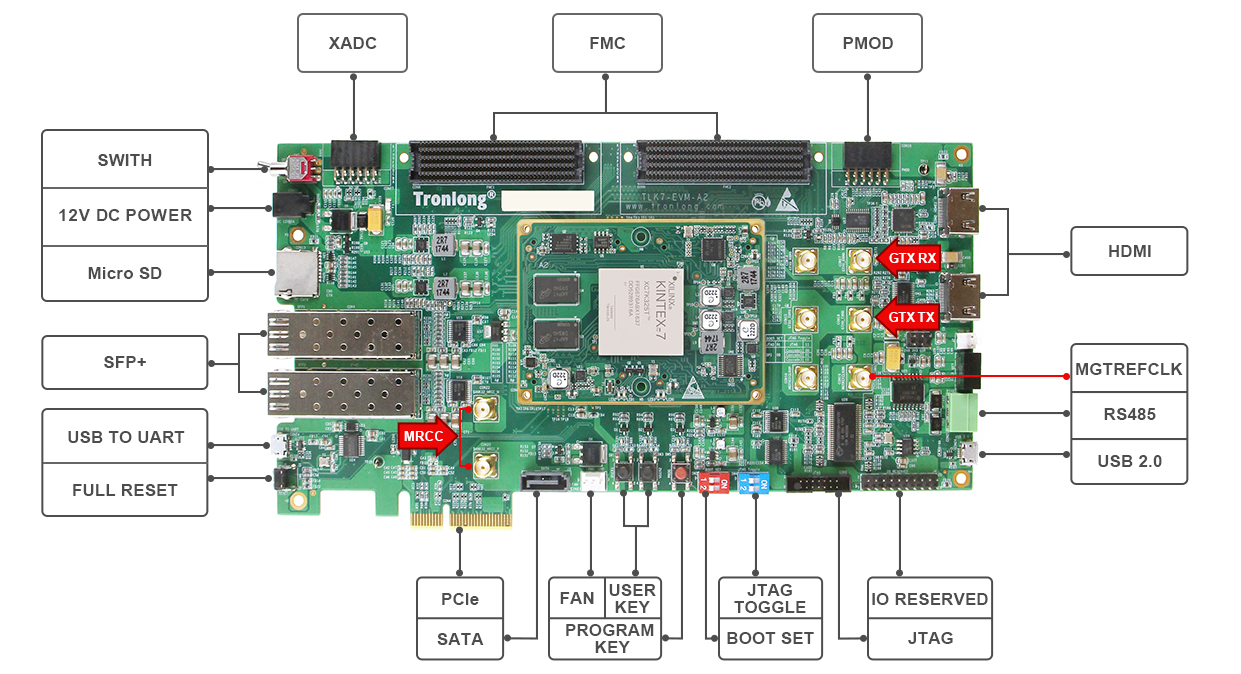

本文led_flash案例是基于创龙科技TLK7-EVM开发板,是一款基于Xilinx Kintex-7系列FPGA设计的高端评估板,由核心板和评估底板组成。核心板经过专业的PCB Layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。

评估板接口资源丰富,引出FMC、SFP+、PCIe、SATA、HDMI等接口,方便用户快速进行产品方案评估与技术预研。

TLK7-EVM评估板

开发案例主要包括:

1.CameraLink、SDI、HDMI、PAL视频输入/输出案例

2.高速AD(AD9613)采集+高速DA(AD9706)输出案例

3.AD9361软件无线电案例

4.UDP(10G)光口通信案例

5.UDP(1G)光口通信案例

6.Aurora光口通信案例

7.PCIe通信案例

8.案例源码、产品资料(用户手册、核心板硬件资料、产品规格书):site.tronlong.com/pfdownload

本文介绍了基于创龙科技TLK7-EVM Kintex-7开发板的LED_flash案例,详细阐述了如何利用HLS进行LED控制,每隔0.5s翻转LED2的状态。内容涵盖工程时钟配置、编译仿真以及IP核测试过程。

本文介绍了基于创龙科技TLK7-EVM Kintex-7开发板的LED_flash案例,详细阐述了如何利用HLS进行LED控制,每隔0.5s翻转LED2的状态。内容涵盖工程时钟配置、编译仿真以及IP核测试过程。

订阅专栏 解锁全文

订阅专栏 解锁全文

2085

2085

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?