时序逻辑这里不太会,主要是数电不会

触发器似乎就是用always@()语句块写就行

Exams/2014 q4a

要形成n位移位寄存器电路,不过这道题就把里面的子模块写出来就行】

子模块就是两个数据选择器和一个D触发器加上

wire temp1,temp2;//两根线

assign temp1=E?w:Q;//第一个数据选择器,选择后赋值

assign temp2=L?R:temp1;//第二个

always @(posedge clk)//时钟信号来了,就输出Q=D了,D是temp2;

begin

Q=temp2;

end

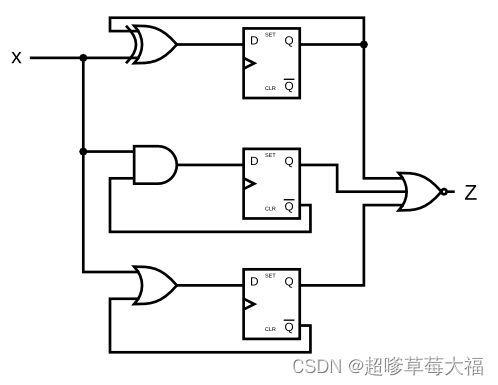

Exams/ece241 2014 q4

module top_module (

input clk,

input x,

output z

);

wire D0,D1,D2;

wire Q0,Q1,Q2;

assign D0=x ^ Q0;

assign D1=x& !Q1;

assign D2=x | !Q2;

myDFF DFF_0(clk,D0,Q0);

myDFF DFF_1(clk,D1,Q1);

myDFF DFF_2(clk,D2,Q2);

assign z=!(Q0|Q1|Q2);

endmodule

module myDFF(input clk,input d,output reg q);

always@(posedge clk)

q<=d;

endmodule

Edgedetect(边缘检测)

reg [7:0]in_1;

always @(posedge clk)begin

in_1<=in;

pedge<=~in_1∈

end

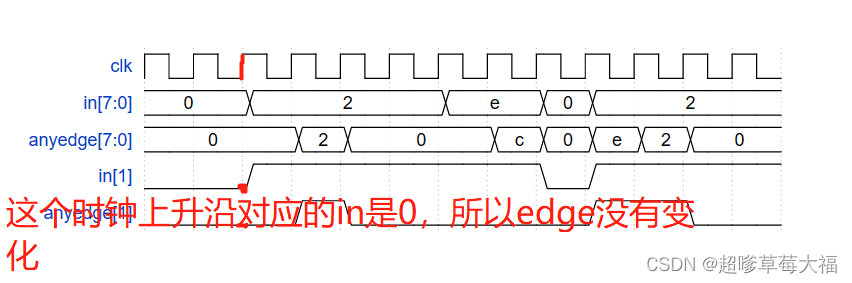

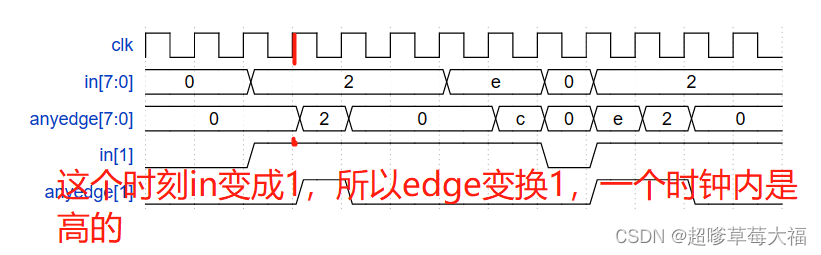

Edgedetect2

两个时钟之间,只要有0到1,或者是1到0 的变化,就会产生anyedge

所以用异或就可以实现

reg[7:0]in_1;

always@(posedge clk)begin

in_1<=in;

anyedge<=in^in_1;

end

Edgecapture

module top_module (

input clk,

input reset,

input [31:0] in,

output [31:0] out

);

reg[31:0]in_1;

always@(posedge clk)begin

in_1<=in;

if(reset)

out<=32'b0;

else

out<=(~in&in_1)|out;

end

endmodule

这篇博客探讨了FPGA开发中的时序逻辑,重点讲解了如何构建移位寄存器,包括使用D触发器和数据选择器。同时,还介绍了边缘检测的概念及其在不同场景的应用,如Edgedetect和Edgecapture模块的实现。

这篇博客探讨了FPGA开发中的时序逻辑,重点讲解了如何构建移位寄存器,包括使用D触发器和数据选择器。同时,还介绍了边缘检测的概念及其在不同场景的应用,如Edgedetect和Edgecapture模块的实现。

246

246

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?