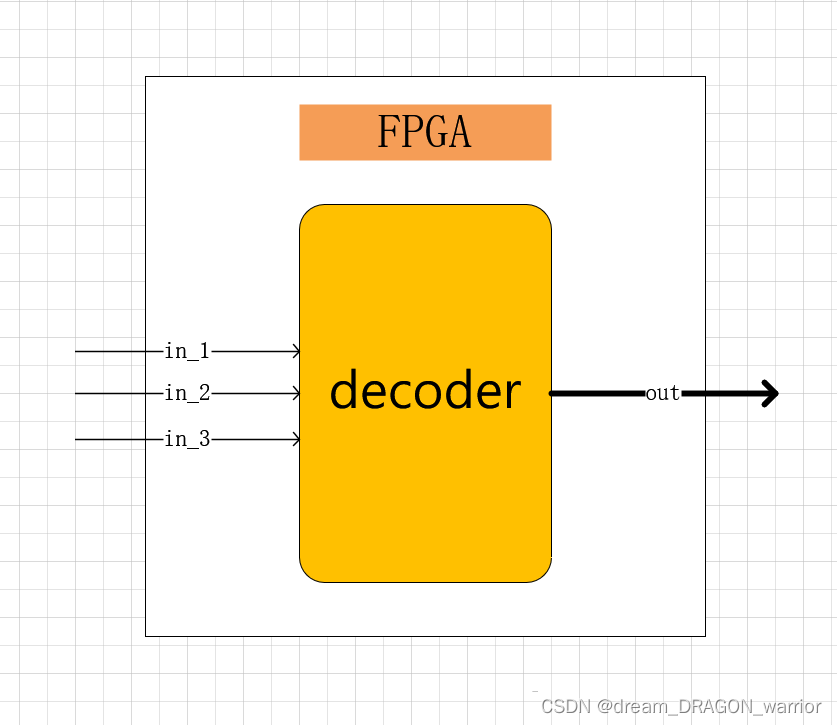

module decoder(

input wire in_1 ,

input wire in_2 ,

input wire in_3 ,

output reg [07:00] out

);

always @(*) begin

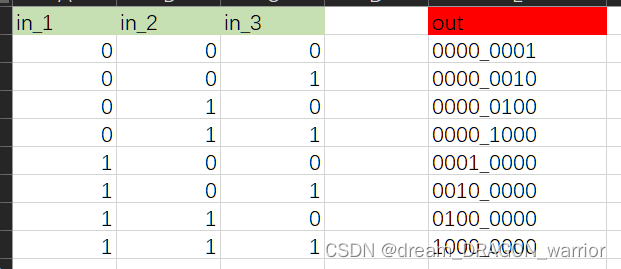

case ({in_1, in_2, in_3})

3'b000 : begin

out = 8'b0000_0001 ;

end

3'b001 : begin

out = 8'b0000_0010 ;

end

3'b010 : begin

out = 8'b0000_0100 ;

end

3'b011 : begin

out = 8'b0000_1000 ;

end

3'b100 : begin

out = 8'b0001_0000 ;

end

3'b101 : begin

out = 8'b0010_0000 ;

end

3'b110 : begin

out = 8'b0100_0000 ;

end

3'b111 : begin

out = 8'b1000_0000 ;

end

default: out = 8'hzz ;

endcase

end

endmodule

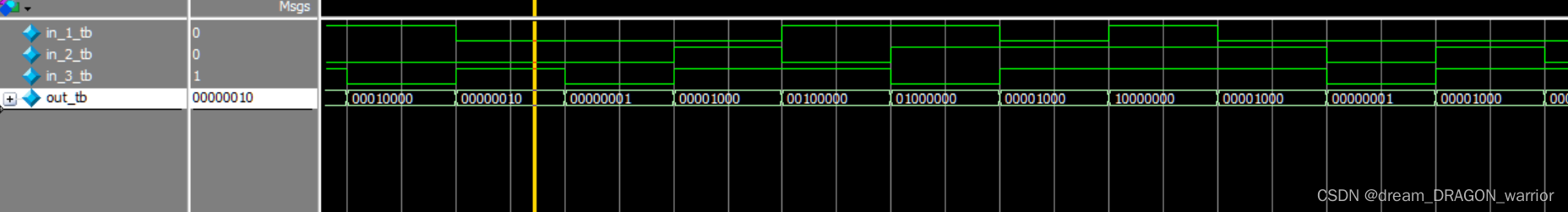

`timescale 1ns/1ps

module test();

reg in_1_tb ;

reg in_2_tb ;

reg in_3_tb ;

wire [07:00] out_tb ;

decoder decoder_insert(

.in_1 ( in_1_tb ) ,

.in_2 ( in_2_tb ) ,

.in_3 ( in_3_tb ) ,

.out ( out_tb )

);

parameter CYCLE = 20 ;

initial begin

in_1_tb = 1'b1 ;

in_2_tb = 1'b1 ;

in_3_tb = 1'b1 ;

#( CYCLE * 1000) ;

$stop;

end

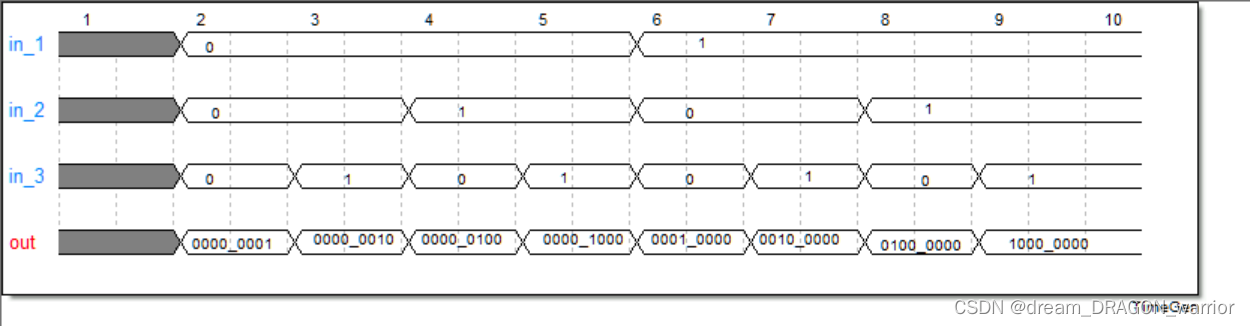

always #( CYCLE ) in_1_tb = ($random) % 2 ;

always #( CYCLE ) in_2_tb = ($random) % 2 ;

always #( CYCLE ) in_3_tb = ($random) % 2 ;

initial begin

$timeformat(-9,0,"ns",6) ;

$monitor("@time %t:in_1_tb=%b,in_2_tb=%b,in_3_tb=%b,out=%b",$time,in_1_tb,in_2_tb,in_3_tb,out_tb) ; // 监测函数

end

endmodule

该篇文章详细描述了一个Verilog设计,包括一个名为`decoder`的模块,它根据输入的3位二进制代码生成8位输出。同时,文中还展示了如何创建一个测试用例(testbench),使用随机输入来验证模块功能并监控输出。

该篇文章详细描述了一个Verilog设计,包括一个名为`decoder`的模块,它根据输入的3位二进制代码生成8位输出。同时,文中还展示了如何创建一个测试用例(testbench),使用随机输入来验证模块功能并监控输出。

2640

2640