74LS138 decoder works as follows:

When one gating terminal (G1) is high and the other two gating terminals (/(G2A) and /(G2B)) are low, the binary encoding of the address terminals (A, B, C) can be translated at low levels on a corresponding output terminal.

code:

module decoder(

input G1 ,

input G2A ,

input G2B ,

input [2:0] ABC ,

output reg [7:0] Y_7_0

);

always@(*)begin

if(G1 == 0 )begin

Y_7_0 = 8'hFF ;

end else begin

if(~(G2A || G2B))begin

case (ABC)

3'b000 : Y_7_0 = 8'b0111_1111 ;

3'b001 : Y_7_0 = 8'b1011_1111 ;

3'b010 : Y_7_0 = 8'b1101_1111 ;

3'b011 : Y_7_0 = 8'b1110_1111 ;

3'b100 : Y_7_0 = 8'b1111_0111 ;

3'b101 : Y_7_0 = 8'b1111_1011 ;

3'b110 : Y_7_0 = 8'b1111_1101 ;

3'b111 : Y_7_0 = 8'b1111_1110 ;

default: Y_7_0 = 8'hZZ ;

endcase

end else begin

Y_7_0 = 8'hFF ;

end

end

end

// another way :

// always @(posedge clk or negedge rst_n) begin

// if(~rst_n)begin

// dout <= dout <= 3'b000 ;

// end esle begin

// if(din[0])

// dout <= 3'b000 ;

// else if(din[1])

// dout <= 3'b001 ;

// else if(din[2])

// dout <= 3'b010 ;

// else if(din[3])

// dout <= 3'b011 ;

// else if(din[4])

// dout <= 3'b100 ;

// else if(din[5])

// dout <= 3'b101 ;

// else if(din[6])

// dout <= 3'b101 ;

// else if(din[7])

// dout <= 3'b111 ;

// else dout <= 3'b00 ;

// end

// end

endmodule

testbench :

`timescale 1ns/1ps

module test_tb ();

reg G1_tb ;

reg G2A_tb ;

reg G2B_tb ;

reg [2:0] ABC_tb ;

wire [7:0] Y_7_0_tb ;

decoder decoder_inst(

.G1 ( G1_tb ) ,

.G2A ( G2A_tb ) ,

.G2B ( G2B_tb ) ,

.ABC ( ABC_tb ) ,

.Y_7_0 ( Y_7_0_tb )

);

parameter CYCLE = 20 ;

initial begin

#(CYCLE * 10 ) ;

G1_tb = 1'b0 ;// Simulate the first row of the truth table

G2A_tb = 1'bx ;

G2B_tb = 1'bx ;

#(CYCLE * 10 ) ;

G1_tb = 1'bx ;// Simulate the sceond row of the truth table

G2A_tb = 1'b1 ;

G2B_tb = 1'b1 ;

#(CYCLE * 10 ) ;

G1_tb = 1'b0 ;// Simulate the case when G1 is not 1

G2A_tb = 1'b0 ;

G2B_tb = 1'b1 ;

ABC_tb = 3'b010 ;

#(CYCLE * 10 ) ;

G1_tb = 1'b1 ;//Simulate the case when G1 is 1 ,when G2 and G3 are in phase or 1

G2A_tb = 1'b0 ;

G2B_tb = 1'b1 ;

#(CYCLE * 10 ) ;

G1_tb = 1'b1 ;

G2A_tb = 1'b0 ;

G2B_tb = 1'b0 ;// Simulate the normal output situation

#(CYCLE * 10 ) ;

ABC_tb = 3'b011 ;// change value

#(CYCLE * 10 ) ;

$stop ;

end

endmodule

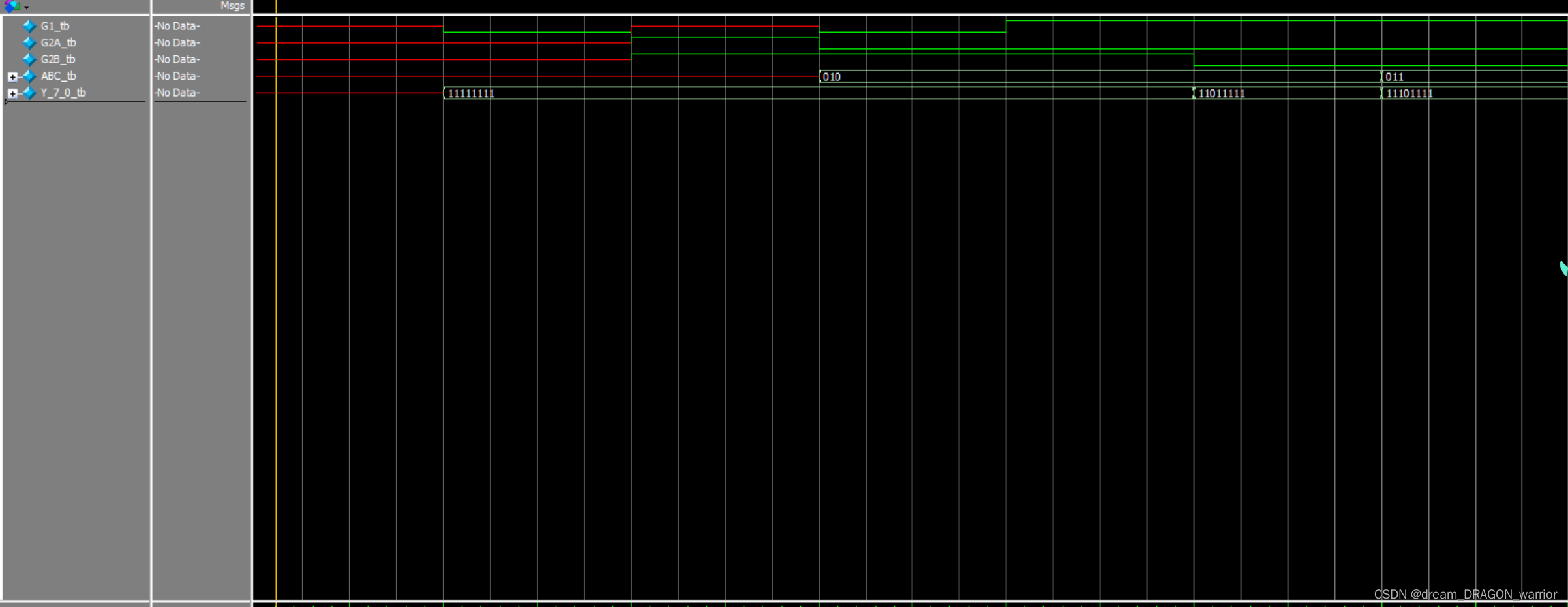

simulation waveform :

这篇文章详细描述了74LS138译码器的工作原理,当特定输入条件满足时如何将二进制地址转换为对应的输出。测试部分展示了如何使用模拟来验证不同输入组合下的行为。

这篇文章详细描述了74LS138译码器的工作原理,当特定输入条件满足时如何将二进制地址转换为对应的输出。测试部分展示了如何使用模拟来验证不同输入组合下的行为。

236

236