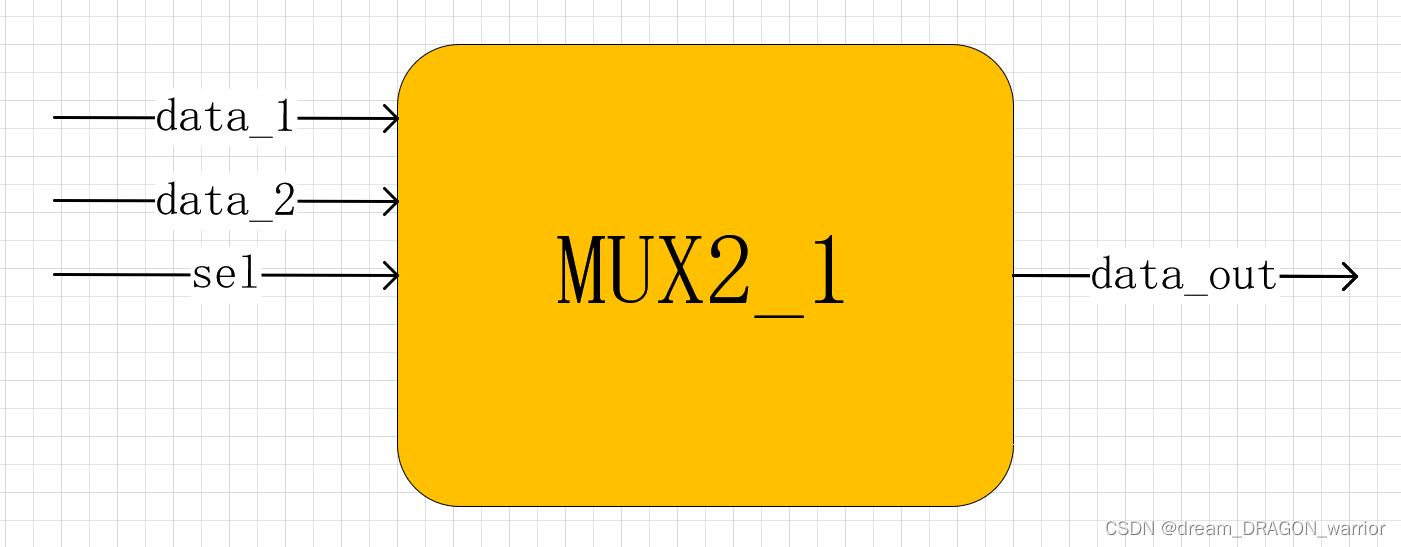

module mux2_1 (

input wire [0:0] data_1 ,

input wire [0:0] data_2 ,

input wire [0:0] sel ,

output reg [0:0] data_out

);

// method 1

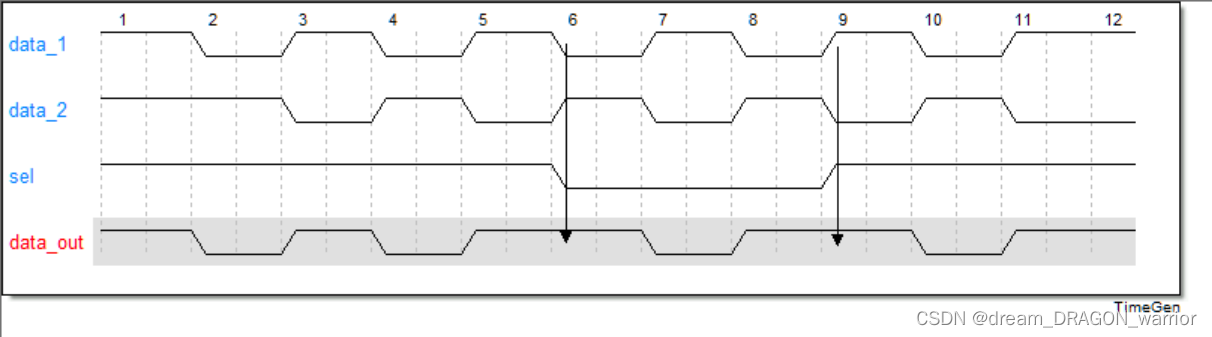

always @(*) begin

if(sel == 1'b1) begin

data_out = data_1 ;

end else begin

data_out = data_2 ;

end

end

// method 2

always @(*) begin

case (sel)

0 : begin

data_out = data_1 ;

end

1 : begin

data_out = data_2 ;

end

default: data_out = data_1 ;

endcase

end

// method 3

data_out = ( sel == 1'b1 ) ? data_1 : data_2 ;

endmodule

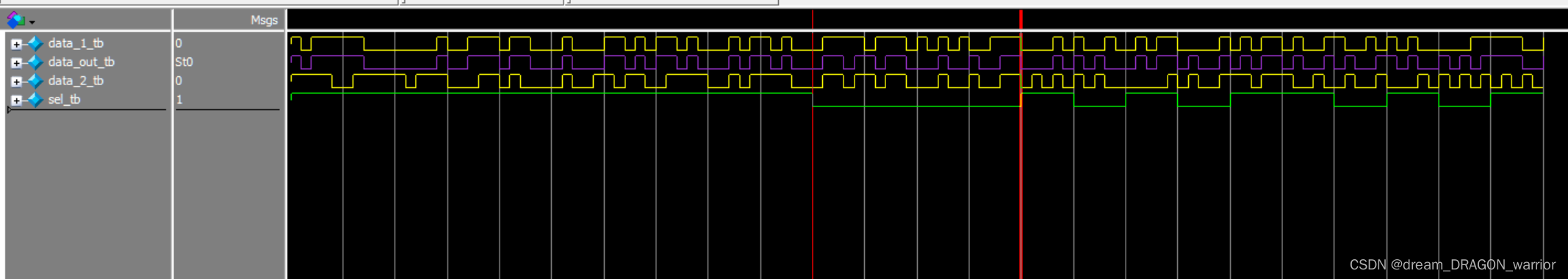

`timescale 1ps/1ps

module test();

reg [0:0] data_1_tb ;

reg [0:0] data_2_tb ;

reg [0:0] sel_tb ;

wire [0:0] data_out_tb ;

mux2_1 mux2_1_insert(

.data_1 ( data_1_tb ) ,

.data_2 ( data_2_tb ) ,

.sel ( sel_tb ) ,

.data_out ( data_out_tb)

);

parameter CYCLE = 20 ;

initial begin

data_1_tb = 1'b1 ;

data_2_tb = 1'b1 ;

sel_tb = 1'b1 ;

end

always #(CYCLE) data_1_tb <= {$random} % 2 ;

always #(CYCLE) data_2_tb <= {$random} % 2 ;

always #(CYCLE * 5) sel_tb <= {$random} % 2 ;

endmodule

exercises for improvement :

module MUX8_1 (

input wire [07:00] data_1 ,

input wire [07:00] data_2 ,

input wire [07:00] data_3 ,

input wire [07:00] data_4 ,

input wire [07:00] data_5 ,

input wire [07:00] data_6 ,

input wire [07:00] data_7 ,

input wire [07:00] data_8 ,

input wire [02:00] sel ,

output reg [07:00] data_out

);

/* always @(*) begin

case (sel)

3'b000 : begin

data_out = data_1 ;

end

3'b001 : begin

data_out = data_2 ;

end

3'b010 : begin

data_out = data_3 ;

end

3'b011 : begin

data_out = data_4 ;

end

3'b100 : begin

data_out = data_5 ;

end

3'b101 : begin

data_out = data_6 ;

end

3'b110 : begin

data_out = data_7 ;

end

3'b111 : begin

data_out = data_8 ;

end

default: data_out = data_1 ;

endcase

end */

/* always@(*) begin

if(sel == 3'b000)

data_out = data_1 ;

else if(sel == 3'b001)

data_out = data_2 ;

else if(sel == 3'b010)

data_out = data_3 ;

else if(sel == 3'b011)

data_out = data_4 ;

else if(sel == 3'b100)

data_out = data_5 ;

else if(sel == 3'b101)

data_out = data_6 ;

else if(sel == 3'b110)

data_out = data_7 ;

else if(sel == 3'b111)

data_out = data_8 ;

else

data_out = data_1 ;

end */

wire [07:00] data_out_w ;

assign data_out_w = (sel == 3'b000) ? data_1 : (sel == 3'b001) ? data_2 : (sel == 3'b010) ? data_3 : (sel == 3'b011) ? data_4 : (sel == 3'b100) ? data_5 : (sel == 3'b101) ? data_6 : (sel == 3'b110) ? data_7 : (sel == 3'b111) ? data_8 : data_1 ;

always @(*) begin

data_out = data_out_w ;

end

endmodule

博客提及FPGA开发的提升练习,但未给出具体内容。FPGA开发是信息技术领域重要部分,相关练习有助于提升开发能力。

博客提及FPGA开发的提升练习,但未给出具体内容。FPGA开发是信息技术领域重要部分,相关练习有助于提升开发能力。

3924

3924