这章节描述了对于多样的输入、输出路径的时序分析流程,以及几个常用的接口。特殊端口的时序分析,如SRAM;以及对于源同步接口的时序分析,也有讲到,如DDR SDRAM。

目录

输入路径的延迟指定 (Path Delay Specification to Inputs)

输出路径的延迟指定(External Path Delays for Output)

9.1 IO接口

本小节展示了如何对DUA的输入输出接口进行约束。晚些将会讲到对于SRAM DDR SDRAM的时序约束。

9.1.1 输入接口

有两种方法指定输入接口的时序

- 以AC特性的形式指定DUA输入端口的波形

- 指定了连接输入端口的外部逻辑的路径延时

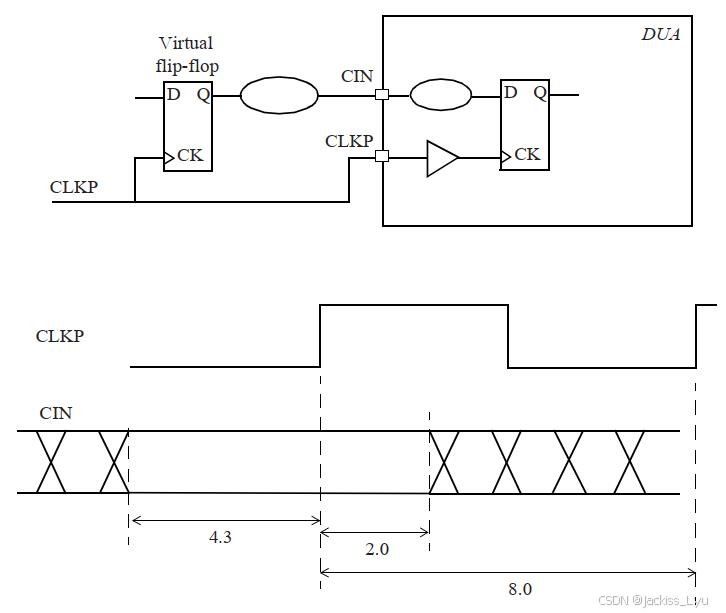

指定输入端口的波形

指定的波形中,在CLKP的上升沿到来之前,CIN保持4.3ns的稳定,并且持续到上升沿之后的2ns。考虑8ns的周期,从虚拟触发器到CIN的组合逻辑所用时间最多为3.7ns(最大延时)。这可以保证数据在上升沿到来前4.3ns就保持了稳定。因此,这部分延时的指定,也可以指定为外部输入延时最大为3.7ns。在上升沿之后,数据需要保持2ns的稳定。这也意味着从外部虚拟触发器到CIN端口的延时至少为2.0ns。因此,这部分延时的指定,也可以指定为外部输入延时最小为2ns。

这部分可以这样理解:外部输入延时最大为3.7ns,如果大于了3.7ns,那么对于下一个捕获有效沿,就无法使得CIN端口提前4.3ns稳定。外部输入延时最小为2ns,如果小于了2ns,那么对于同一时刻的捕获有效沿,有可能造成重写的问题。所以最大外部延时为3.7ns,最小外部延时为2ns。

create_clock -name CLKP -period 8 [get_ports CLKP]

set_input_delay -min 2.0 -clock CLKP [get_ports CIN]

set_input_delay -max 3.7 -clock CLKP [get_ports CIN]

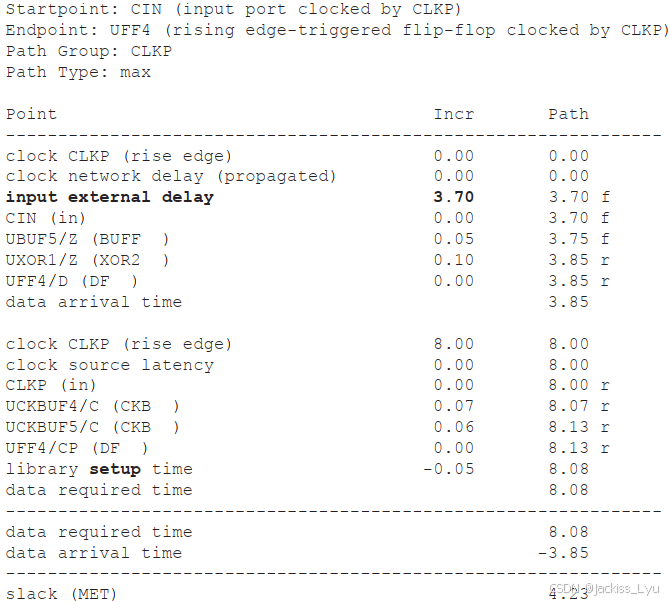

建立时间检查DUA内部的延时小于4.3ns,触发器可以捕获正确的数据。下面是保持时间报告:

![]()

这个保持时间检查保证最早的数据在有效边沿过去后的2ns发生变化,不会重写前面的数据。

输入路径的延迟指定 (Path Delay Specification to Inputs)

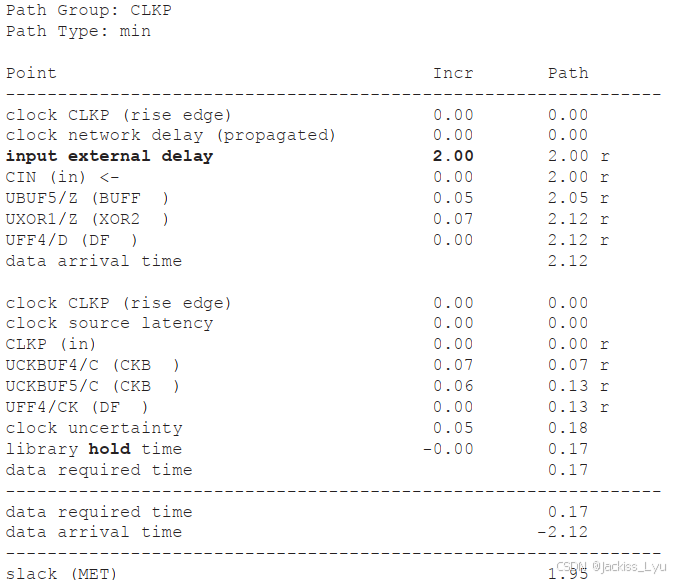

当连接了输入端口的外部组合逻辑的延时知道后,这项任务就变的简单了。任何沿着外部组合逻辑路径的延时都会被加起来,延时是使用set_input_delay指令进行指定的。

上图中,Tck2q Tc1的延时被加起来用来计算外部延时,两者加起来即可。下面指定的延时是INIT端口相对于RCLK端口的延时。

create_clock -name RCLK -period 10 [get_ports RCLK]

set_input_delay -max 6.2 -clock RCLK [get_ports INIT]

set_input_delay -min 3.0 -clock RCLK [get_ports INIT]时序报告与先前的类似。注意,当计算设计内部触发器的数据引脚的数据到达时间的时候,计算得到最大延时还是最小延时,取决于进行的是最大延时路径检查(setup),还是最小延时路径检查(hold)。如上图中,max为6.2,那么就要考虑能否满足紧接着的下个时钟沿的建立时间要求;min为3,那么就要考虑是否数据传输的过快,会对相同时钟边沿捕获的数据造成重写的问题。

9.1.2 输出接口

同样也有两种方法用来指定输出端口的时序要求

- 以AC特性的形式指定DUA输出端口的波形

- 指定了连接输出端口的外部逻辑的路径延时

指定输出端口的波形

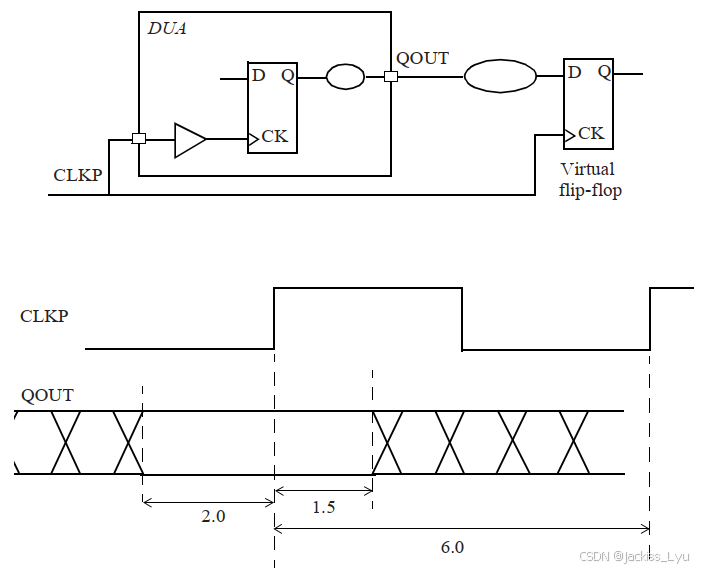

下图中,输出端口QOUT的数据应在CLKP的时钟沿到来前保持2ns稳定,在时钟沿到来后再保持1.5ns稳定。通常可以要求连接QOUT的外部逻辑的建立、保持时间来满足以上的约束值。

下面是对于端口的约束条件,输出路径的最大延时指定为2ns,这将会保证QOUT在2ns的窗口期之前变化。输出路径的最小延时指定为-1.5ns,用来确保输出QOUT上1.5ns的保持时间需求。解释一下,就是QOUT在CLKP下一个上升沿到来之前2ns已经稳定,所以外部延时QOUT相对于CLKP为2.0。QOUT在上升沿到来之后1.5ns仍然能稳定,所以为了满足保持时间的要求(也就是不被重写),QOUT相对于CLKP为-1.5ns。

create_clock -name CLKP -period 6 \

-waveform {0 3} [get_ports CLKP}

# Setup delay of virtual flip-flop:

set_output_delay -clock CLKP -max 2.0 [get_ports QOUT]

# Hold time for virtual flip-flop:

set_output_delay -clock CLKP -min -1.5 [get_ports QOUT]

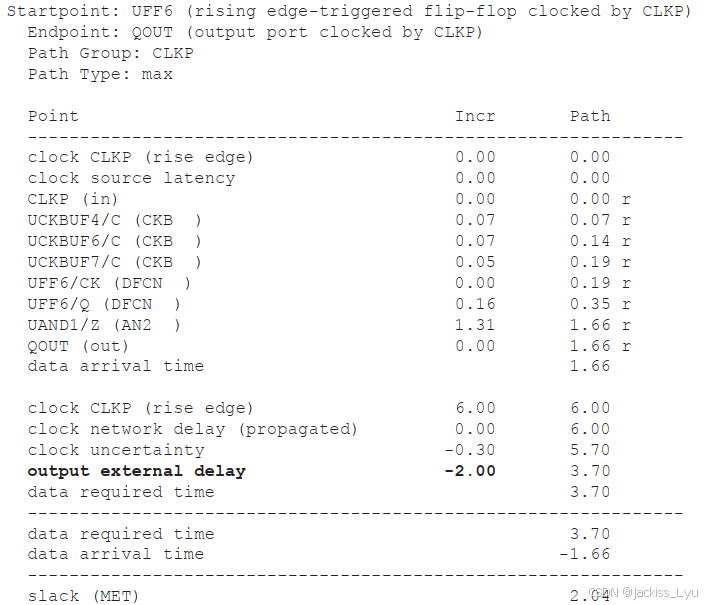

建立时间检查, 将会从下个时钟沿减去外部延时,来确定数据的到达时间是否满足要求。

最小的输出路径延时将会从捕获时钟边沿减去,用来检查DUA输出端口的最早的到达时间能否满足保持时间的要求。上面的保持时间报告中,数据1.02ns就到了,但是要求数据最早1.55ns到,所以违例了。因为无法保证QOUT在1.55ns内保持稳定。

输出路径的延迟指定(External Path Delays for Output)

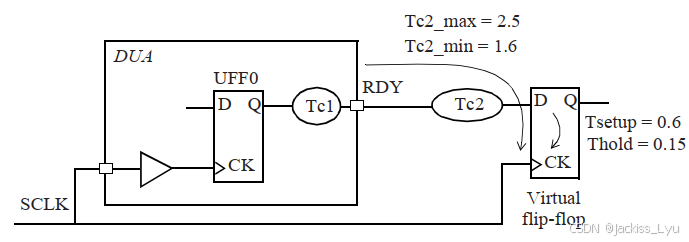

在这例子中,外部逻辑的路径延时被显式的指定了出来。

最大的输出延时设定,从Tc2_max和Tsetup获得。为了完成DUA内部触发器和虚拟触发器之前的建立时间检查,最大的输出延时将会指定为Tc2_max + Tsetup。最小的路径延时由Tc2_min和Thold获得。由于捕获触发器的保持时

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8815

8815

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?