目录

8.9 例子

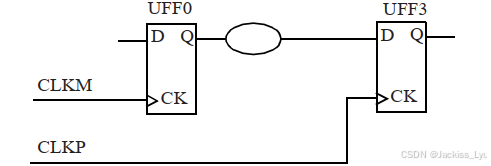

半周期路径 - 例1

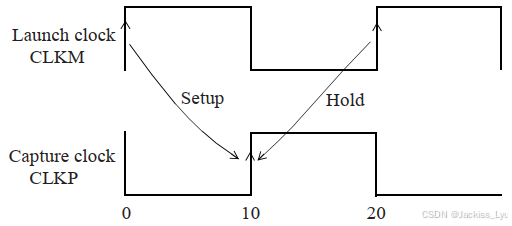

这个例子中,俩个时钟周期相同但是是反相的,代码指定如下,波形见图。

create_clock -name CLKM \

-period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP \

-period 20 -waveform {10 20} [get_ports CLKP]

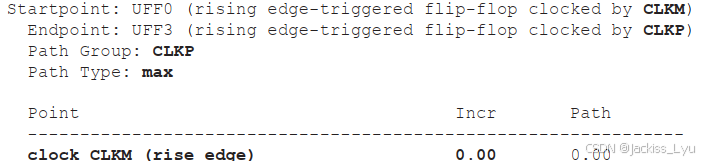

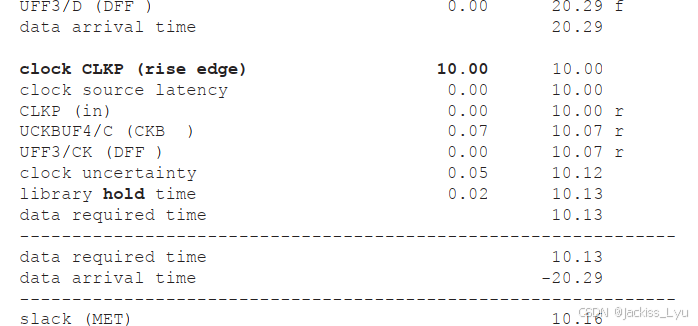

建立检查在0ns的发射边沿,到下个捕获边沿,在10ns。半个时钟周期的裕量可以用于保持时间检查,从而去验证在20ns发射的数据没有被10ns的捕获边沿捕获。下面是报告。

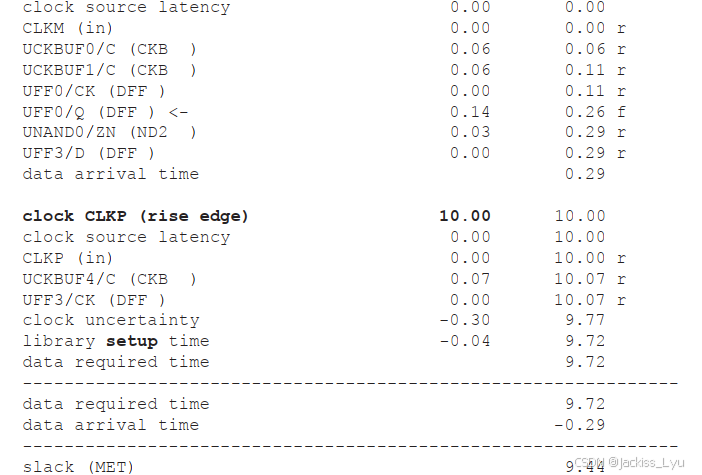

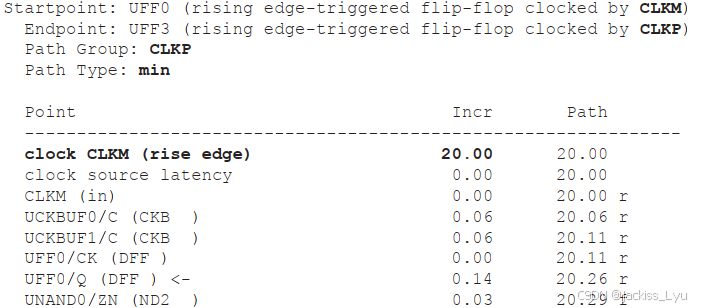

下面是保持时间检查报告:

半周期路径 - 例2

这个例子与例1类似,只不过将发射时钟在时间轴进行了平移。

create_clock -name CLKM \

-period 10 -waveform {5 10} [get_ports CLKM]

create_clock -name CLKP \

-period 10 -waveform {0 5} [get_ports CLKP]

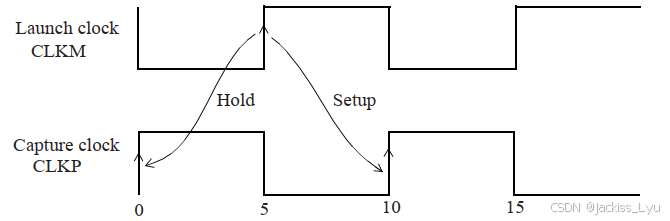

建立时间检查是从5ns的发射时钟边沿到到下一个10ns的捕获边沿。保持时间检查是从5ns的发射时钟边沿,到前一个0ns的捕获边沿。

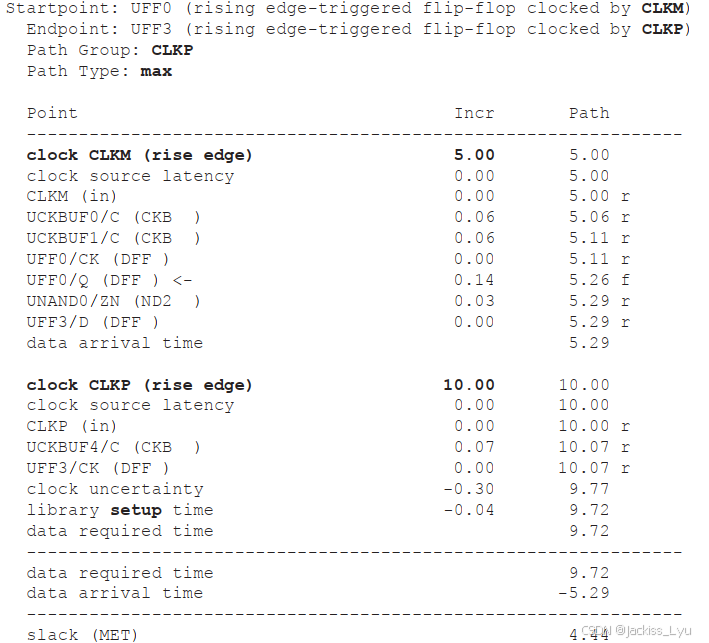

下面是保持时间报告:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5971

5971

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?