前一篇文章:STA 静态时序分析 第八章——时序检查(1)

目录

8.3 多周期路径

某些情况下,两个触发器之间的组合逻辑路径需要多于一个时钟周期来传播,这就是多周期路径。即使捕获寄存器的在每个有效时钟边沿都捕获了数据,但是我们仍需告诉STA在特定数目的周期才会出现有效(相关)的时钟边沿。

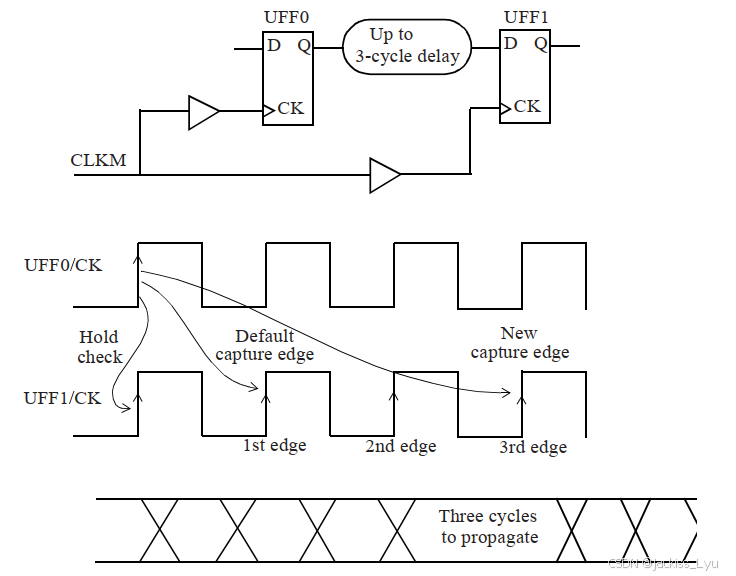

下图中例子,数据路径需要3个时钟周期才能传播,建立时间多周期检查,应当被指定为3周期。多周期建立时间约束,如下所示。

create_clock -name CLKM -period 10 [get_ports CLKM]

set_multicycle_path 3 -setup \

-from [get_pins UFF0/Q] \

-to [get_pins UFF1/D]"设置多周期约束"指定了从 UFF0/CK 到 UFF1/D 的路径完成需要最多三个时钟周期。这意味着设计每隔三周期才会使用来自 UFF1/Q 的数据,而不是每个周期都使用。

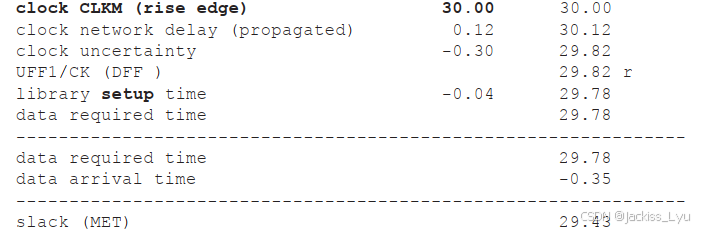

报告中的30ns意味着,三个周期才会使用一次数据。不要将其想象为流水线,中间不是分阶段的。

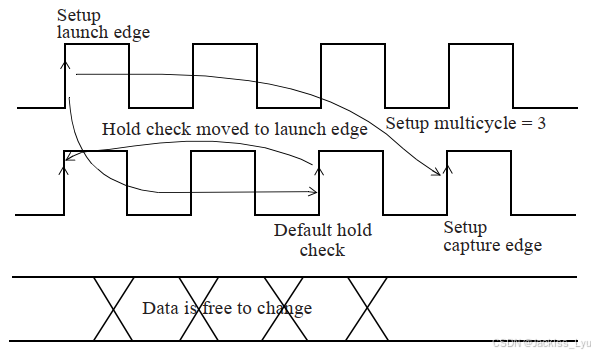

下面进行保持时间检查。 在大多数情况下,我们想让他如同在单周期路径中一样去检查他,就像上面的电路图所示。这样可以保证数据在三个时钟周期的时间里可以自由改变。只有指定多周期保持时间为2,才可以获得与单周期建立时间检查情况相同的保持时间检查。这是因为若没有这个多周期保持时间的设定,默认的保持时间检查将在建立时间检查有效边沿前一周期的有效沿处进行,这不是我们想要的。需要将保持时间检查移动至默认保持时间检查沿的前两个时钟周期,因此多周期保持时间指定为2。预想的行为如下图所示。有了多周期保持时间,数据路径的最小延迟可以比一个时钟周期更短。

set_multicycle_path 2 -hold -from [get_pins UFF0/Q] \

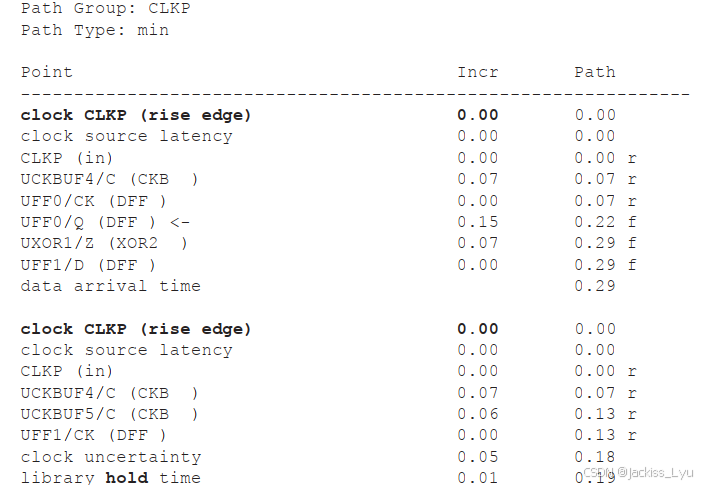

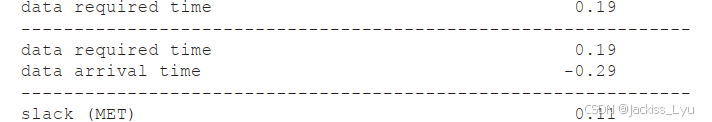

-to [get_pins UFF1/D]多周期保持(multicycle hold)中标示的周期数指定了从默认的保持检查边缘(即在设置捕获边缘之前的一个有效边缘)向回推移多少个时钟周期。以下是路径报告。

![]()

![]()

在这个时序报告中,注意到保持时间检查在捕获沿的前一有效时钟沿进行,导致了很大的违例。实际上,保持时间检查要求组合逻辑电路的时延要在两个时钟周期及以上。

时钟域的交叉

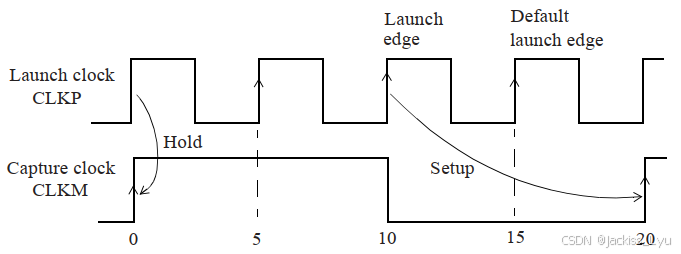

如果存在周期相同的两个时钟之间的多周期路径。

create_clock -name CLKM \

-period 10 -waveform {0 5} [get_ports CLKM]

create_clock -name CLKP \

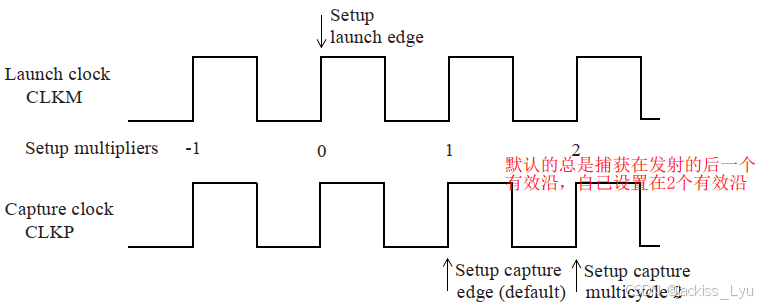

-period 10 -waveform {0 5} [get_ports CLKP]setup multicycle multiplier 代表了对于一条给定的路径上的时钟周期数。

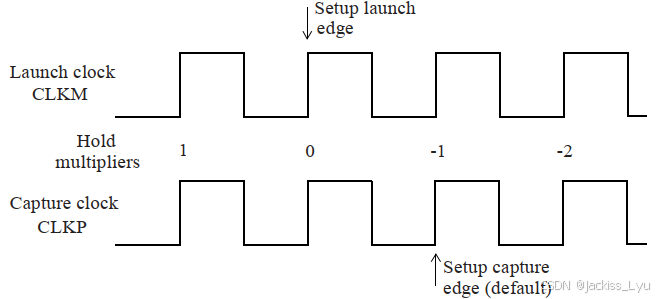

hold multicycle multiplier 代表了在建立捕获有效沿之前的时钟周期数,此时不管发射的有效边沿。默认的边沿总是在捕获沿的前一个,如果设置为1,就将默认边沿前推一个周期,因此就会领先捕获有效沿两个周期,如下图所示。

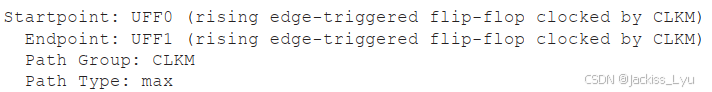

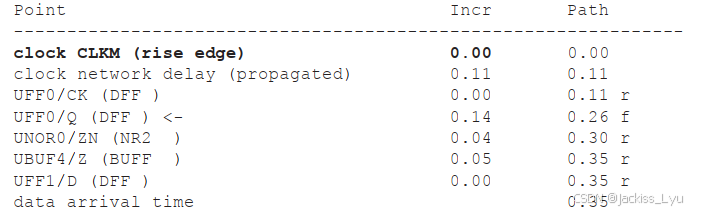

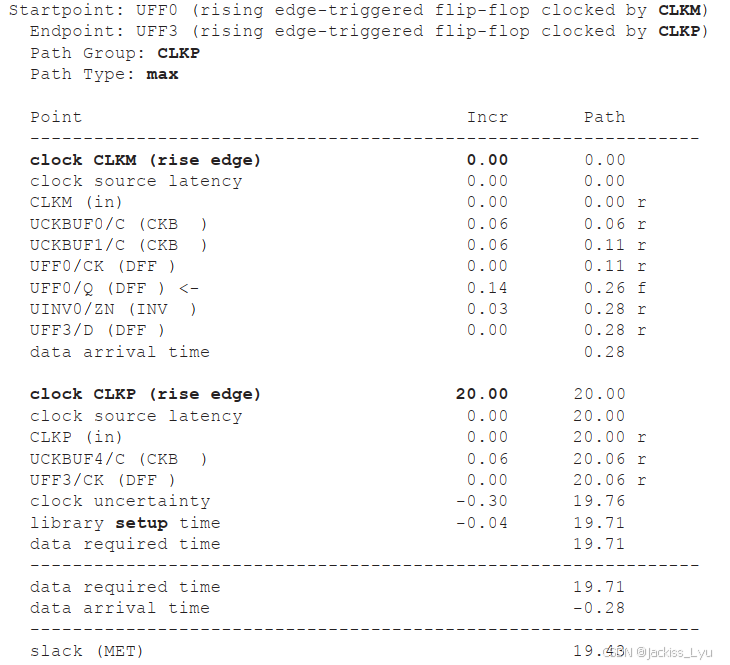

下面是建立时间检查所对应的时序报告。

STA静态时序分析:多路径与时序问题

STA静态时序分析:多路径与时序问题

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5947

5947

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?