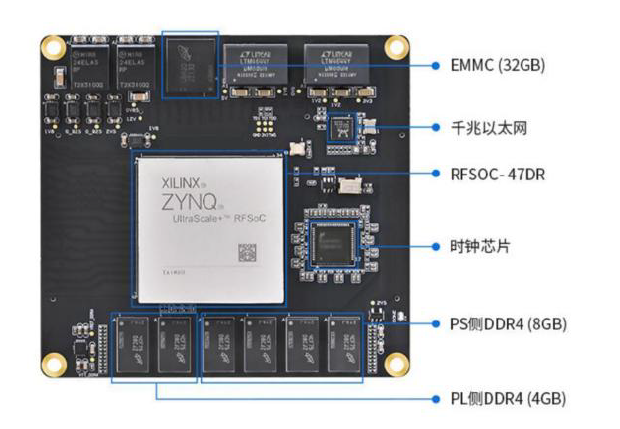

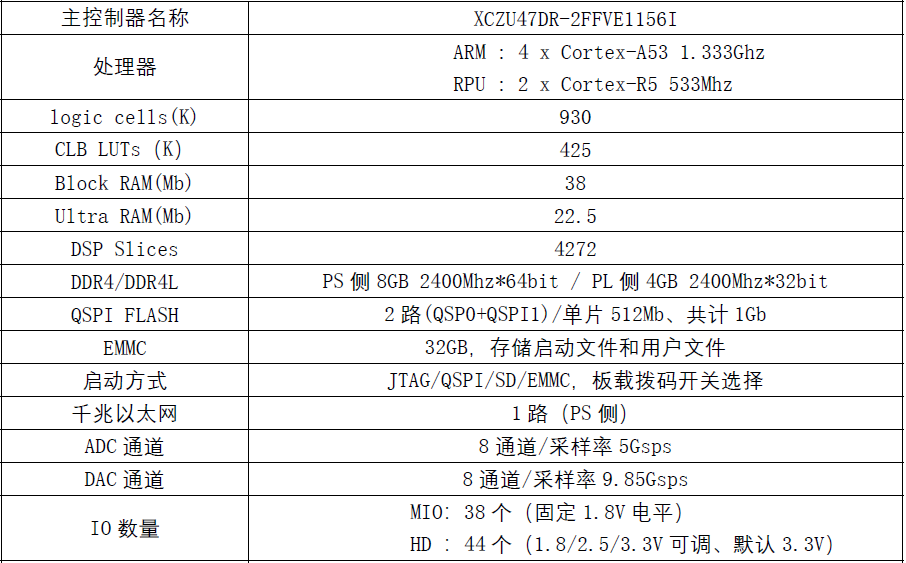

采用XILINX的XCZU47DR-2FFVE1156I处理器,拥有8个RF-ADC、8个RF-DAC通道。提供完整的应用示例源代码和性能分析工具,主要用于小尺寸、低功耗、实时处理RF系统的快速集成与应用部署,缩短产品开发周期,提供了丰富的板载资源。

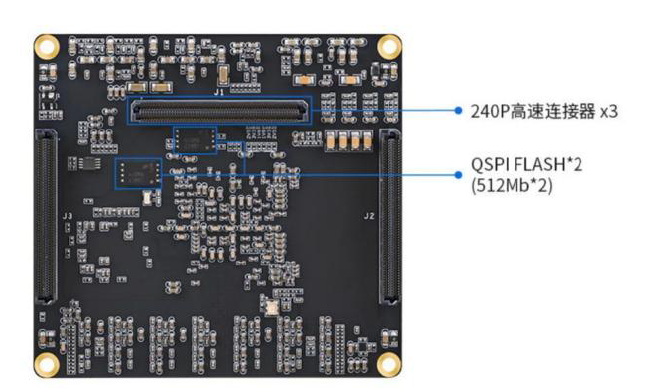

如下列出了核心板所有板载资源,以及核心板的尺寸信息。

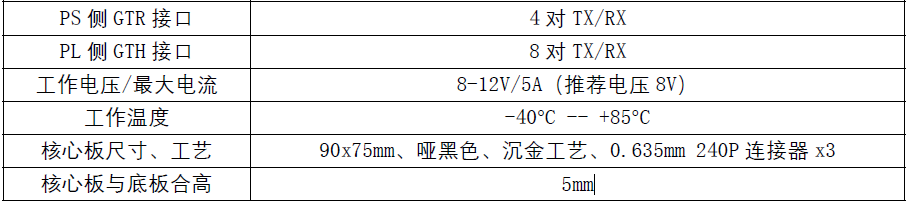

核心板供电

核心板供电电压范围是8-12V,推荐供电电压为8V,在核心板的两个角都留有电

源输入管脚,电源管脚在模块内部已做了连通,此设计是为了方便底板的电源接入,

设计时只需要连接一个角上的电源管脚,核心板即可工作。电源连接需用铜皮连接且

打足够的过孔以保证电源通流能力。核心板上的所有GND 信号都需要连接到底板上,

每个GND 通过两个过孔与底板连接。核心板供电极限电流在5A,所以外部供电需要

考虑极限电流情况以保证核心板工作稳定。

给模组供电的电源输出电压需要稳定,在模组电源输入加一级DCDC 电源转换,

从高电压转到8-12V(推荐8V),DCDC 电流输出能力可以选6A 及以上。在模组电源输

入处需放置2 颗220uF/25V 电容保证电源质量。

核心板时钟

核心板为 PS 侧提供了 33.333333Mhz 的时钟输入,输入的管脚位置为 PS_REF_CLK;

为PL 侧提供了200Mhz 的差分时钟输入, PL 侧的时钟输入管脚是

IO_13P_GC_66/IO_13N_GC_66,管脚位置是 AL9/AM9;另外 ZU47DR 其他部分我们采用了专

用的时钟芯片产生ADC/DAC/GT/PL 端各个部分的时钟需求,如下图分别列出了各部分时钟

的管脚连接。

核心板启动方式

主芯片支持JTAG、QSPI Flash,SD,EMMC四种启动模式,四种启动模式可以根 开

据发板上的拨码开关选择,更详细说明可参考提供的核心板原理图。

685

685

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?