注意:纯属个人学习笔记,初学者,后续会进行完善修改,参考gitee上《从零开始写RISC-V处理器》。

1、用always描述组合逻辑电路时要注意避免产生锁存器,if和case的分支情况要写全。

2、流水线设计:采用流水线设计方式,不但可以提高处理器的工作频率,还可以提高处理器的效率。但是流水线并不是越长越好,流水线越长要使用的资源就越多、面积就越大。

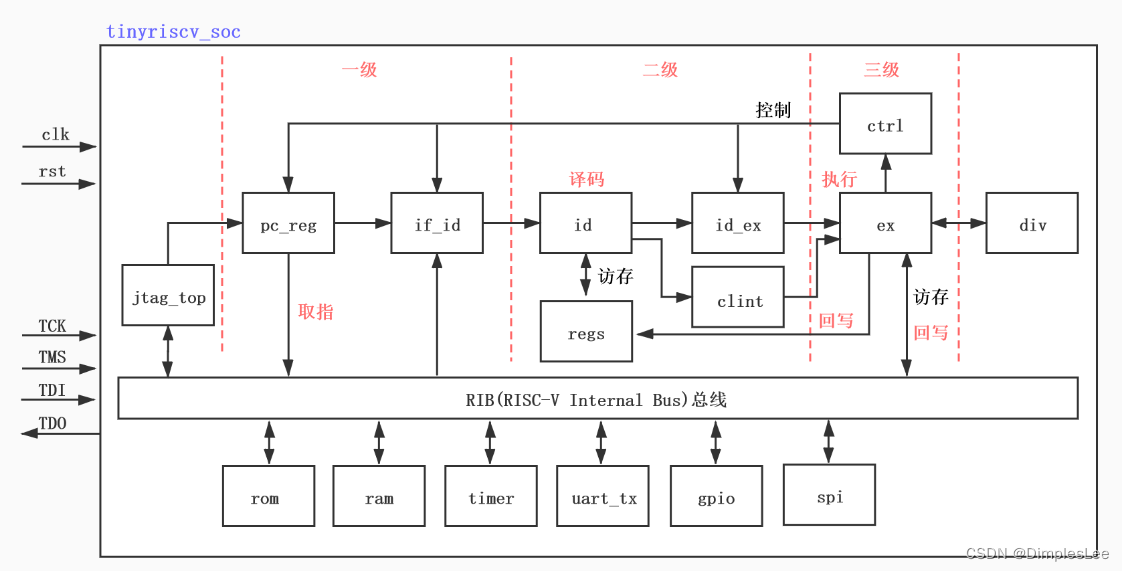

3、tinyriscv采用的是三级流水线,即取指、译码和执行,设计的目标就是要对标ARM的Cortex-M3系列处理器。

tinyriscv整体框架

tinyriscv SOC输入输出信号有两部分,一部分是系统时钟clk和复位信号rst,另一部分是JTAG调试信号,TCK、TMS、TDI和TDO。

下面简单介绍每个模块的主要作用。

jtag_top:调试模块的顶层模块,主要有三大类型的信号,第一种是读写内存的信号,第二种是读写寄存器的信号,第三种是控制信号,比如复位MCU,暂停MCU等。

pc_reg:PC寄存器模块,用于产生PC寄存器的值,该值会被用作指令存储器的地址信号。

if_id:取指到译码之间的模块,用于将指令存储器输出的指令打一拍后送到译码模块。

id:译码模块,纯组合逻辑电路,根据if_id模块送进来的指令进行译码。当译码出具体的指令(比如add指令)后,产生是否写寄存器信号,读寄存器信号等。由于寄存器采用的是异步读方式,因此只要送出读寄存器信号后,会马上得到对应的寄存器数据,这个数据会和写寄存器信号一起送到id_ex模块。

id_ex:译码到执行之间的模块,用于将是否写寄存器的信号和寄存器数据打一拍后送到执行模块。

ex:执行模块,纯组合逻辑

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1729

1729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?