SR(Set/Reset)锁存器

- 由一对交叉耦合的或非门组成

- R=1,S=0,Q复位为0

- R=0,S=1,Q置位为1

- R=0,S=0,Q保持之前的值

- R=1,S=1,是无效状态,必须想办法避免

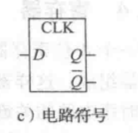

D锁存器

- 因为SR锁存器会有无效状态,使用不便,且输入S和R混淆了时间和内容,当输入有效时,不仅要确定内容是什么,还要确定是何时。将内容与时间分开考虑使电路设计变得简便。

- D锁存器解决了这个问题,D是数据输入,用来控制下一个状态的值,CLK是时钟输入,控制状态发生改变的时间

- CLK为0,输出会保持之前的状态(阻塞的,不透明的opaque)

- CLK为1,输出Q的状态与D相同(透明的transparent)

- D锁存器又称透明锁存器或电平敏感锁存器

本文介绍了锁存器和触发器的基础知识,包括SR锁存器、D锁存器和D触发器的工作原理。SR锁存器由交叉耦合的或非门组成,存在无效状态。D锁存器解决了无效状态问题,数据输入D决定输出Q的值,时钟输入CLK控制状态变化。D触发器由两个反相时钟控制的D锁存器构成,实现边沿触发,确保在时钟上升沿复制D到Q。此外,文章还提到了电平敏感与边沿触发的区别,以及寄存器在时序电路中的作用。

本文介绍了锁存器和触发器的基础知识,包括SR锁存器、D锁存器和D触发器的工作原理。SR锁存器由交叉耦合的或非门组成,存在无效状态。D锁存器解决了无效状态问题,数据输入D决定输出Q的值,时钟输入CLK控制状态变化。D触发器由两个反相时钟控制的D锁存器构成,实现边沿触发,确保在时钟上升沿复制D到Q。此外,文章还提到了电平敏感与边沿触发的区别,以及寄存器在时序电路中的作用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3938

3938

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?