1 什么是IBERT?

IBERT是Xilinx FPGA中集成的一种比特误码率测试工具,它能够:

-

生成高速PRBS(伪随机二进制序列)测试码型

-

在接收端实时检测比特错误并计算误码率

-

扫描并可视化眼图轮廓

-

自动优化收发器参数

与昂贵的外部误码仪(BERT)不同,IBERT完全集成在FPGA内部,只需一根下载线,就能对高速收发器进行全面诊断。

2 测试原理

IBERT提供了四种回环模式+none模式:

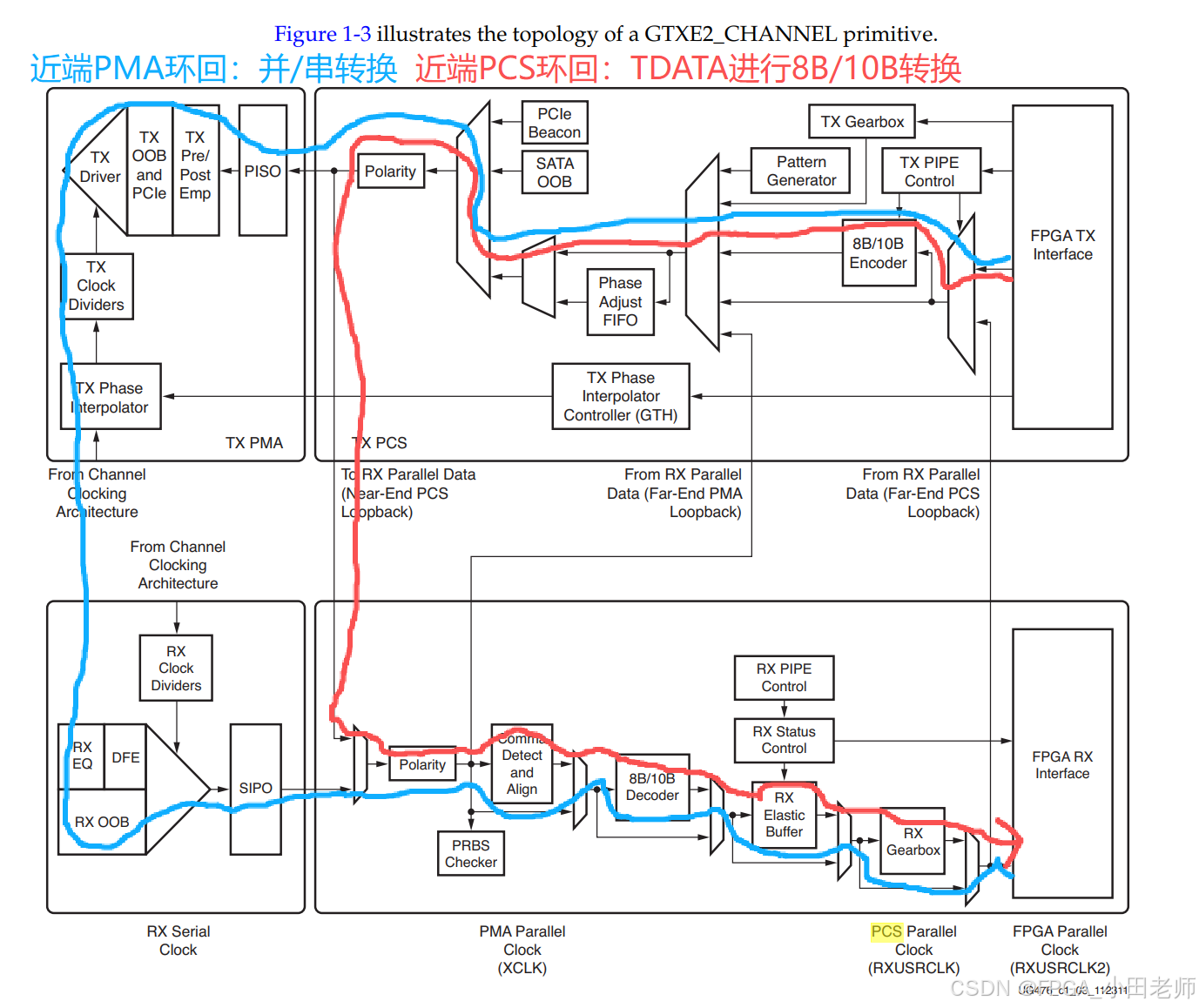

1) 近端PCS回环:如下图红线所示,从Polarity(极性选择)的地方开始回环,从图中可以看出,这里其实只是编解码层的回环,测试编解码是否正常。

2 )近端PMA回环:如下图蓝线所示, 将编码后的数据转化为串行数据,对串行的数据进行回环测试。

上述两种方式都是单板测试使用,或者单个GT口测试使用,当然还有一种模式,单GT口的none模式:

3) 单GT口 none模式:使用光纤将一个GT口的收发相连,形成回路,进行测试,这里会直接测试到硬件走线外部线缆。

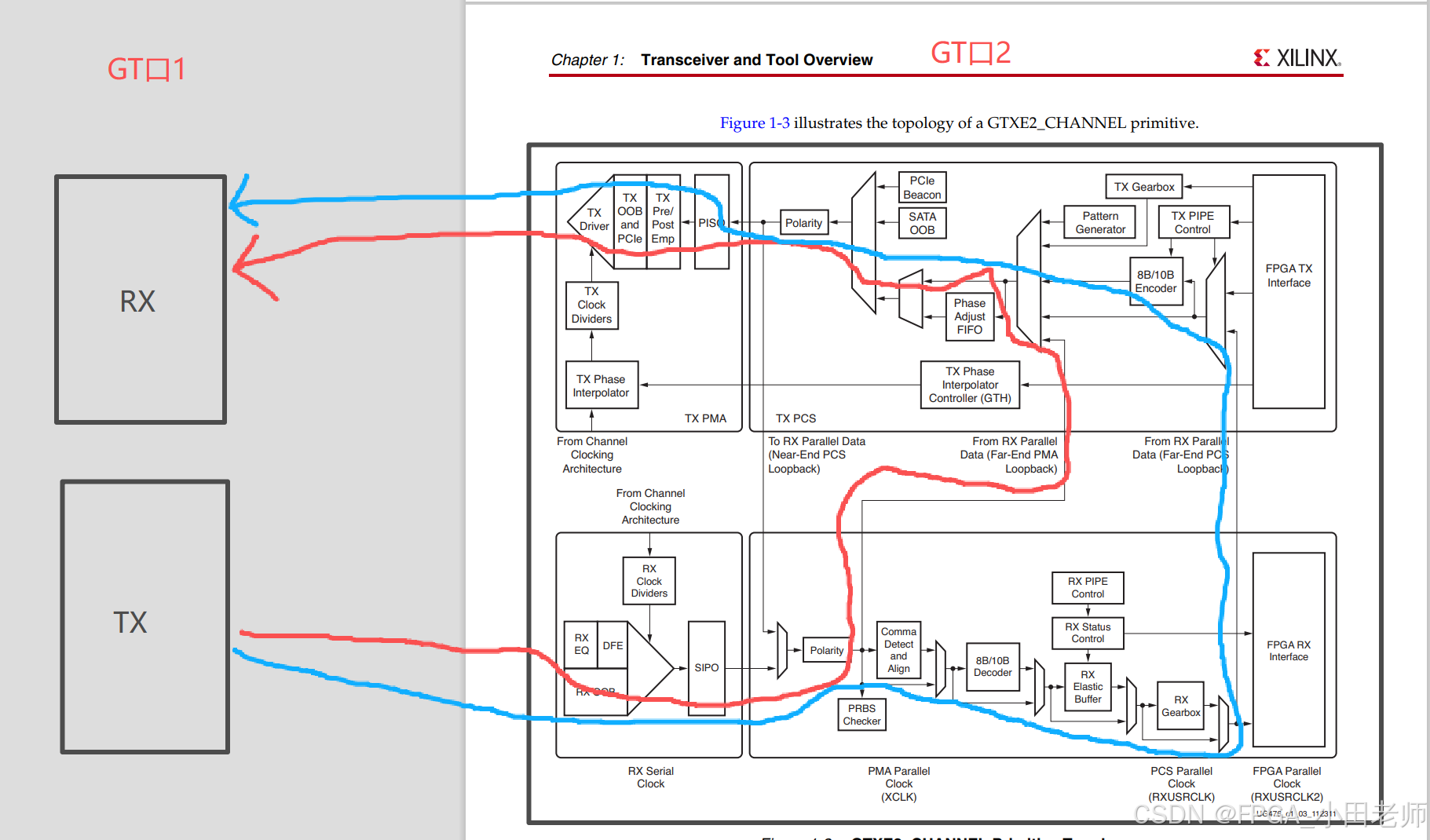

4) 远端PMA回环:远端回环是发生在两个GT口之间的,如下图红线所示:从GT口1(none模式)TX发出数据,到GT口2(Far PMA模式)RX的polarity(极性选择)之后环回给GT口2的TX,之后发出给GT口1的RX,即只将GT口1过来的数据进行串并转换后就进行环回测试。

5) 远端PCS回环:如下图蓝线所示,在串并转换的基础上进行了解码操作之后进行环回。

3 以现有的测试环境说明IBERT如何使用

3.1 ibert配置和测试bit生成

现有的环境是,A板(XCTA100T),B板(XC7K325T),两个板子之间使用Aurora接口进行通讯,我们需要测试各自的GT通道。

以A板为例,说明单板测试

1)新建工程--->ip catelog-->搜索ibert(新建工程的过程这里不再详述,大家应该都清楚)

2)参考需要测试的GT口相关的原理图,和我们的内部配置,配置ibert

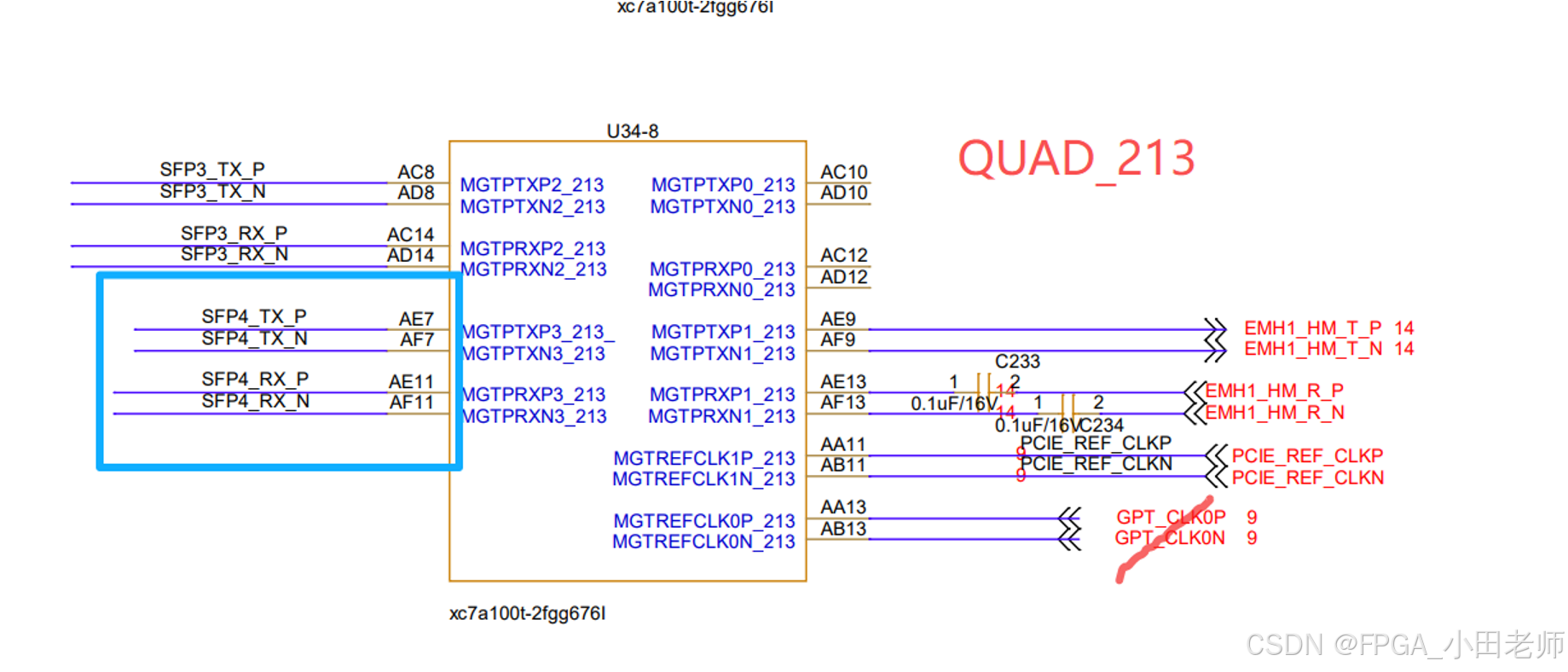

原理图如下:

我们实际使用的是BANK213-GT[3]

GT时钟使用的是GT_REF_CLK1---100MHz 差分

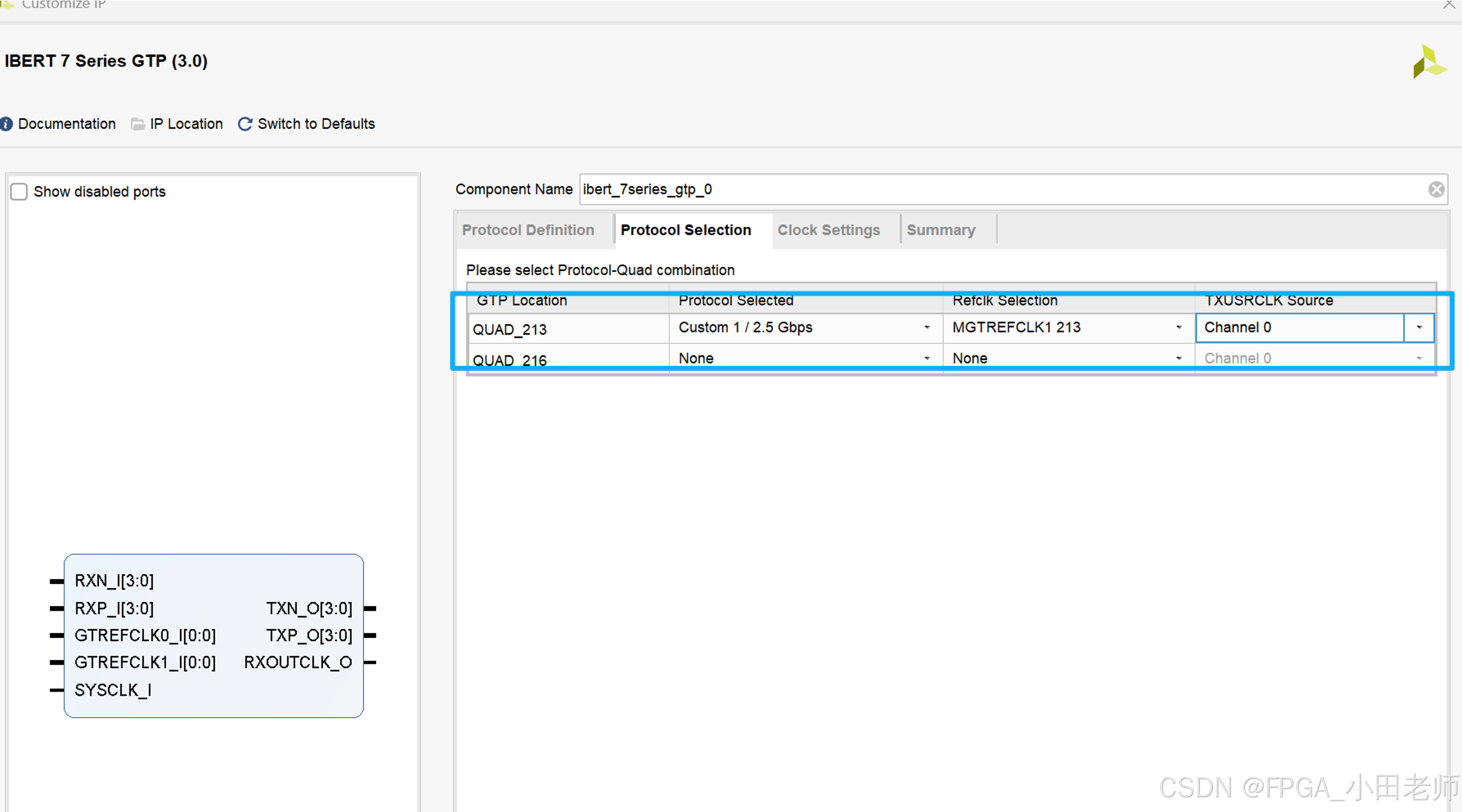

3)ibert配置如下:

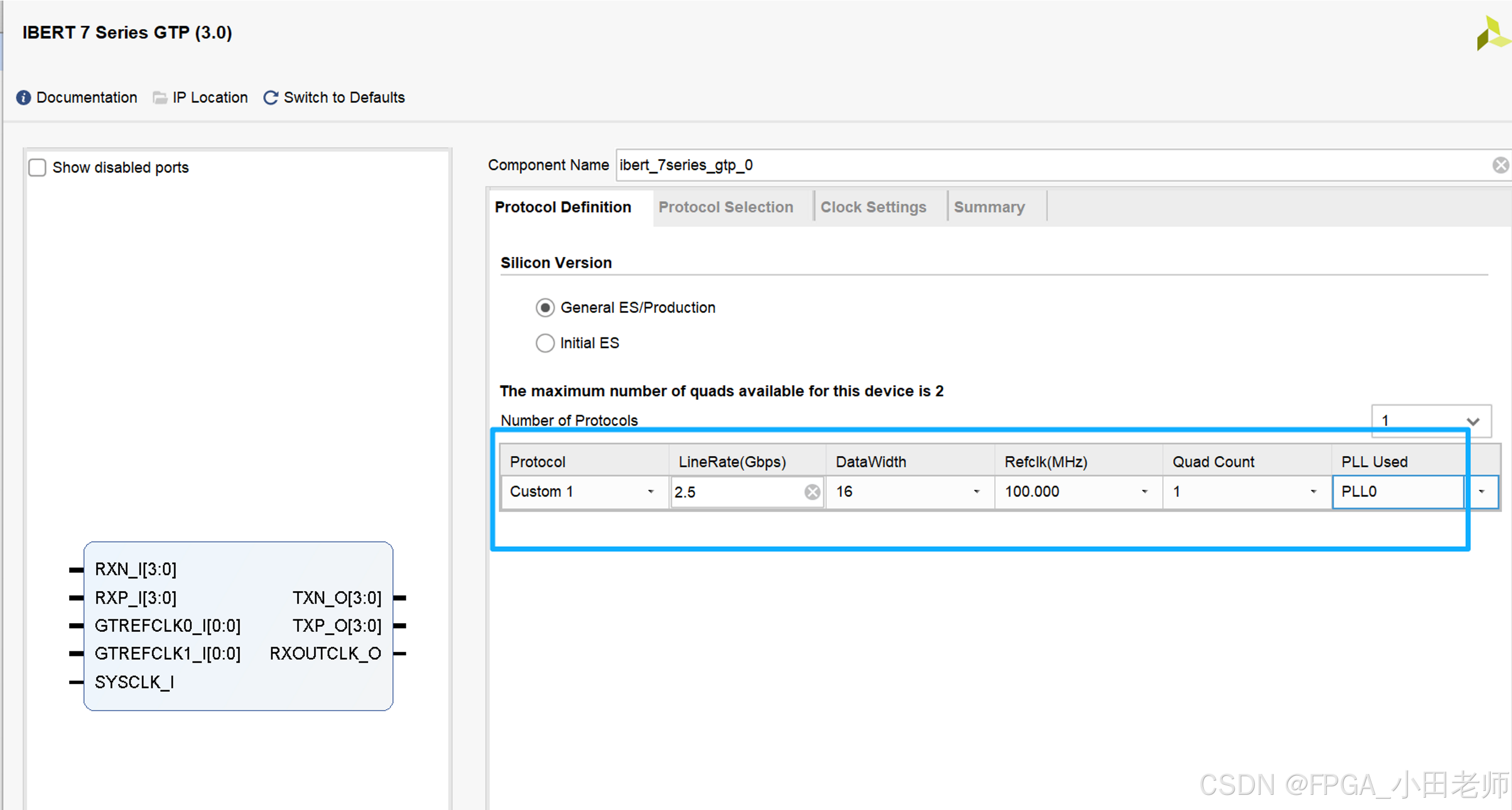

页面一:

选择线速率,我们本次工程中使用的线速率是2.5Gbps,所以测试就按照2.5Gbps进行测试;

参考时钟,原理图中GT_Ref_CLK1,设置100MHz

Quad Count:我们本次ibert只测试一个Quad(1个Quad对应4组GT通道,但是实际中具体测试哪一组GT通道,我们后面也可以自己选择哈,XC7A100T上总共有2个QUAD,我们本次只测试QUAD_213就可以了)

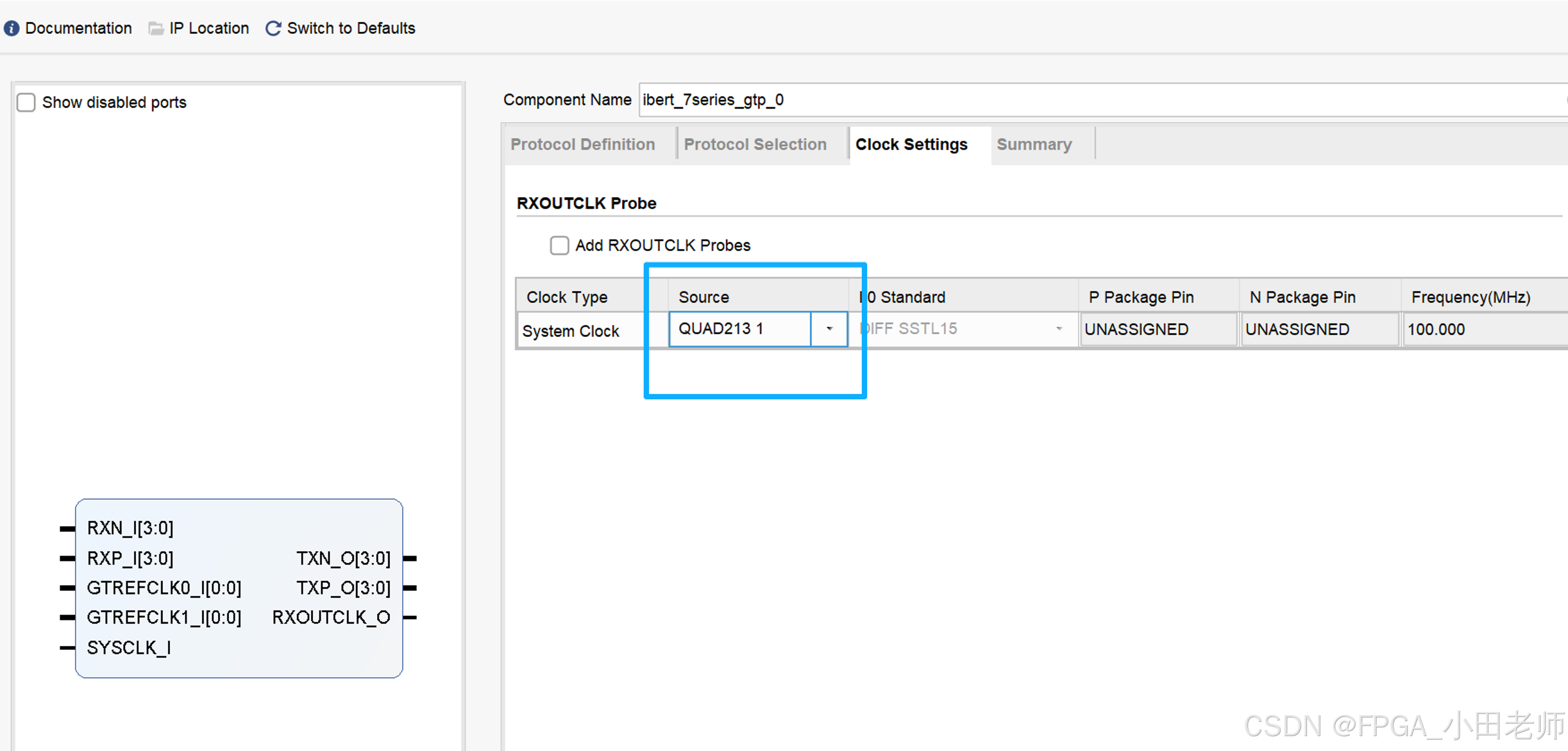

页面二:

选择QUAD:按照原理图,我们本次测试的是QUAD_213(对应BANK_213),参考时钟是GT_REF_CLK1

这里选择系统时钟:要么是外部给的,要么是QUAD 213产生的,为了方便起见,就使用QUAD 213产生就行了。

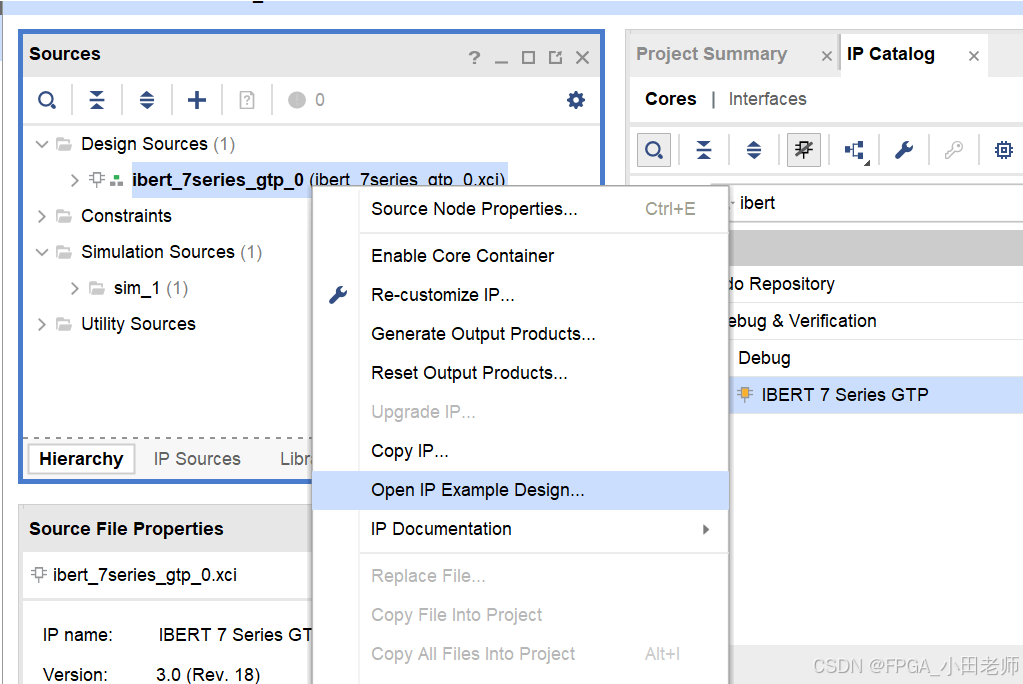

4)测试例程生成

配置好ibert后,等待generate完成,我们打开Open IP Example Design

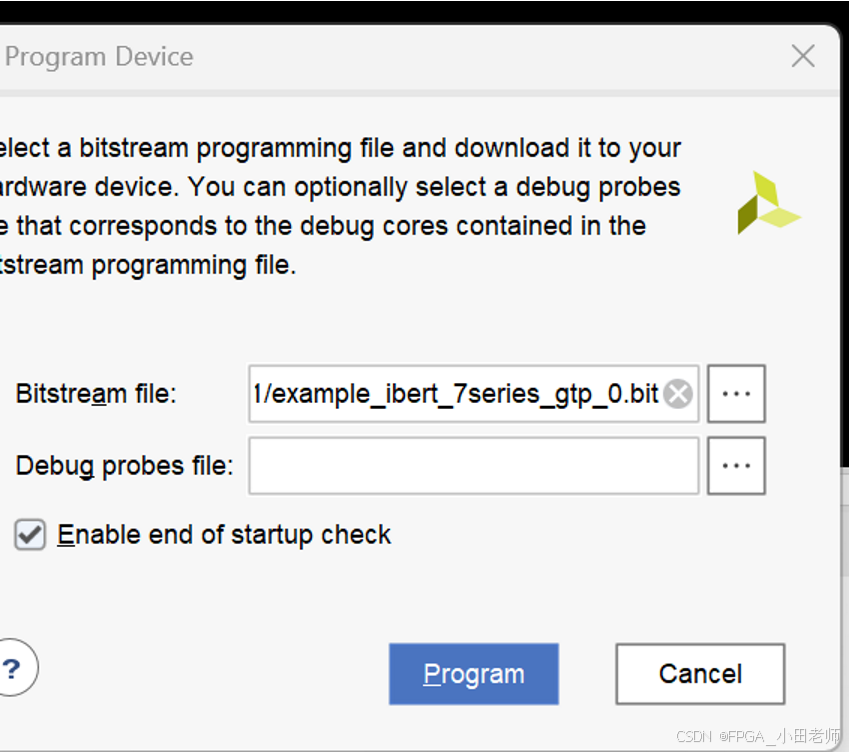

5)直接编译我们打开的example工程,生成bit,下载进板子即可

3.2 单独A板测试(单GT口测试)

3.2.1 测试链路创建

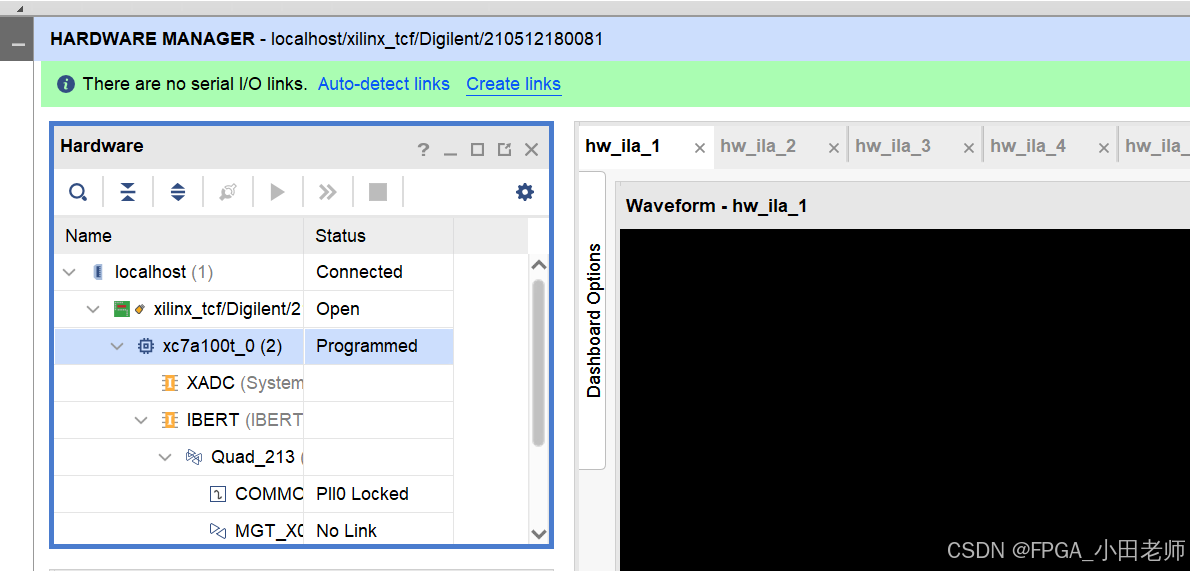

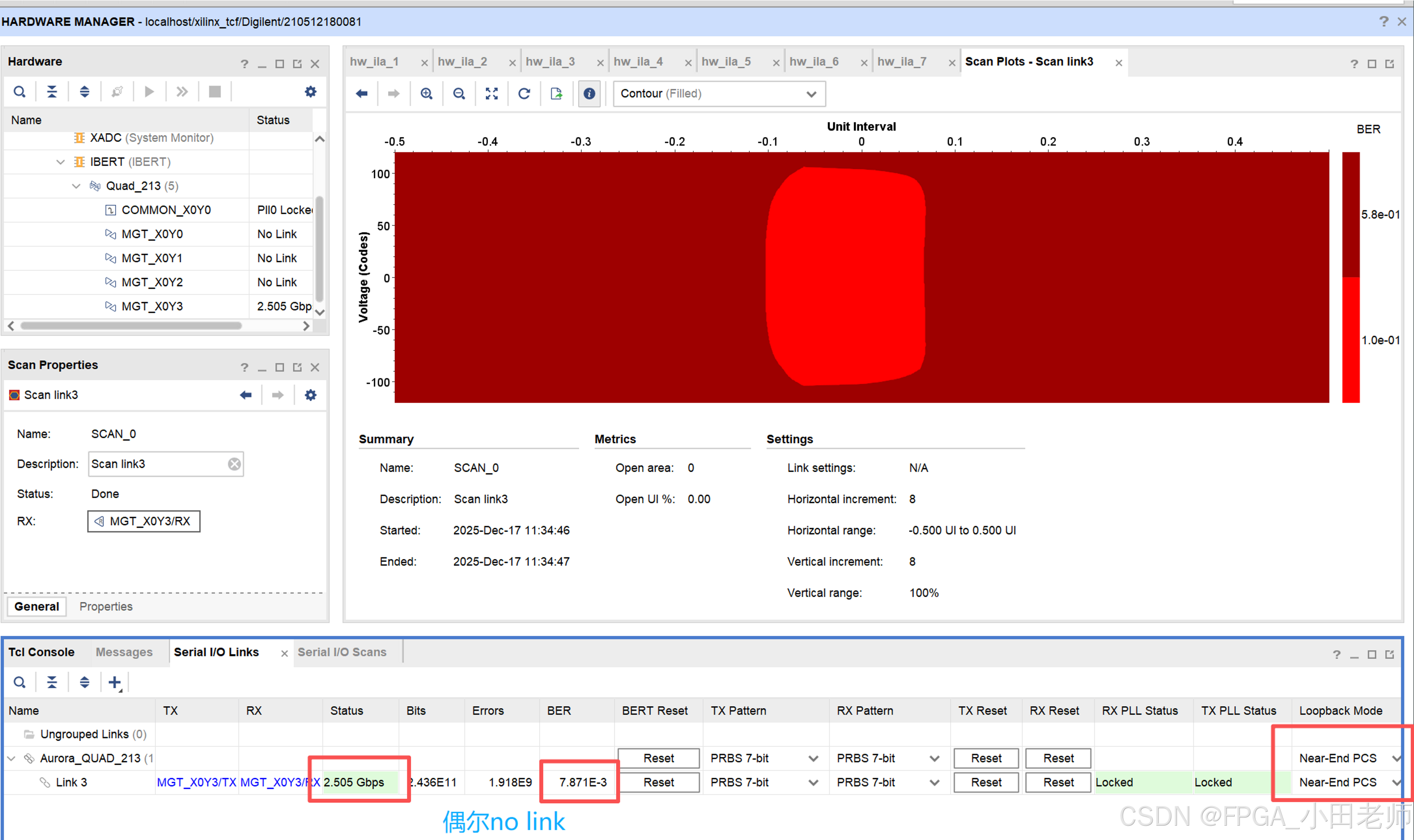

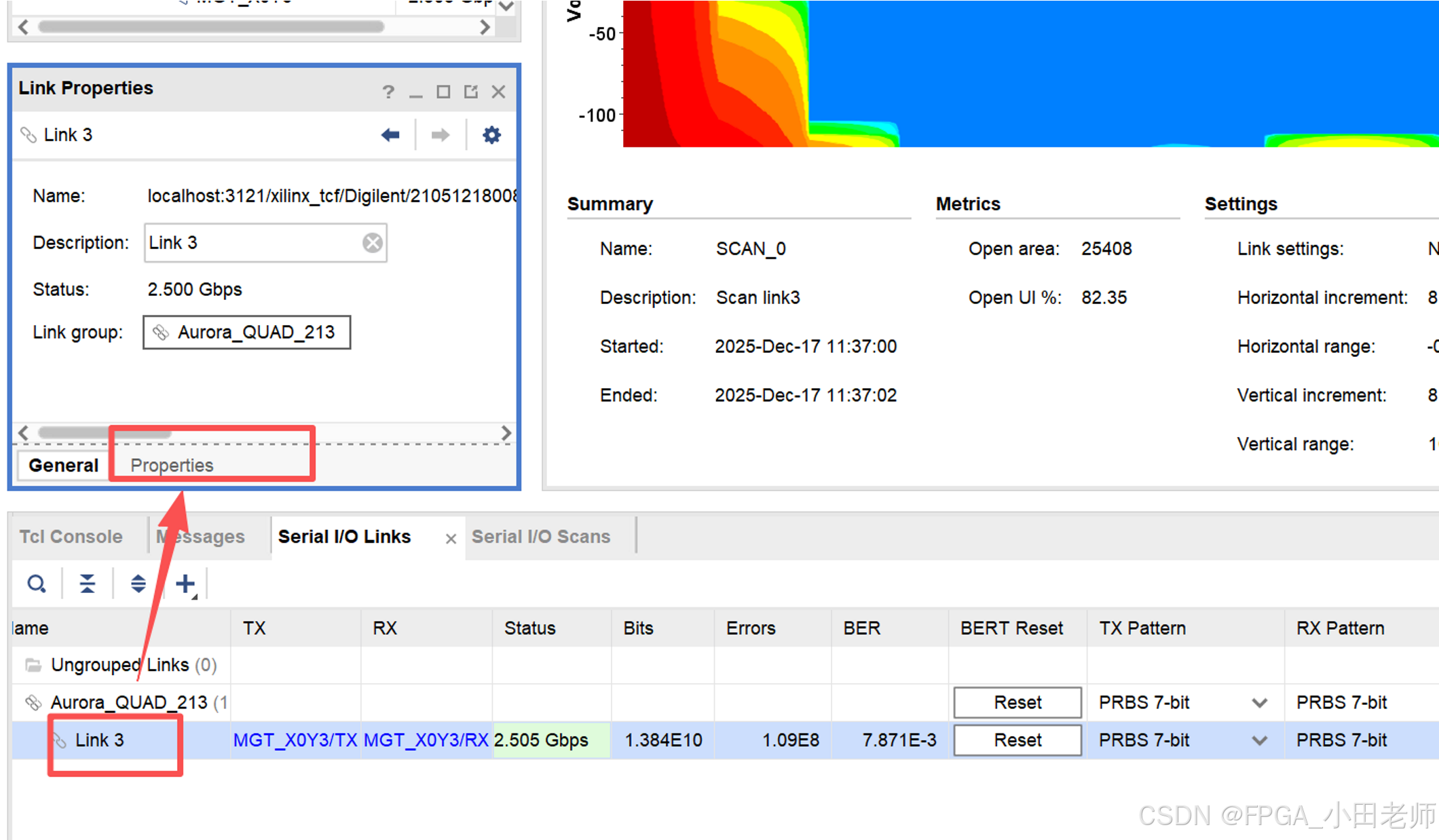

1)bit下载进板子,点击Create links,用来创建一个测试用的GT口。

创建界面打开如下图,将我们需要测试的一组GT通道(TX+RX)选中,点+,将其添加为一个New Links,即一个新的测试链路,我们也可以创建几个测试链路,这些测试链路都放在一个Link Group里面,即链路组里面,点击OK

那我们本次只测试GT通道[3],那我们只创建一个测试链路就可以了。

3.2.2 近端环回测试

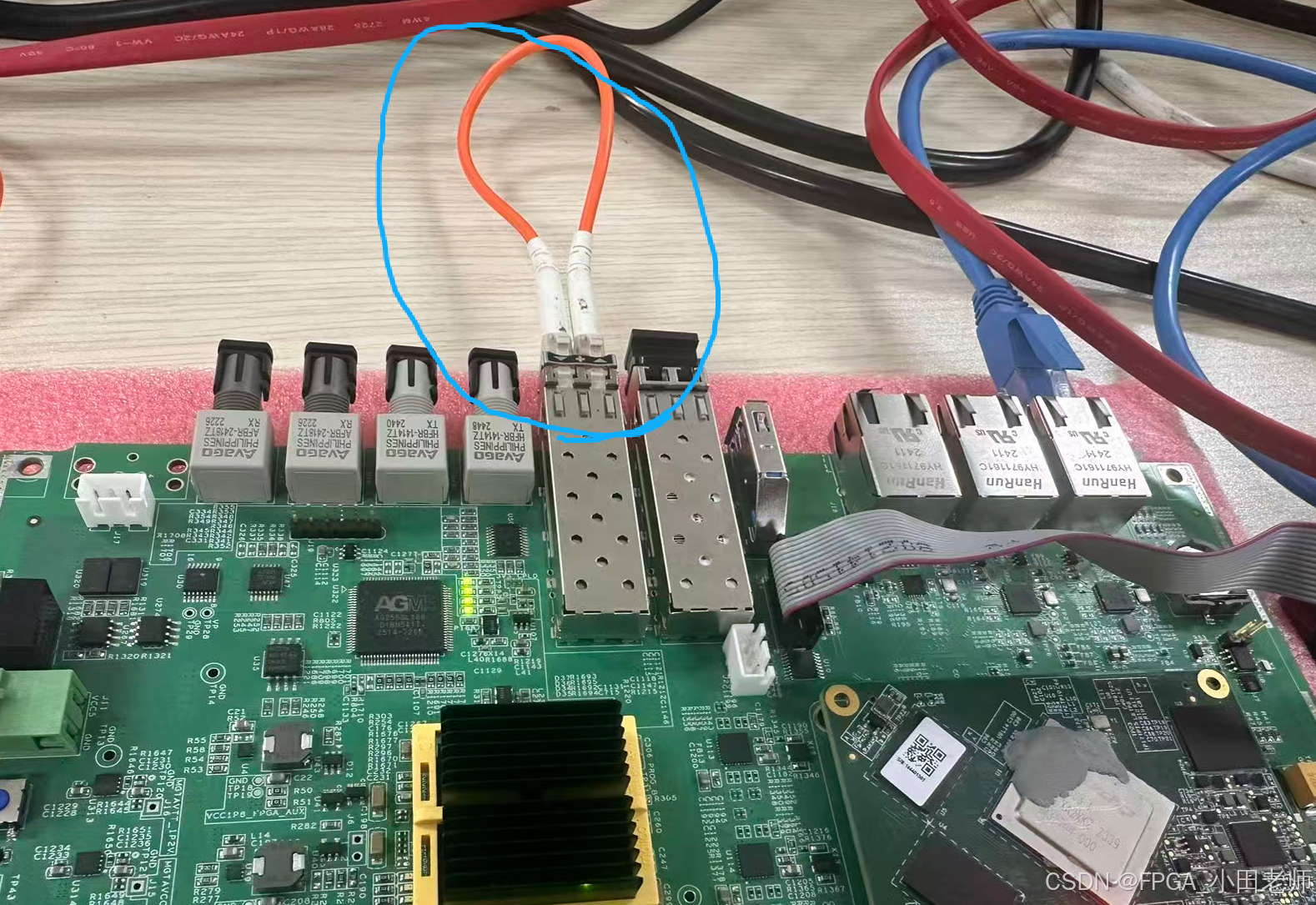

测试硬件环境如下图所示

3.2.2.1 Near-End PMA

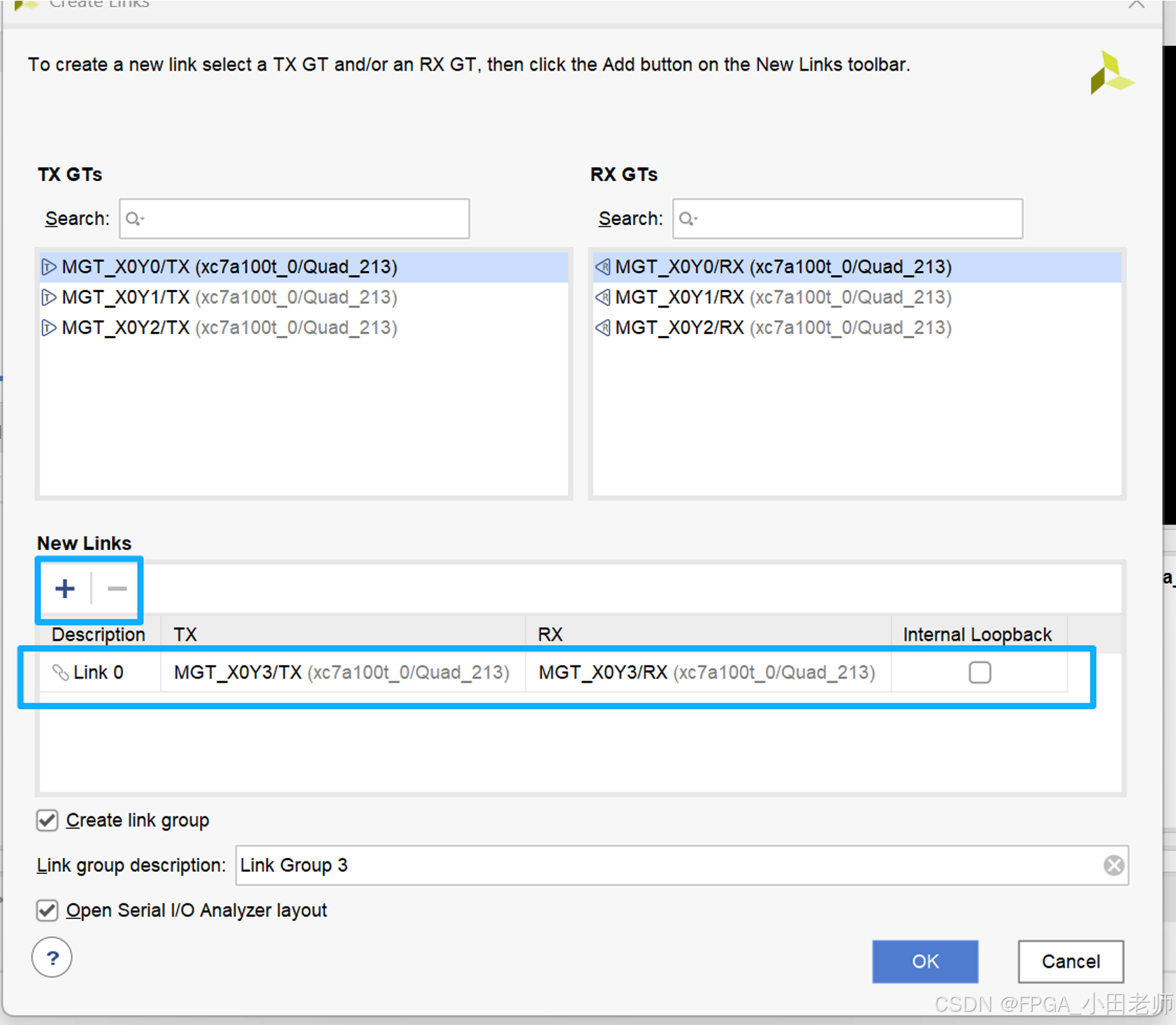

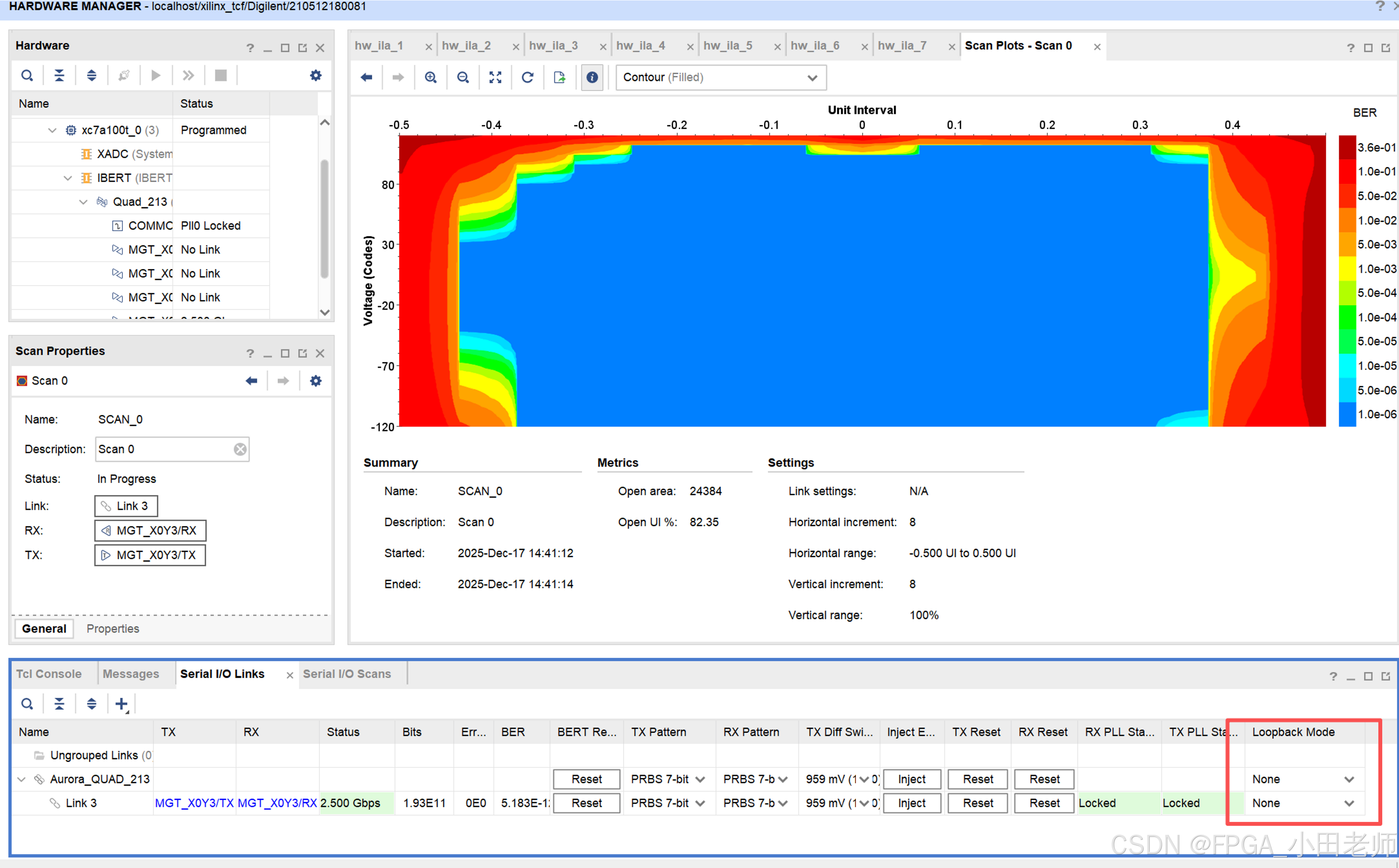

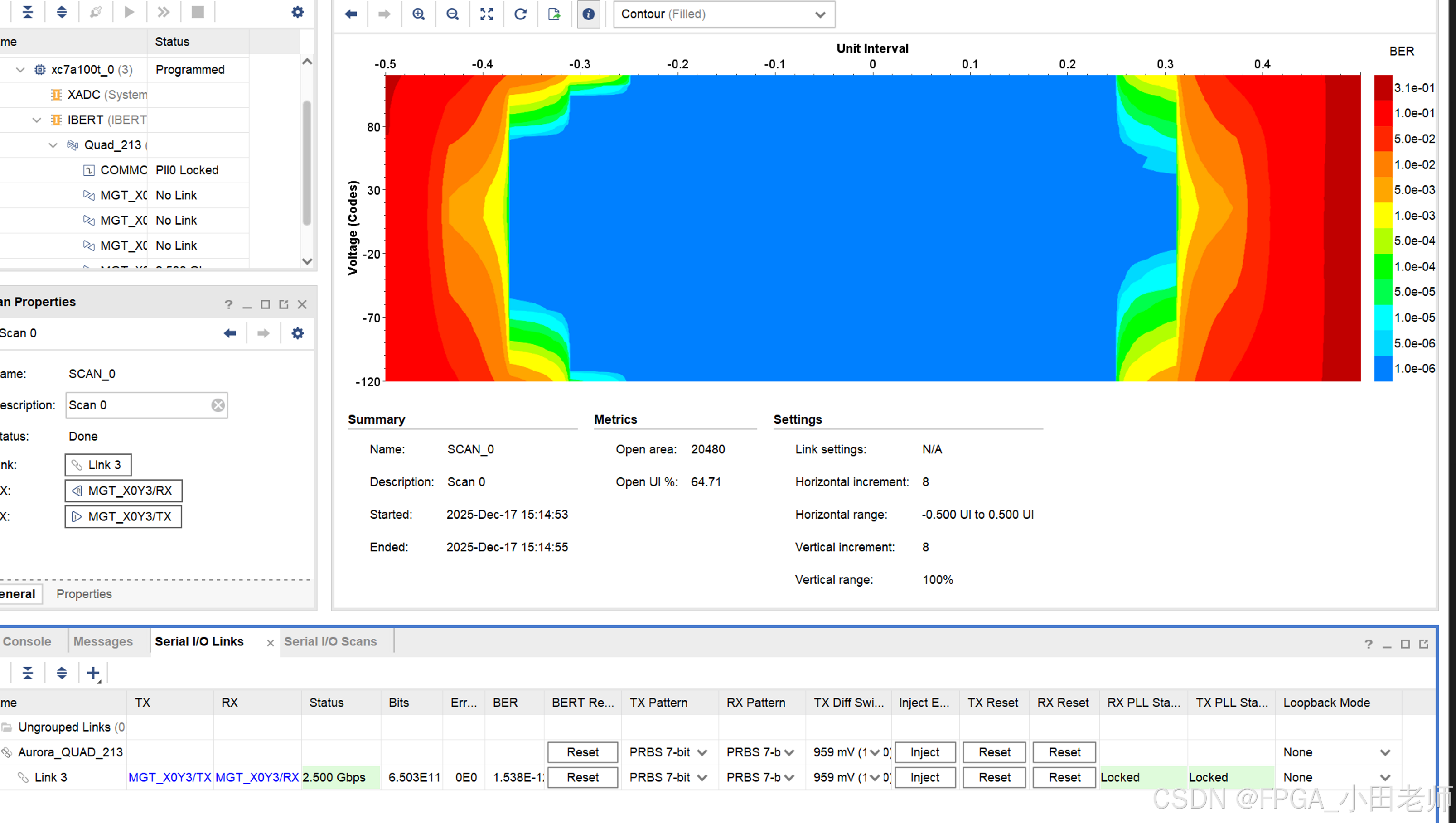

将Lookback Mode设置为 Near-End PMA,根据章节2测试原理部分,近端PMA回环, 将编码后的数据转化为串行数据,对串行的数据进行回环测试,测试结果如下:

可以看出,没有ERRORS,误码率也到10E-12,眼图正常(眼图打开方式,link的地方右键选择Create SCan,就可以看到了)

3.2.2.2 Near-End PCS

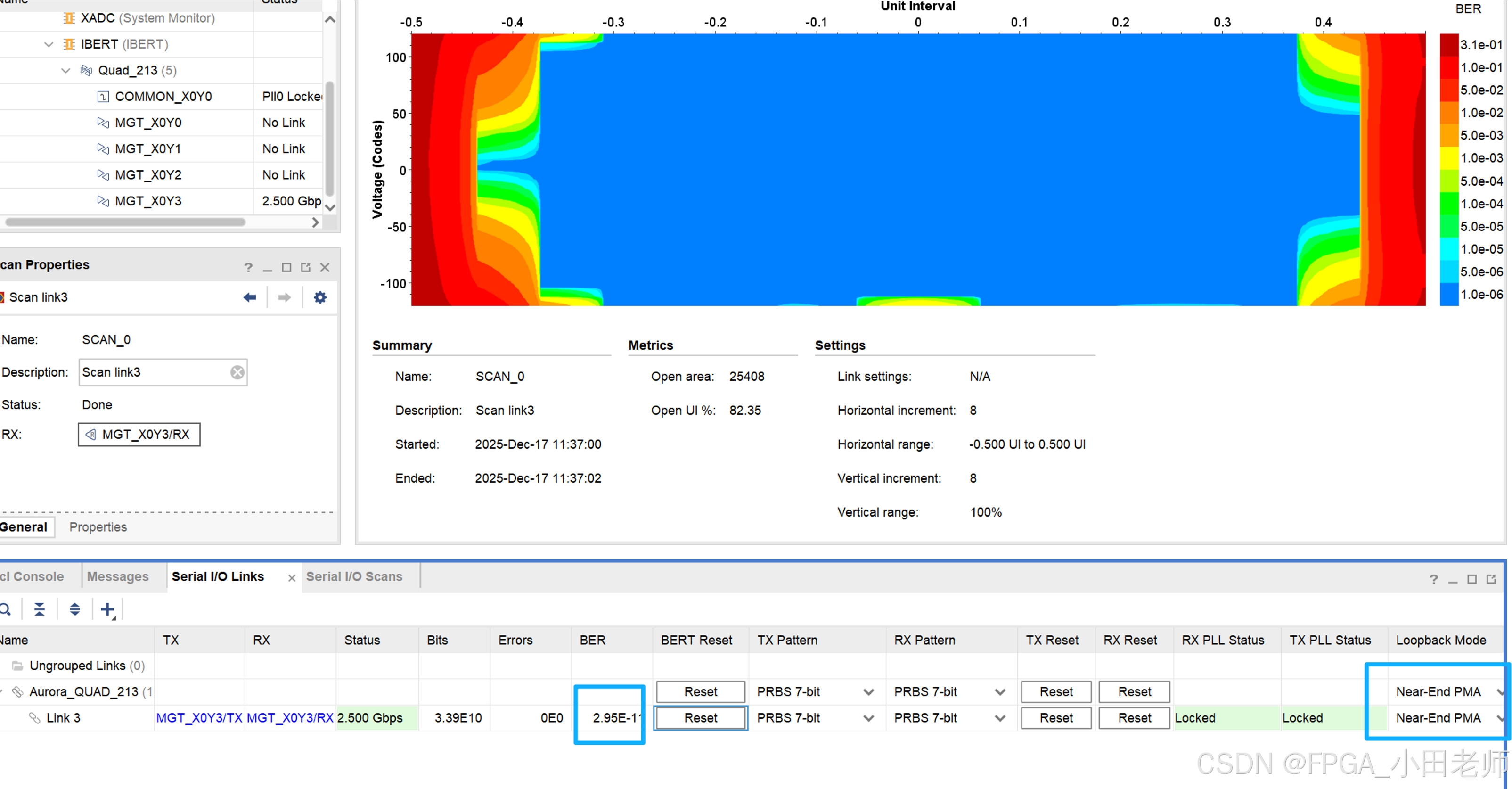

将Lookback Mode设置为 Near-End PCS,根据章节2测试原理部分,从Polarity(极性选择)的地方开始回环,从图中可以看出,这里其实只是编解码层的回环,测试编解码是否正常,测试结果如下:

咦!!!!!!

按说PCS要比PMA测试的范围更小呀,为什么这里PCS测试会出现偶尔no link,且有错误,误码率很高的情况呢,还有眼图,怎么什么都没有?

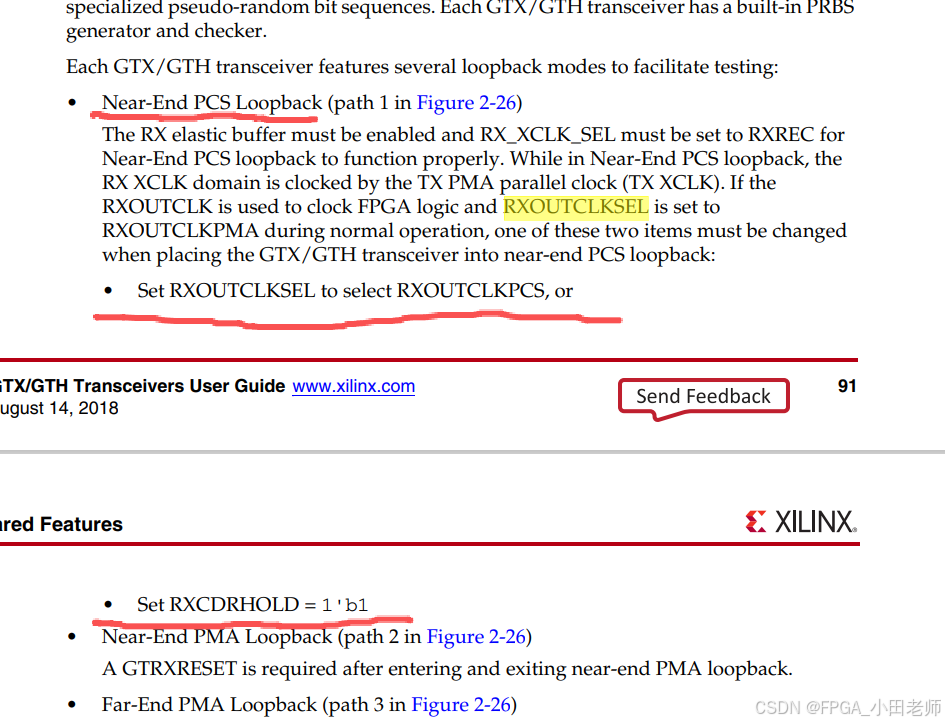

这是因为PCS测试的时候需要参考PCS的时钟,但是我们默认的时钟其实是PMA的,手册里面有提到,在进行近端PCS环回测试的时候,我们需要进行如下设置。

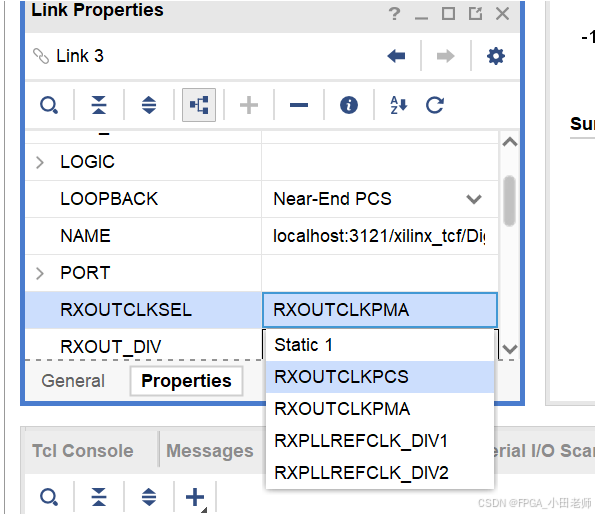

那我们按照手册,更改一下设置,设置的位置如下,点击这个link,在link Properties界面选择Properties。

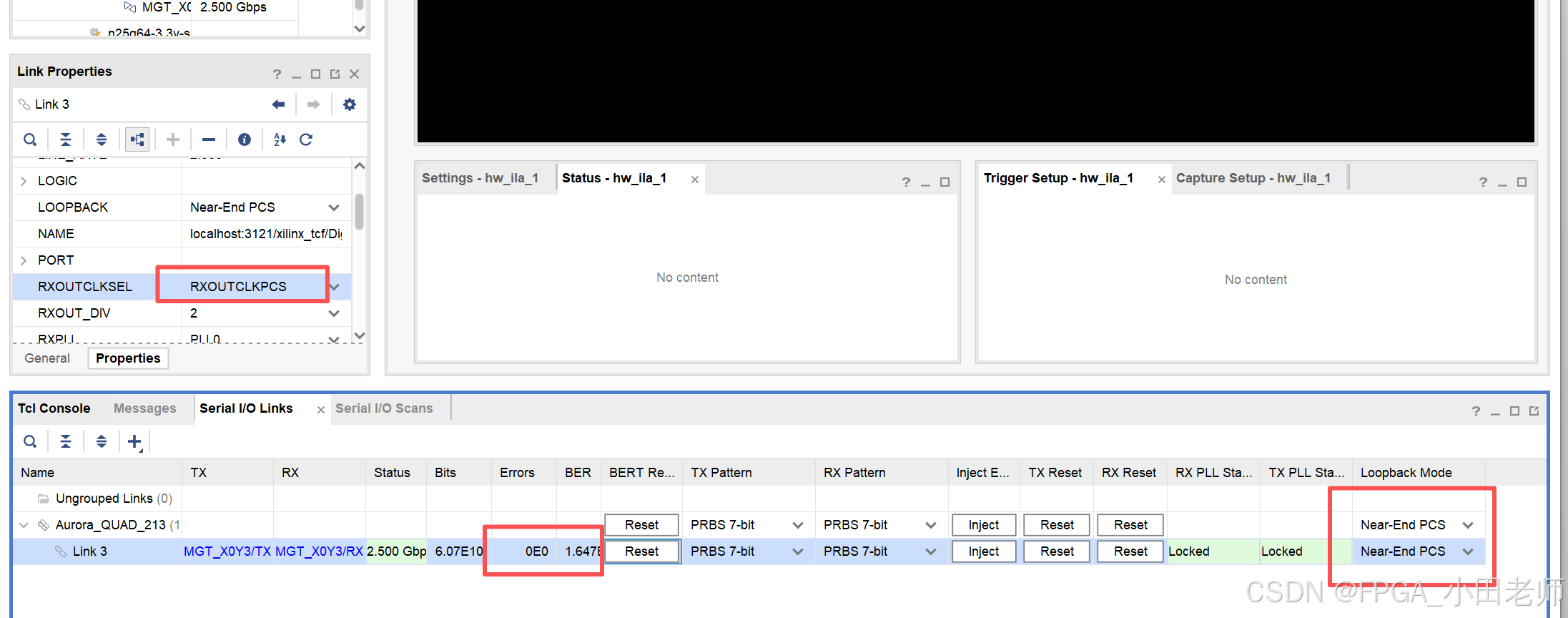

在这里找一下我们的配置项RXOUTCLKSEL,选择PCS时钟就可以了。

我们配置完成之后,点击一下link那一行的Reset,可以看到,Near-end PCS环回测试正常了;

关于眼图--------近端PCS环回是不需要关注眼图的哈,为什么呢?

这里要从眼图的定义开始说明:

眼图(Eye Diagram)是用余辉方式累积叠加显示采集到的串行信号的比特位的结果,叠加后的图形形状看起来和眼睛很像,故名眼图。

那近端PCS环回只到8B10B编解码,就没有串行信号,哪里来的眼图呢,是吧,只有有串行信号的时候才有眼图哈。

3.2.3 单GT口(单A板)外环测试(测试到硬件走线和线缆)

测试环境如下:

我们使用一根光纤将待测GT口的TX和RX接起来,然后在vivado中将loopback设置为none模式,即不进行内部环回,信号就会走我们外部的线路进行环回,测试结果如下图所示。

3.2.4 远端环回测试

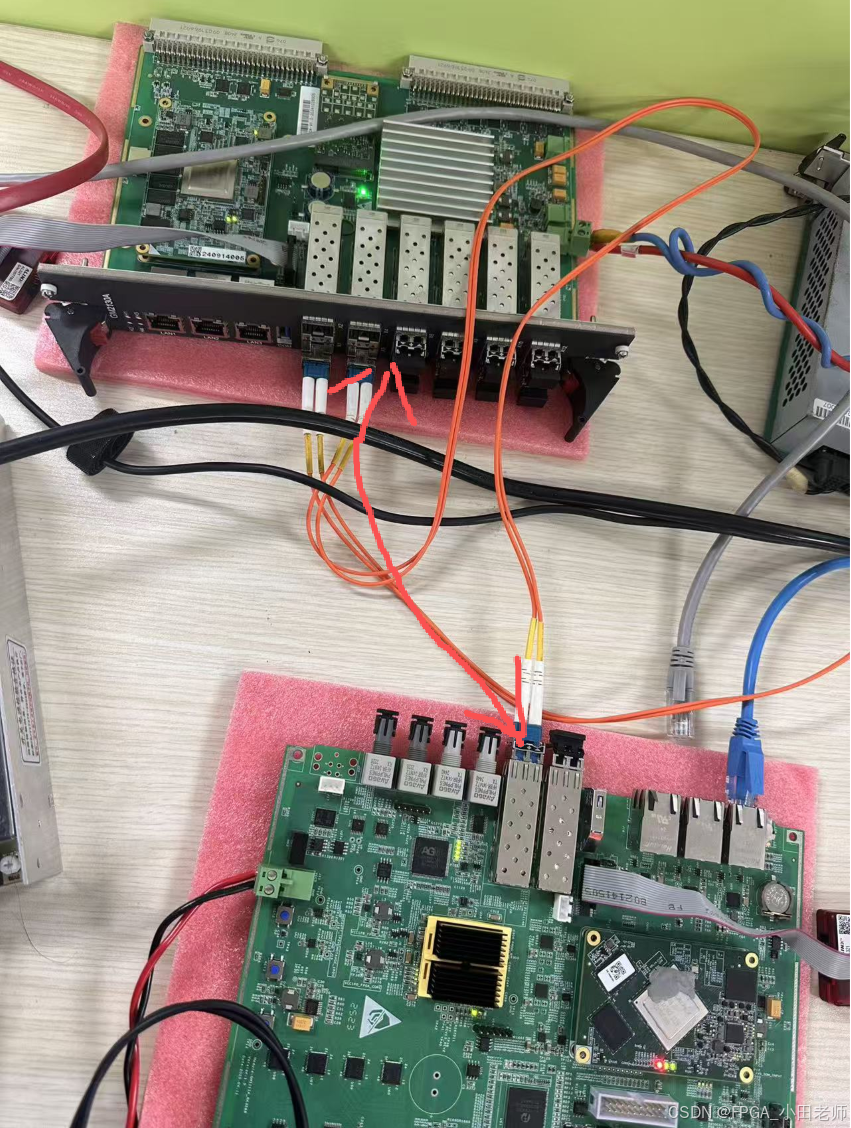

远端环回需要两个GT口之间(也可以两个板子之间,我们本次测试就是A板和B板之间),测试的硬件连接如下图,使用光纤将A板和B板连接起来。

分别在A板和B板中下载各自的ibert测试文件,对,你没有看错,需要两边都有FPGA,可以两边都下载ibert文件哈。

3.2.4.1 Far-end PMA

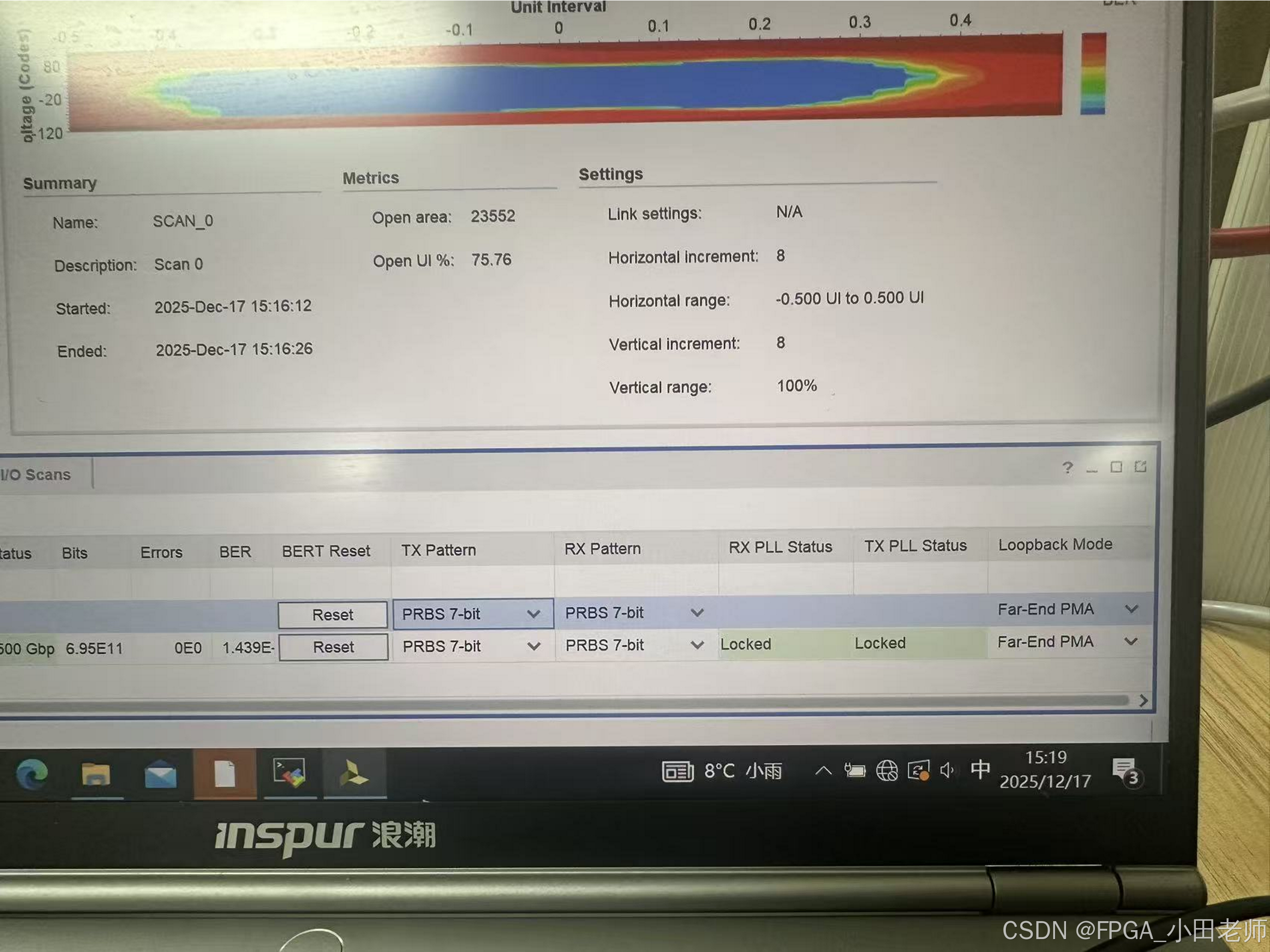

远端PMA环回,即从GT口1(none模式)TX发出数据,到GT口2(Far PMA模式)RX的polarity(极性选择)之后环回给GT口2的TX,之后发出给GT口1的RX,即只将GT口1过来的数据进行串并转换后就进行环回测试

故我们将A板设置为none模式,B板设置为 Far-end PMA模式,这样A板发出的数据,到B板之后完成串并转换又会环回到A板。

测试结果如下所示,我们在A板(设置NONE的那端)进行信号环回观测。

3.2.4.2 Far-End PCS

远端PCS环回,即A板发出的数据,到B板之后,经过串并转换8B10解码然后环回到B板的8B10B编码,并串转化最后通过A板的RX端口再送回A板,我们在A板进行信号观测即可,这里就不贴图了,感兴趣的大家自己试试。

4 结语

在数字设计日益复杂、速率不断攀升的今天,IBERT已经从"锦上添花"的工具变成了"雪中送炭"的必需品。它不仅仅是测试工具,更是工程师理解高速信号行为的窗口。

掌握IBERT,意味着你能够:

-

在数小时内完成以往需要数天的调试工作

-

用数据说话,而不是凭经验猜测

-

在设计阶段就发现并解决潜在的信号完整性问题

-

为客户提供经过充分验证的可靠产品

高速数字设计如同在钢丝上跳舞,而IBERT就是你手中的平衡杆。它不会让你不摔跤,但能让你在摔跤前知道哪里有风。

1469

1469

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?