1 概述

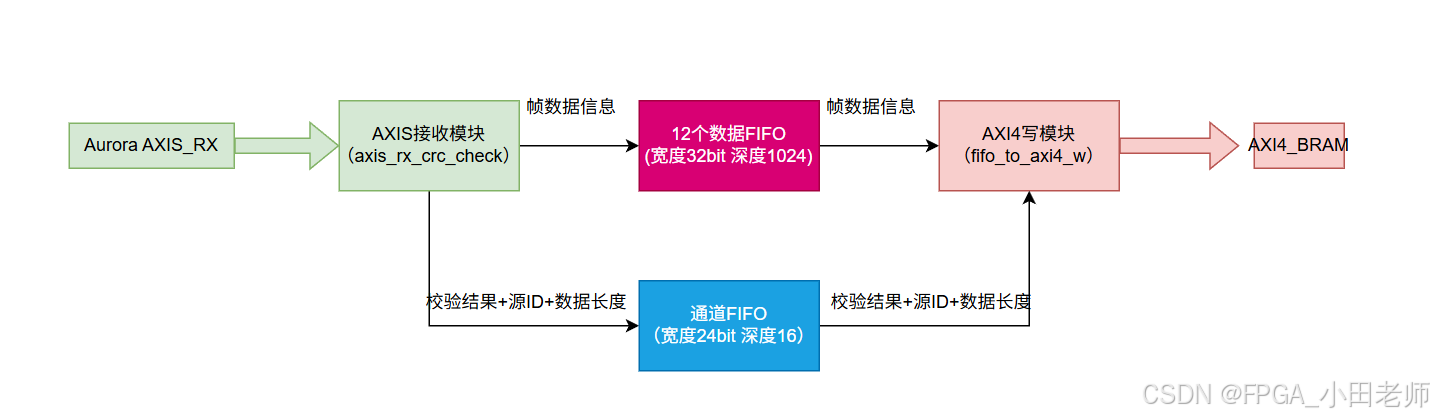

在FPGA通信系统中,上行数据处理是一个关键环节。本文详细介绍一个高效的上行数据处理模块设计,该设计能够同时处理多个通道的AXI-Stream数据流,进行CRC校验,并按顺序通过AXI4接口写入BRAM。整个系统已在硬件上验证通过,表现稳定可靠。

2 系统架构

3 模块详解

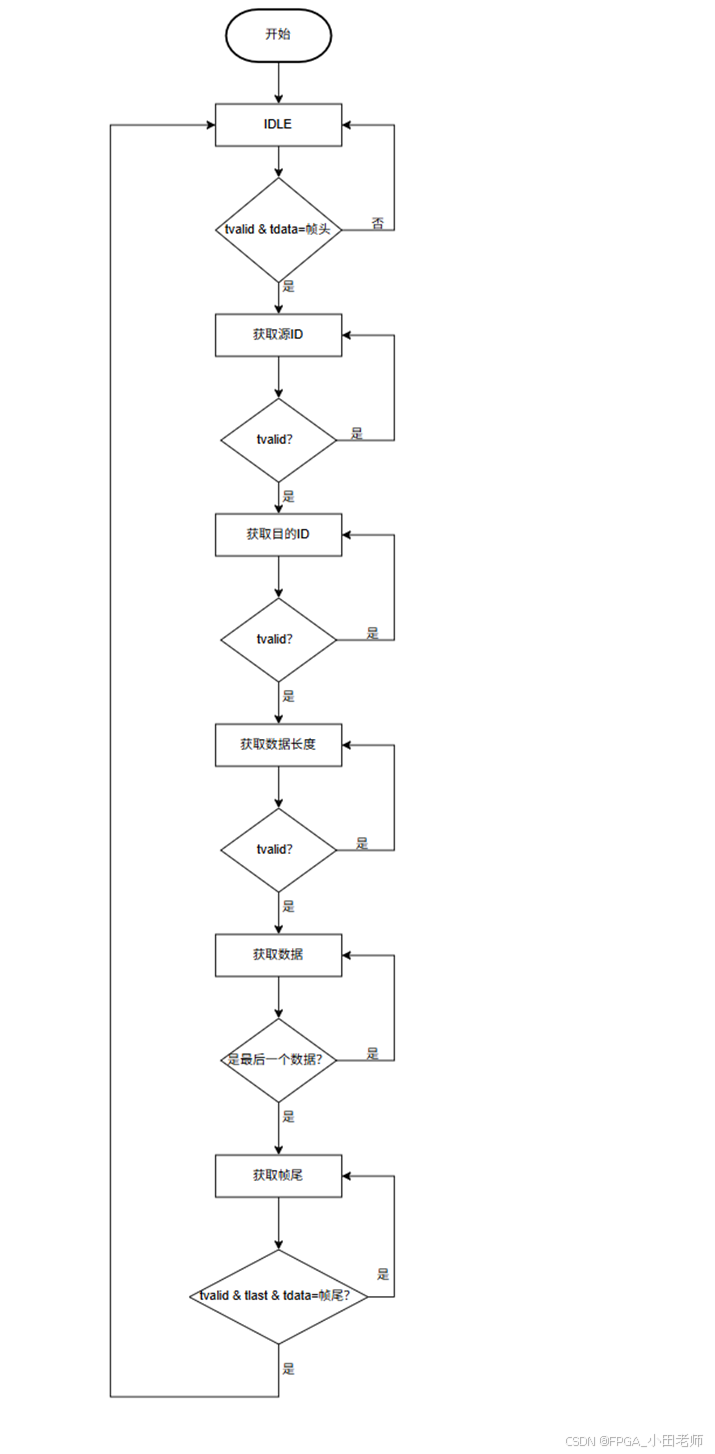

3.1 AXIS接收数据模块 (axis_rx_crc_check)

接收数据模块,主要接收来自于Aurora的数据,将其按照通道缓存在接收FIFO中,并将通道号和校验结果缓存在通道FIFO中,状态机处理流程如下:

1)当获取源ID的时候,将源ID缓存在src_id中

订阅专栏 解锁全文

订阅专栏 解锁全文

1511

1511

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?