相关文档参考:

- Xilinx Aurora 8B/10B IP核(2):时钟架构&线速率&Lane配置--使用与选择详解_aurora 配置-优快云博客

- Xilinx Aurora 8B/10B IP核(3):Shared Logic的选择

- Xilinx Aurora 8B/10B IP核(4):GT配置--逻辑Lanes vs 物理Quad

- Xilinx Aurora 8B/10B IP核(5):gt_reset、reset、power_down与loopback信号深度解析-优快云博客

- Xilinx Aurora 8B/10B IP核(5):例化接口说明(多核共享时钟)

1 引言

在高速数据采集、数据中心互连、雷达信号处理及高性能计算等领域, FPGA之间或FPGA与其它设备之间的高速、可靠数据通信至关重要。AMD(原Xilinx)的 Aurora 8B/10B LogiCORE IP 正是为此而生的一个轻量级、可扩展的链路层协议解决方案。它不仅是一个IP核,更是一套完整的通信框架,本文将深入其架构、特性、配置流程与实际应用。

2 核心架构与工作原理

Aurora 8B/10B IP核是一个分层设计的协议引擎,其核心模块包括:

-

通道逻辑:每个GTX/GTH/GTP收发器对应一个通道逻辑实例,负责单个通道的初始化、8B/10B编解码及控制字符处理。

-

全局逻辑:管理多通道的绑定与验证,生成协议所需的空闲字符,并监控所有通道的错误状态。

-

用户接口:提供标准化的AXI4-Stream接口,分为发送与接收两部分,无缝对接用户应用逻辑。

-

收发器封装:将AMD复杂的收发器原语进行封装,提供简化的控制与状态接口。

数据流从用户应用的AXI4-Stream接口进入,经过协议封装(添加帧起始/结束符)、扰码(可选)、CRC计算(可选)后,被分配到各通道进行8B/10B编码,最后通过高速串行收发器发出。接收端则执行相反的过程。

3 IP核配置

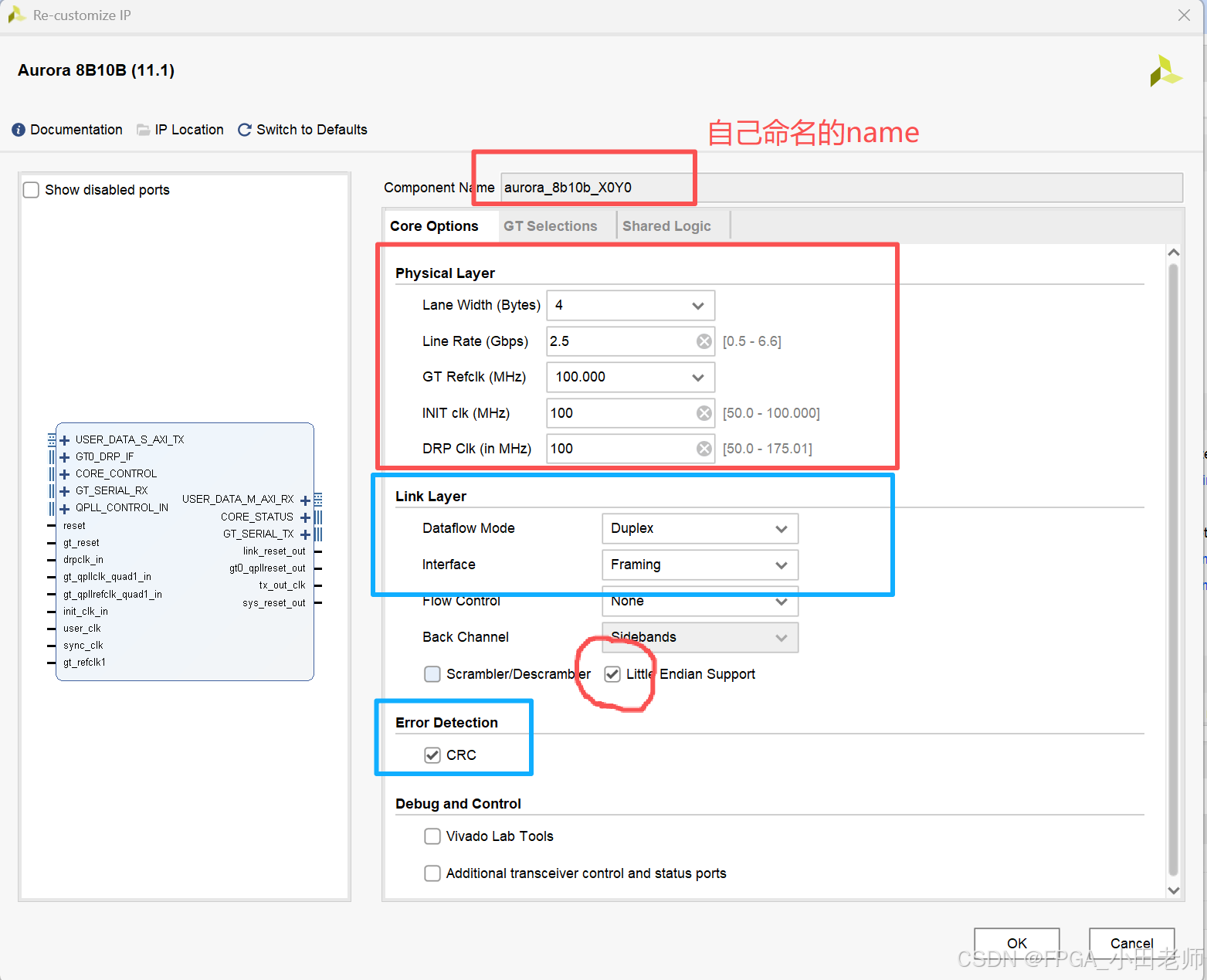

3.1 第一页:Core Options

3.1.1 第一部分:时钟,线速率的配置:

GT Refclk:

功能:驱动GT收发器锁相环,产生高速串行时钟

来源:外部晶振/时钟芯片,通过专用时钟管脚输入

质量要求:低抖动(<1ps RMS)、高稳定性

决定性关系:线速率 = GT_Ref_Clk × 整数倍频系数

// 举例

GT_Ref_Clk频率 = 100 MHz

目标线速率 = 2.5 Gbps

倍频系数 = 2.5 Gbps / 100 MHz = 25 // 25是个整数INIT clk:

功能:控制GT收发器初始化和复位序列

来源:通常与参考时钟同源或FPGA逻辑时钟

频率范围:50-150 MHz

关键特性:只在初始化和重配置时使用,正常数据传输时不活跃

DRP clk(基本不用):

功能:动态重配置接口时钟,用于实时调整GT参数

来源:FPGA逻辑时钟

频率:与用户逻辑兼容(通常50-250 MHz)

User clk:

根据上述,我们可以衍生出User clk,即用户时钟

User_Clk频率 = 有效数据速率 / 总数据位宽

有效数据速率 = 线速率 × (8/10)

线速率 = 2.5 Gbps

// 单Lane配置计算:

有效数据速率 = 2.5 Gbps × 0.8 = 2.0 Gbps

单Lane数据位宽 = 32位(4字节)

User_Clk频率 = 2.0 Gbps / 32 bit = 62.5 MHz

// 4-Lane配置计算:

总有效数据速率 = 2.0 Gbps × 4 = 8.0 Gbps

总数据位宽 = 32位 × 4 = 128位

User_Clk频率 = 8.0 Gbps / 128 bit = 62.5 MHz详细的参数介绍可参考:Xilinx Aurora 8B/10B IP核(2):时钟架构&线速率&Lane配置--使用与选择详解_aurora 配置-优快云博客

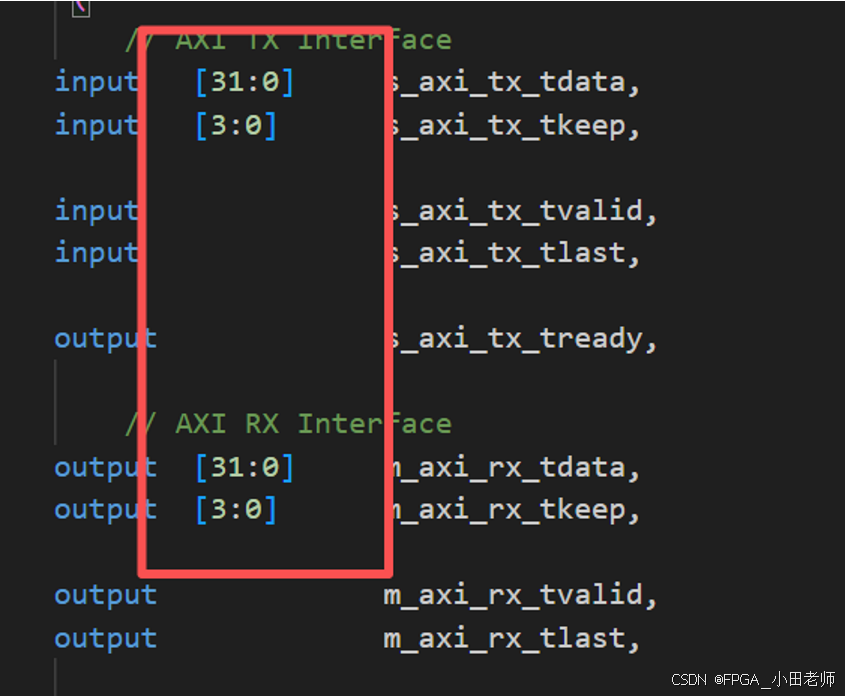

3.1.2 第二部分:用户接口选择

可选接口为Framing和Streaming

Framing:完整的AXI4-Stream接口,支持带帧头帧尾的任意长度数据包传输。适用于网络封包、DMA传输等场景。

Streaming:简化的AXI4-Stream接口,数据如流水般持续传输,无帧概念。结构更简单,资源占用更少。

说这么多,其实就是Framing有tlast信号,streaming只有tvalid和tdata,所以一个是数据流的概念,一个是帧的概念。

3.1.3 第三部分:大小端选择

勾选小端模式,对外的stream数据就是[31:0],如果不勾选,数据就是[0:31],为了跟FPGA适配,一般都是需要勾选的。

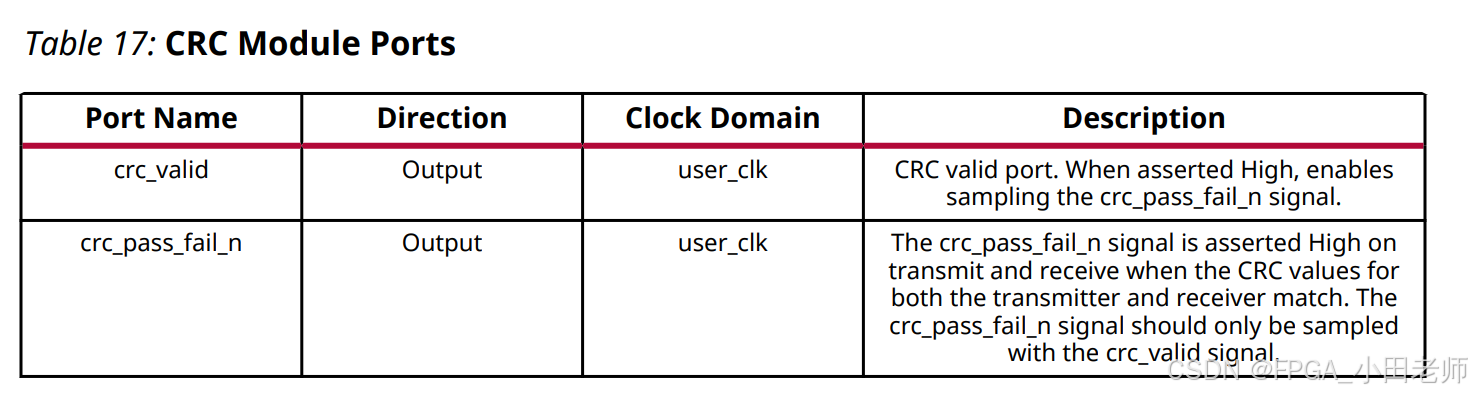

3.1.4 第四部分:CRC校验

主要是如下两个信号,当crc_valid有效时,crc_pass_fail_n为高,说明校验通过。

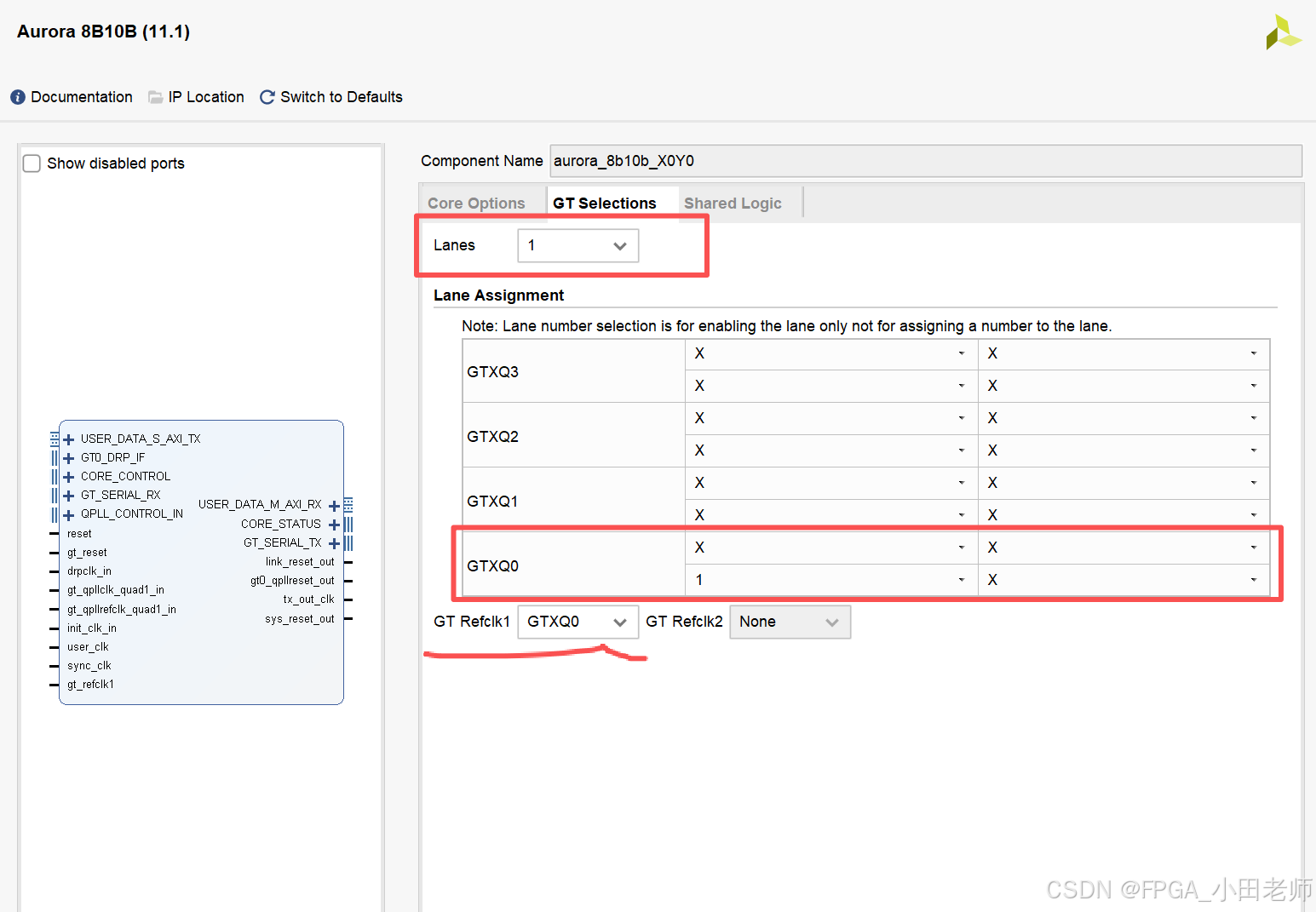

3.2 第二页:GT Selections

Lanes:即逻辑通道,我们设置为1,即选择了1个GT通道,对应一组TXP TXN RXP RXN

GTXQ0~GTXQ3:对应的是物理的QUAD,每个QUAD对应4个逻辑通道。

具体的QUAD和LANE的使用与选择,请参考:Xilinx Aurora 8B/10B IP核(4):GT配置--逻辑Lanes vs 物理Quad_fpga gt quad 编号-优快云博客

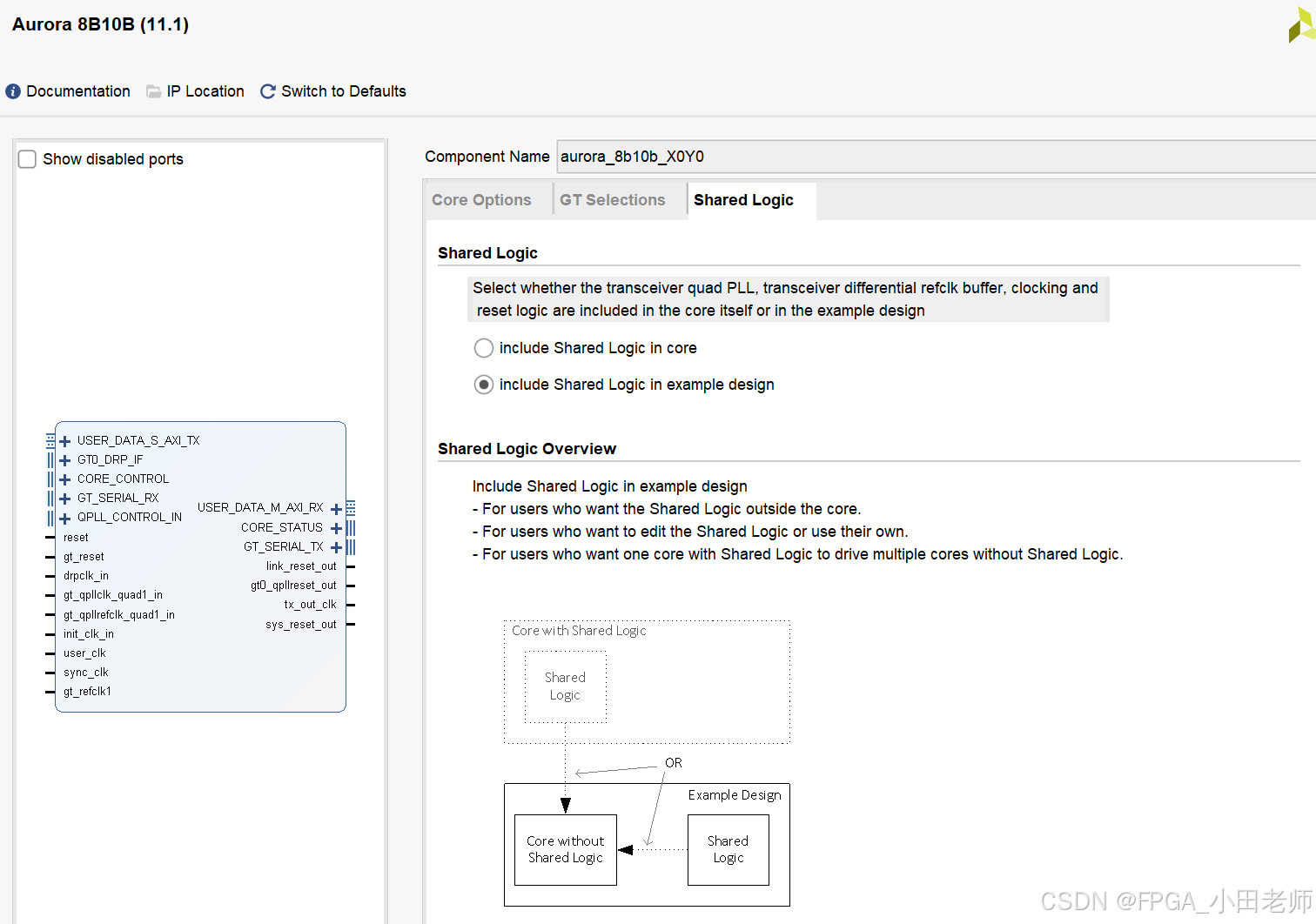

3.3 第三页:Shared Logic

共享逻辑的选择:

可以选择将其包含在core里面

也可以将其例化在example design中

具体的选择方式,请参考:Xilinx Aurora 8B/10B IP核(3):Shared Logic的选择_aurora pll lock-优快云博客

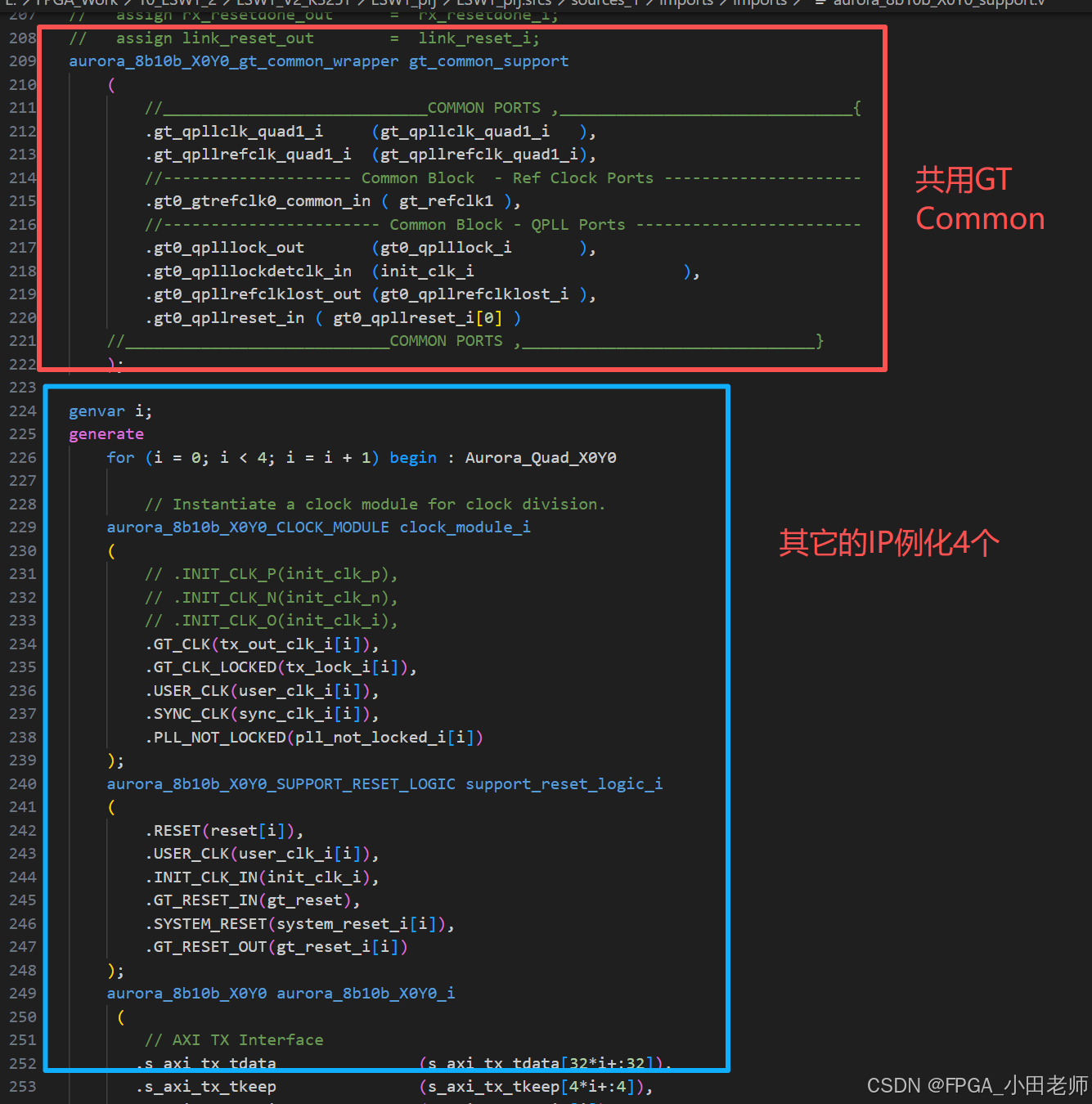

4 应用实例

根据我们本次的场景:我们需要使用一个QUAD例化4个Aurora ip核,故share logic需要选择example design的方式,我们参考下面的文章,熟悉一下例化之后的Aurora ip的一些对外接口

Xilinx Aurora 8B/10B IP核(5):例化接口说明(多核共享时钟)_aurora ip配置界面无法选择相邻quads时钟-优快云博客

Xilinx Aurora 8B/10B IP核(5):gt_reset、reset、power_down与loopback信号深度解析-优快云博客

然后根据此,我们将example design的相关文件导入工程中,进行修改。

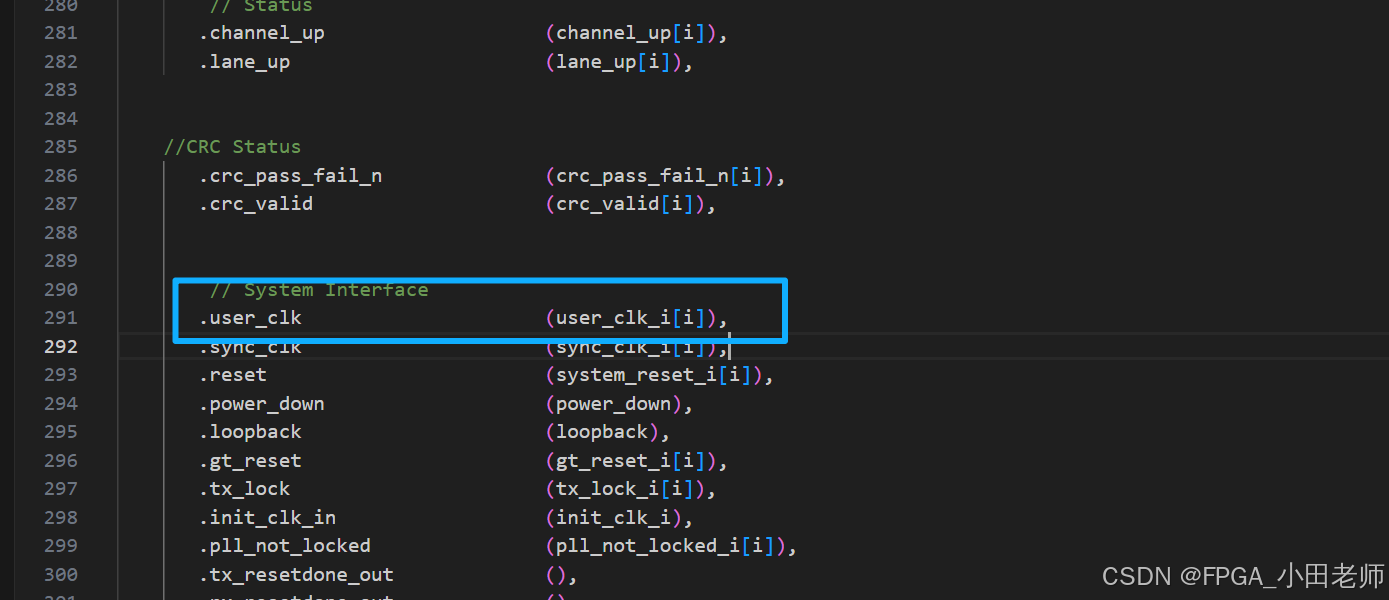

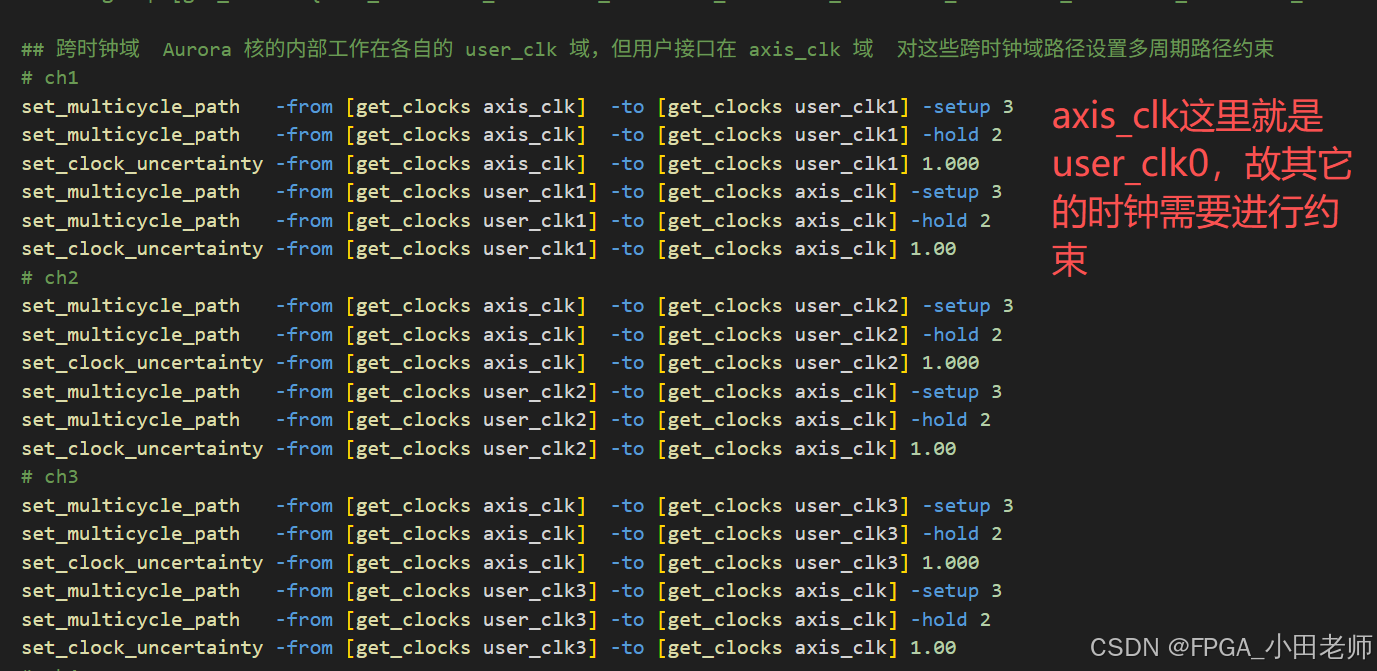

这里我们可以看到,User clk也是多个的,但是正常来说,我们都使用同一个user clk作为4路AXIS的参考时钟即可,我们一般使用user clk[0]作为所有AXIS总线的参考时钟。

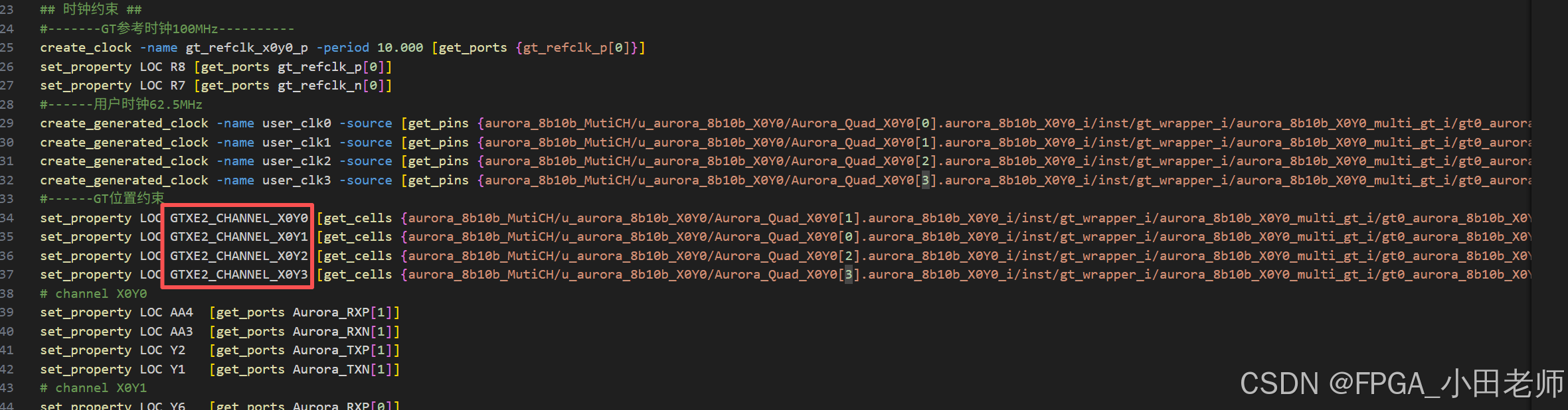

那因为其它路的AXIS原本的同步时钟并不是user_clk0,故需要进行如下的约束。

除上述的约束之外,Aurora在使用的时候还需要进行GT位置的约束,这个直接决定了FPGA上的通达0~3与实际GT通道0~3的对应关系。

5 总结

Aurora 8B/10B IP核是AMD FPGA平台上构建高速串行通信系统的成熟解决方案。通过深入理解其协议特性、时钟复位架构、数据接口机制和配置选项,工程师可以高效设计出稳定可靠的高速数据链路。

核心价值:

-

灵活性:支持从简单点到点连接到复杂多通道绑定的各种应用场景

-

可靠性:内置完整的错误检测、时钟补偿和链路恢复机制

-

易用性:标准AXI4-Stream接口、Vivado工具链深度集成、丰富调试支持

-

高效性:在提供高性能的同时保持较低的逻辑资源占用

无论是用于芯片间互联、背板通信还是板卡间数据汇聚,Aurora 8B/10B IP核都提供了一个经过充分验证的基础架构,让工程师能够专注于应用逻辑开发,而非通信底层实现。随着系统对带宽需求的不断增长,掌握这一核心技术将成为FPGA开发者的重要竞争优势

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?