X态主要是没有赋初值造成的,目前遇到的几种原因总结如下:

1、时钟异常

2、复位信号异常

3、时钟、复位、输入都正常,但是输出为X态:

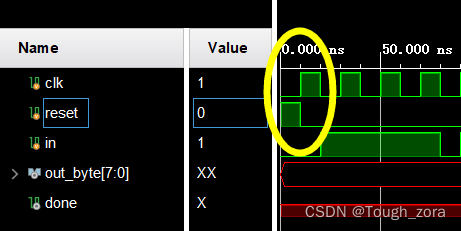

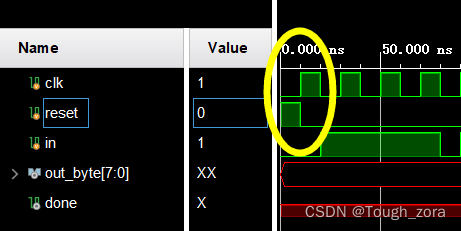

我写的tb有问题,复位有效时间太短,复位有效时,时钟没有产生上升沿,

所以输出没有成功赋初值, 如下所示:

本文总结了导致数字电路输出为X态的常见原因,包括时钟异常、复位信号异常以及测试平台(TB)设计不当。特别是当复位有效时间过短,时钟未在复位期间产生上升沿时,输出无法正确赋初值,从而出现X态。了解这些因素有助于优化数字电路设计和测试过程。

本文总结了导致数字电路输出为X态的常见原因,包括时钟异常、复位信号异常以及测试平台(TB)设计不当。特别是当复位有效时间过短,时钟未在复位期间产生上升沿时,输出无法正确赋初值,从而出现X态。了解这些因素有助于优化数字电路设计和测试过程。

X态主要是没有赋初值造成的,目前遇到的几种原因总结如下:

1、时钟异常

2、复位信号异常

3、时钟、复位、输入都正常,但是输出为X态:

我写的tb有问题,复位有效时间太短,复位有效时,时钟没有产生上升沿,

所以输出没有成功赋初值, 如下所示:

2421

2421

4194

4194

1万+

1万+

1万+

1万+

740

740

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?