X态Verilog行为

在RTL电路仿真中X态表示高低电平不确定的不定态,前仿产生x态的原因:

- 四态逻辑的初始值为x态,且在复位时没有将其复位掉。

- 数组取值时index越界。

…

在verilog中规定了一系列x态与其他值(0、1、x、z)的逻辑运算结果,通常X具有较高的优先级,因此一旦出现了X态,如果没有做好逻辑保护的话,以X态信号作为输入信号的逻辑就会继续运算出x态,从而导致X态在整个电路中扩散。

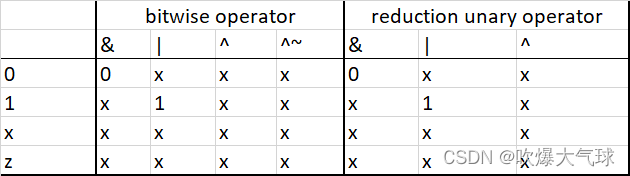

X态与0/1/x/z的运算结果如下:

这只是基本的,其他逻辑:

reg sel;

reg [1:0] a,b,d;

reg [1:0] out1, out2, out3, out4, out5;

``````cpp

always@(*) begin

if(sel)

out1 = a;

else

out1 = b;

end

always@(*) begin

out2 = (sel) ? a : b ;

end

always@(*) begin

case(sel)

1'b0: out3 = a;

1'b1: out3 = b;

endcase

end

always@(*) begin

case(sel)

1'b0: out4 = a;

1'b1: out4 = b;

default: out4 = 2'b00;

endcase

end

always@(posedge clk_x)begin

out5 <= c;

end

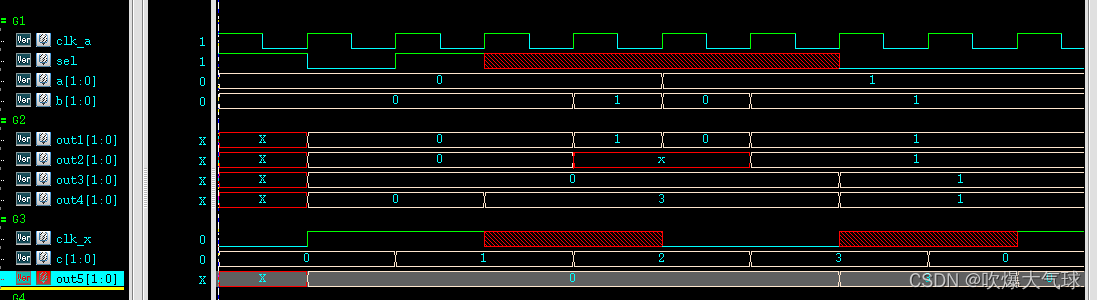

可以看到Verilog behavior中:

- if(sel) a else b 逻辑: 如果sel为x态,选择的都是else 分支

- out = (sel)? a:b 逻辑:如果sel为x态,a,b 值不一致是会产生x态。

- case逻辑没有default: 如果sel为x态,则相当于没有选中任何逻辑,out 保持不变

- case逻辑带有default:如果sel为x态,选择default

- 最后的打拍逻辑,如果时钟sel为x态,在0->x, 1->x, x->0, x->1中,0->x,x->1, 会被视为上升沿

==以上的行为实际上不符合实际的电路行为, 其中一些逻辑中不一定会导致x态的传播,前仿不一定能发现这个问题,可能导致bug遗漏到后仿阶段。==因此EDA前仿工具中引入了XPROP工具, 当然Formal 工具也有XPROP的RAK可以发现这个问题。

两种X态模型

在介绍XPROP工具前,首先引入了2种X态模型,X-Optimism和X-Pessimism。

- X-Optimism : 乐观模型,模拟在RTL仿真中,如果逻辑的输出结果未知则会被解析为X值。

- X-Pessimism: 悲观模型,在gate-level仿真中,如果逻辑的输入中包含了X,那么输出结果会被解析为X,哪怕结果是确定的。

举个离子:

if(sel) out= a; else out = b;

真值表:

| sel | a | b | out(Verlog) | out (乐观) | out(悲观) |

|---|---|---|---|---|---|

| x | 0 | 0 | 0 | 0 | x |

| x | 0 | 1 | 1 | x | x |

| x | 1 | 0 | 0 | x | x |

| x | 1 | 1 | 1 | 1 | x |

可以看到真值表中,当a != b时 X-Optimism 会将仿真变为X态,而在X-Pessimism中所有的结果都为X态,哪怕结果是固定。

在Cadence工具中引入了2个对应的mode, 非常形象的

FOX mode --> Focus only X

CAT mode --> Compute as Ternary

VCS也有同样的对应,

| X-mode | Cadence | VCS |

|---|---|---|

| Verilog行为 | Deafult | vmerge |

| X-Optimism | CAT | tmerge |

| X-Pessimism | FOX | xmerge |

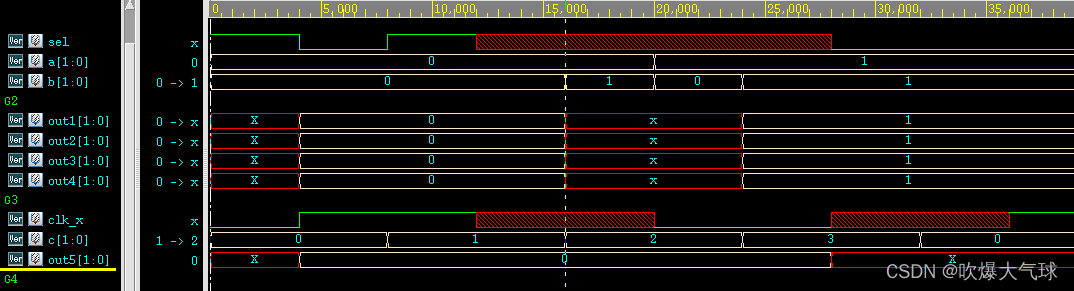

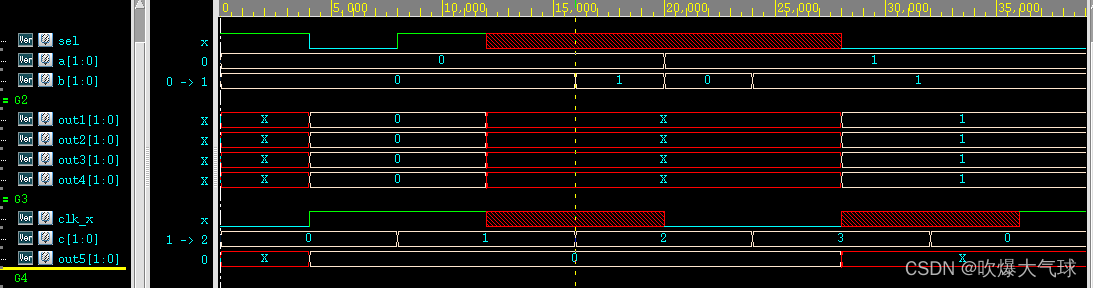

直接看不同的XPROP下对应的不同波形

Cat mode下

FOX mode下

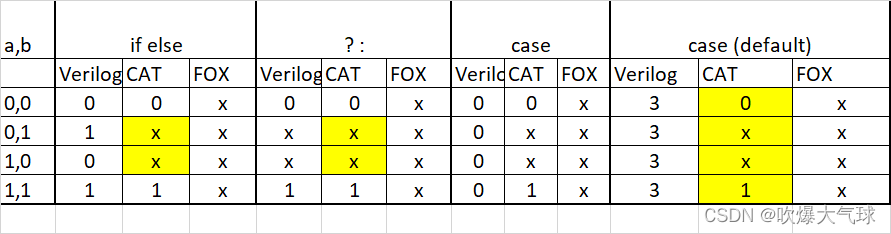

对比三种模式下的真值表

可以看到FOX模式下所有的输出值由于X态参与了逻辑,而全部输出了X态。而CAT模式下,只有在输出结果不确定的情况下才会输出X态。

数组的扩展

另外对于XPROP,除了逻辑上的X态扩散检查,对于数组的index越界的检查也是非常有效的。

考虑以下的场景:

一个深度为6‘d50的数组,期望读index=6’d20, 如果硬件电路设计错误的读了index=6’d60,那么rdata会被返回X态,但如果写了index=’d60的。那么写操作则不会生效,默认情况下将不会有任何行为,再次读index=6‘h20时,将会读到上次的值,如果不作回读,那么这个问题将会被漏掉。

XPROP支持:

- 如果写数组的index中包含X,Z,或者越界,工具将所有数组的值全部改写为X值。

- 读操作的index中包含X,Z,或者越界,工具不会改变行为,依然是X态,但数组的值不会被改写。

==Xcelium中需要定义额外的参数来打开这部分检查,而不是-xprop F/C就可以 ==

注意事项

XPROP在前仿的作用是便于验证工程师在更早的阶段找到bug,将原本只能在gate-level才会发现的问题提前到rtl仿真,更早的释放风险。但这并不表示使能XPROP后发现的行为都是bug,因为有些电路设计做了保护,尤其某些第三方IP,需要验证和设计工程师一起去定位,确认。

对于确认后不是问题的电路设计,可以使用 XRPOP自带的脚本功能来控制XPROP的范围,可以对不同的模块施加不同的XPROP 模式

本文探讨了Verilog中的X态概念,它如何在RTL电路仿真中出现并可能引发问题。着重介绍了X-Optimism和X-Pessimism两种X态模型,以及Cadence工具中的不同X-mode。文章还讨论了XPROP工具在检测X态扩散和数组越界中的作用,以及在电路设计验证中的重要性。

本文探讨了Verilog中的X态概念,它如何在RTL电路仿真中出现并可能引发问题。着重介绍了X-Optimism和X-Pessimism两种X态模型,以及Cadence工具中的不同X-mode。文章还讨论了XPROP工具在检测X态扩散和数组越界中的作用,以及在电路设计验证中的重要性。

4911

4911

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?