FPGA系列文章目录

二、FPGA学习笔记(二)Verilog语法初步学习(语法篇1)

四、FPGA学习笔记(四)通过数码管学习顶层模块和例化的编写

五、FPGA学习笔记(五)Testbench(测试平台)文件编写进行Modelsim仿真

六、FPGA学习笔记(六)Modelsim单独仿真和Quartus联合仿真

七、FPGA学习笔记(七)verilog的深入学习之任务与函数(语法篇3)

语法篇系列目录

FPGA学习笔记(二)Verilog语法初步学习( 语法篇1)

FPGA数字电子技术复习笔记(一)verilog语法规则补充(语法篇2)

FPGA学习笔记(七)verilog的深入学习之任务与函数(语法篇3)

重要声明

作为HDL语言,有两种基本的用途:系统仿真和设计实现。所有的HDL描述都可用于仿真,但并非所有的HDL描述都可综合。

参考:FPGA学习笔记—Verilog HDL 可综合语句和不可综合语句汇总

目录

Verilog简介

在FPGA设计里面,我们有多种设计方式,如原理图设计方式、编写描述语言〈代码〉等方式。一开始很多工程师对原理图设计方式很钟爱,这种输入方式能够很直观的看到电路结构并快速理解,但是随着电路设计规模的不断增加,逻辑电路设计也越来越复杂,这种设计方式已经越来越不满足实际的项目需求了.这个时候Verilog 语言就取而代之了,目前Verilog已经在FPGA开发/IC设计领域占据绝对的领导地位。

Verilog基础知识

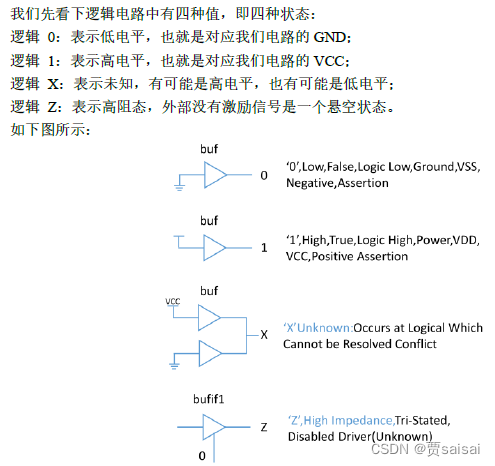

逻辑电路值

标识符

标识符(identifier)用于定义模块名、端口名和信号名等。Verilog 的标识符可以是任意一组字母、数字、$和_(下划线)符号的组合,但标识符的第一个字符必须是字母或者下划线。另外,标识符是区分大小写的。

不建议大小写混合使用,普通内部信号建议全部小写,参数定义建议大写,另外信号命名最好体现信号的含义。

订阅专栏 解锁全文

订阅专栏 解锁全文

2145

2145

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?