MCU配置(一) 时钟与晶振

1.时钟是什么,为什么需要时钟?

时钟对于CPU来说就等同于心脏,时钟频率的高低决定了CPU执行指令的速度,同时对于大多数外设来说也是需要一个时钟信号才能正常工作的,以通信相关的模块来说,一个信号本质上是高低电平的组合,比如我们要发送数据‘1’,且在我们规定的编码格式中‘1’定义为‘0000 0001’,那么我们在表示这个数据时,前7个周期电平都置低,第8个周期电平置高,就正确表达了‘1’,我们的时钟频率越高,就能越‘快’的表达这个数据。

2.什么是晶振?

直白点说晶振就是产生时钟的物理单元,通常来说晶振主要分为以下几类:

内部快速晶振;

内部慢速晶振;

外部快速晶振;

外部慢速晶振;

一般来说内部晶振的稳定性和精度都不是很高,如果对时钟要求比较低可以考虑使用内部晶振,省钱的同时减少主芯片pin脚消耗,时钟要求比较高选择外部晶振,车规级芯片基本上都会选择外部晶振。

3.如何获取高频率的时钟?

外部晶振的标称频率一般为32768hz、8mhz、12mhz、24mhz、125mhz等,CPU和外设要求的时钟都高于这个这个频率,要想得到更高频率的时钟,需要使用锁相环(PLL)进行倍频,再使用分频,给到各个模块,因此外部晶振和倍频系数、分频系数是需要精心设计的,因为分频系数和倍频系数都是取整。

时钟树

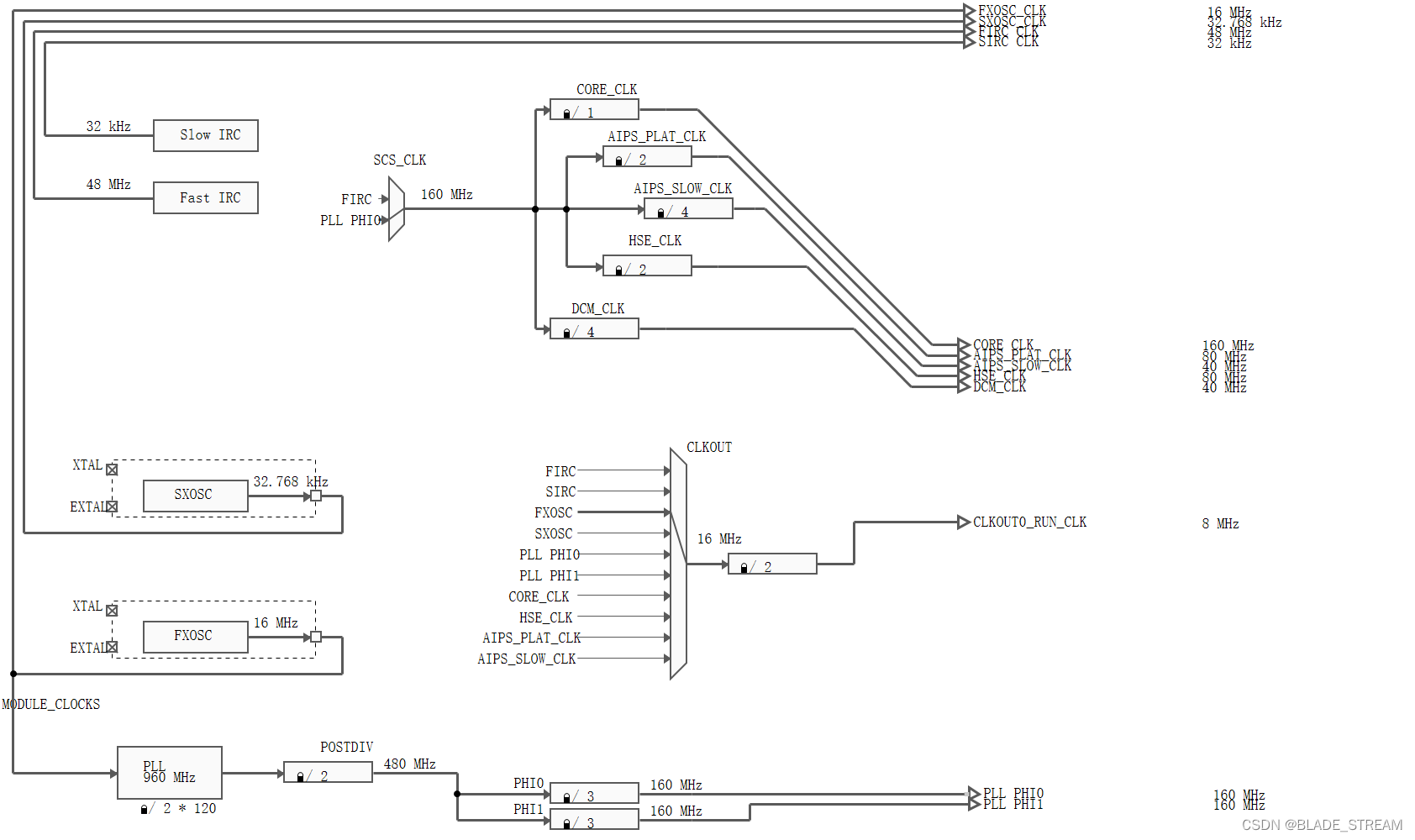

S32K3系列的时钟树可在S32DS的工程中打开,在屏幕右上角点击clock可以打开时钟树

能否看懂时钟树决定了时钟配置的正确性,其中时钟树上部分主要为内外部时钟选择,锁相环配置,下半部分为各个模块的时钟分配与配置

以官方例程来说,我们的SCS_CLK有两路选择源,锁相环输出时钟和内部快速时钟,之前说过内部时钟稳定性和精度都比较差,因此选择PLL输出时钟。

PLL的时钟源选择外部快速时钟,即FXOSC,例程的外部快速时钟为16Mhz,在具体项目配置时,需要根据项目实际进行配置。

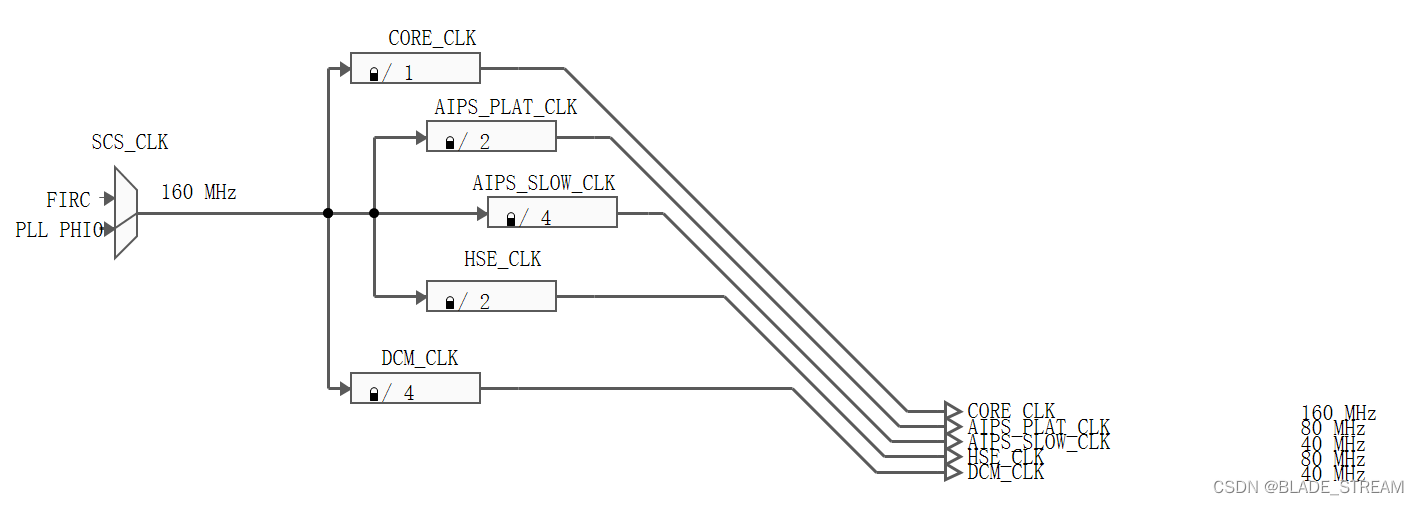

PLL经过一系列的倍频与分频后输出160Mhz的PLL_PHI0,这一路信号再经过分频后输出到下列时钟信号:

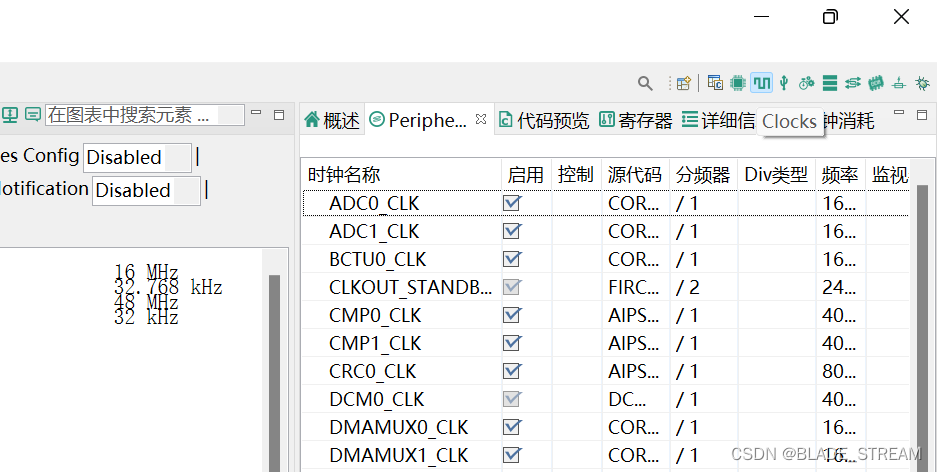

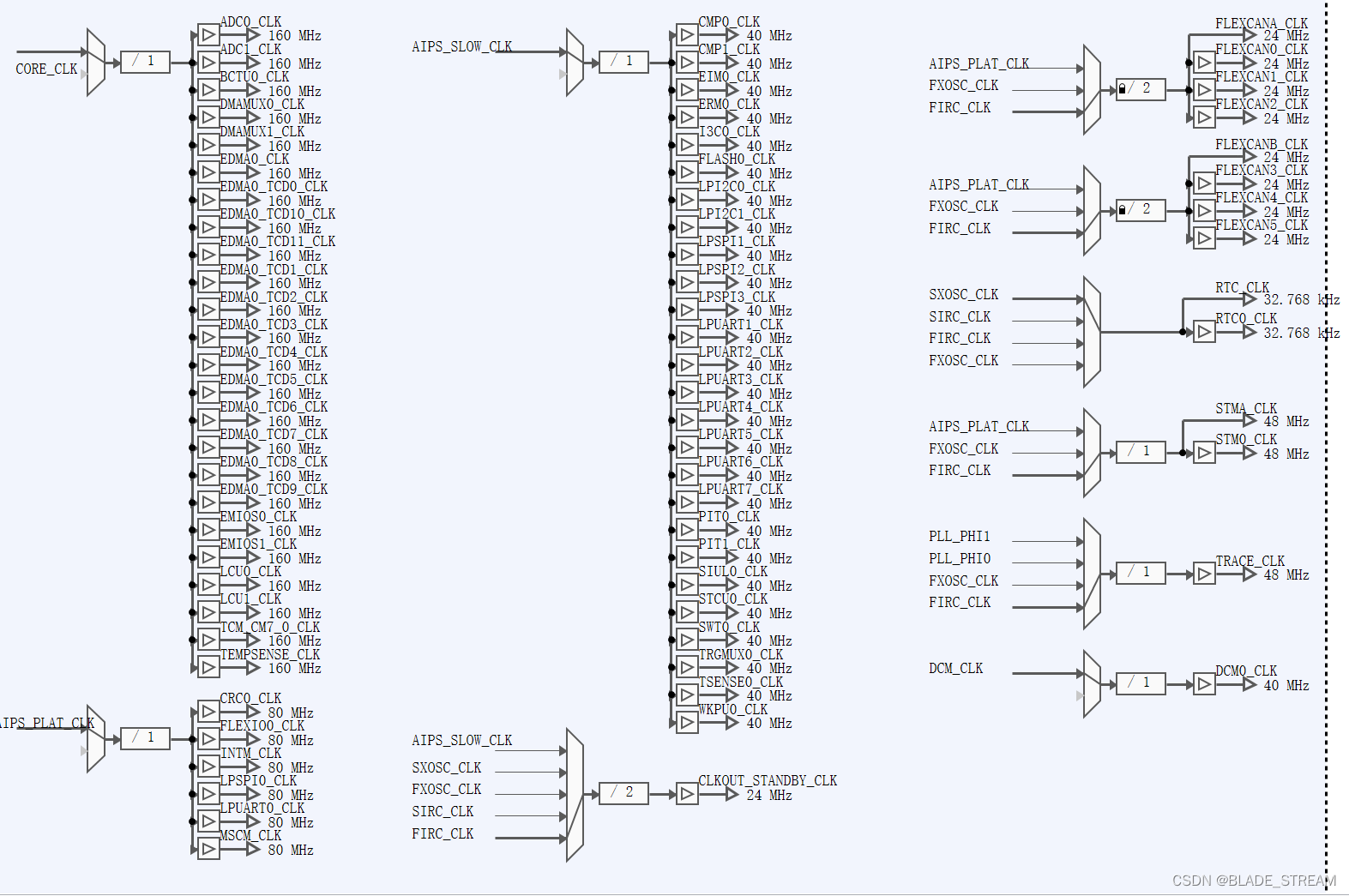

这些时钟再输出到各个模块或具体外设上,也就是下部分的内容:

时钟对于CPU执行速度至关重要,晶振是产生时钟的物理单元,有内部和外部之分。通过锁相环(PLL)可以将低频晶振转换为高频时钟。S32K3系列的时钟树展示了时钟配置的结构,包括时钟源选择、锁相环配置及各模块时钟分配。项目配置应根据实际需求选择合适的时钟源和频率。

时钟对于CPU执行速度至关重要,晶振是产生时钟的物理单元,有内部和外部之分。通过锁相环(PLL)可以将低频晶振转换为高频时钟。S32K3系列的时钟树展示了时钟配置的结构,包括时钟源选择、锁相环配置及各模块时钟分配。项目配置应根据实际需求选择合适的时钟源和频率。

1459

1459

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?