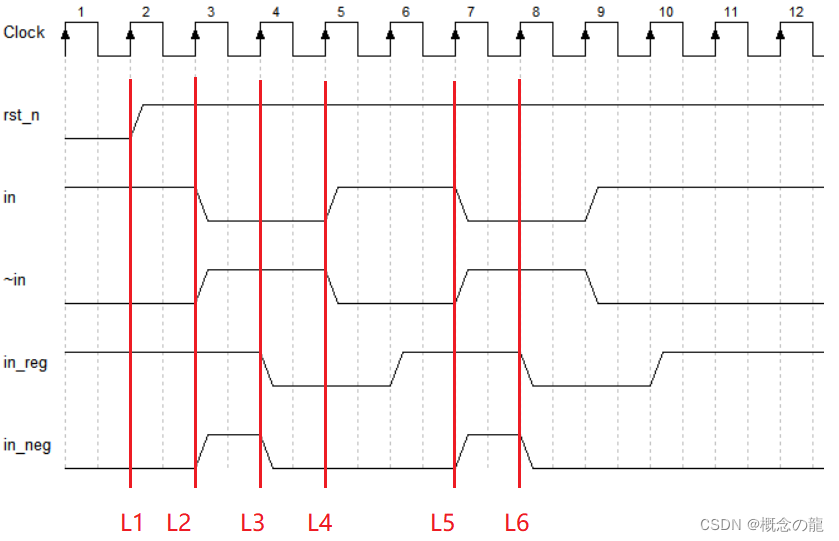

clk :系统时钟信号

rst_n :复位信号

in :输入信号

~in :输入信号的反相信号

in_reg :对输入信号寄存一拍

in_neg :得到的下降沿指示信号,该信号为 in_reg && ~in

信号in是需要对其进行边沿检测的信号

信号~in是对信号in取反

信号in_reg是使用寄存器寄存in信号,即对其进行打拍,或者说是同步到系统时钟域下

输入信号开始为高电平,在L2处变为低电平,产生第1个下降沿,在L5出产生第2个下降沿

L1-L2为产生的第1个下降沿指示信号,L4-L5为产生的第2个下降沿指示信号

推导出边沿检测信号产生的一般方法:

将需要检测的信号寄存一拍,同步到系统时钟域下,得到信号 in_reg

将需要检测的信号反向,得到信号 ~in

将信号 in_reg 反向,得到信号 ~in_reg

通过组合逻辑电路可以得到下降沿信号 in_neg:assign in_neg = ~in && in_reg

同样通过组合逻辑电路可以得到上升沿信号 in_pos:assign in_pos = in && ~in_reg

双边沿检测就是将上两条加(或运算)起来就可以了,化简后有:双边沿信号 in_dou = in ^ in_reg

Verilog代码

`timescale 1ns / 1ps

module test(

input wire clk ,

input wire rst_n ,

input wire in , // 输入信号

output wire in_neg , // 下边沿信号

output wire in_pos , // 上边沿信号

output wire in_dou // 双边沿信号

);

reg in_reg; // in寄存一拍

always@(posedge clk)

if(!rst_n)

in_reg <= 0;

else

in_reg <= in;

assign in_neg = ~in && in_reg;

assign in_pos = in && ~in_reg;

assign in_dou = in ^ in_reg;

endmodule

Testbench文件

`timescale 1ns / 1ps

module tb();

reg clk ;

reg rst_n ;

reg in ;

wire in_neg ;

wire in_pos ;

wire in_dou ;

initial begin

clk = 0;

rst_n = 0;

in = 0;

#100

rst_n = 1;

#20

in = 1;

#100

in = 0;

#40

in = 1;

#100

in = 0;

end

always #10 clk = ~clk;

test ts(

. clk (clk ),

. rst_n (rst_n ),

. in (in ),

. in_neg (in_neg),

. in_pos (in_pos),

. in_dou (in_dou)

);

endmodule

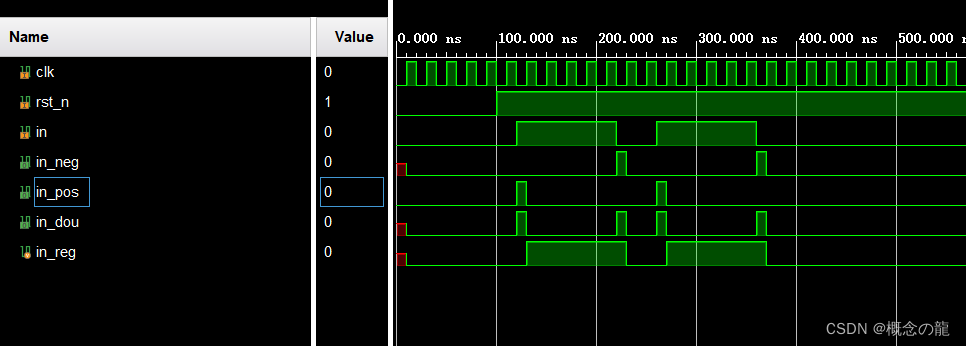

仿真结果

学习来源:

FPGA实现边沿检测电路(上升沿、下降沿)

1107

1107

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?