静态时序分析(STA)原理:STA是一种无需模拟电路实际操作的时序验证方法。它通过分析电路的时序路径来预测电路在不同条件下的性能。STA不考虑电路的输入向量,而是基于电路的最坏情况分析来确保时序要求得到满足。

优点:速度快,资源消耗少,全面性。缺点:过于保守。

动态时序分析(DTA)原理:DTA通过对电路进行实际的仿真来验证时序。它需要特定的输入向量和操作条件下的仿真,以检查电路在实际操作中是否满足时序要求。

优点:准确性,发现功能错误。缺点:速度慢,资源消耗大, 覆盖率问题。

添加时序约束的情况:常见的一些高速接口,比如千兆网、HDMI 接口、摄像头接口、USB 接口、LCD 接口等都应该添加一些基本的时序约束。

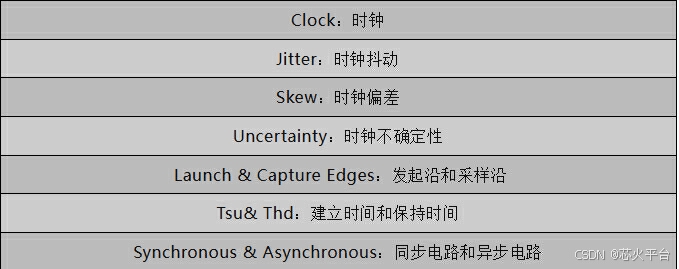

时序约束的基本概念

时序分析的基本公式

·数据到达时间(Data Arrival Time):数据在发送沿发送之后,经过长时间会到达接收寄存器的数据端口,即到达regb的D 端口的时刻,这个时刻就是数据到达时间。需要选择一个参考(基准)时间点。通常选择launch edge 作为零时刻基准点。

数据经过Tco时间,到达Q 端口。数据从Q 端口,要经过组合逻辑,以及布线的线延时才能到达接收短的D 端口的(Tdata)。

公式:数据到达时间Data Arrival Time = 发起沿时间LaunchEdge Time + Tclka+Tco+ Tdata

·时钟到达时间(clock Arrival Time):观察采样寄存器的时钟,选择 launch edge 作为零时刻基准点。其实是launch edge 加上一个时钟周期就是采样沿时间。

公式:时钟到达时间Clock Arrival Time =采样沿时间CaptureEdge Time +Tclkb

·数据建立需要时间(Data Setup Required Time):在regb的时钟到达时间的基础 上,为了避免regb出现亚稳态,需要让其数据保持一段时间。这一段时间为数据需要时间。为了保证建立时间,数据需要在regb采样时钟到来之前到来。

公式:数据建立需要时间Data Setup Required Time = Clock Arrival Time -Tsu

·数据保持需要时间(Data Hold Required Time):为了保证保持时间,数据regb 采样时钟到来之后保持一段时间。

公式:数据保持需要时间Data Hold Required Time = Clock Arrival Time + Th

·Setup Time Slack:建立时间裕量(当前数据到来时间)

公式:Setup Time Slack = Data Setup Required Time -Data Arrival Time

·HoldTime Slack:保持时间裕量(下一个数据到来时间)

公式:Hold Time Slack = Next Data Arrival Time -Data Hold Required Time

323

323

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?