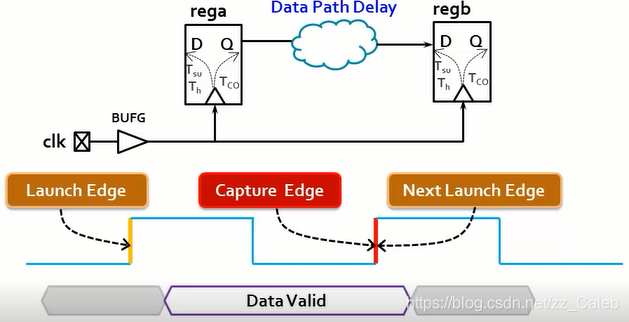

- 发起沿和捕获沿(Launch edge & Capture edge)

- Launch edge是发送数据的时钟边沿,通常选择上升沿。

- Capture edge是捕获段捕获到该数据的时钟边沿。

- 通常情况下这两个边沿会有一个时钟周期的差别。

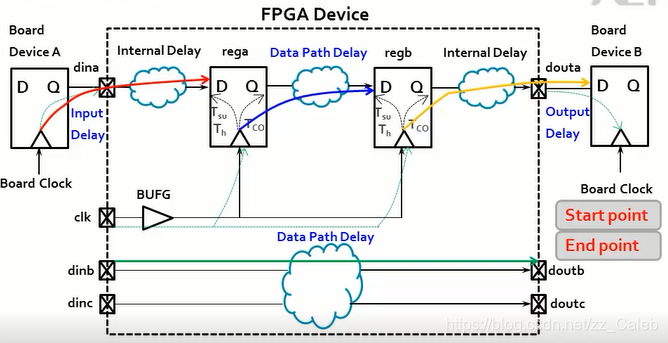

- 时序路径(Timing path典型时序路径有四种)

- 第一类时序路径(红色)

- 从device A的时钟到FPGA的第一级寄存器的输入端口。

- 第二类时序路径

- 两个同步元件之间的路径(rega到regb蓝色)

- 第三类时序路径

- 最后一集寄存器到device B数据端口的路径(黄色)

- 第四类时序路径

- 端口到端口的路径(dinb到dinb绿色)

- 我们要关注的是这些路径的

- 起始点(start point)记作S

- 终止点(end point)记作E

时序分析的基本概念和术语

最新推荐文章于 2023-04-13 15:37:16 发布

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?